High speed ADC interweaved sampling system

A sampling system, high-speed technology, applied in the direction of physical parameter compensation/prevention, analog-to-digital converters, electrical components, etc., can solve the problem of system SNR reduction of spurious-free dynamic range, ADC channel harmonic distortion, and unfavorable overall system performance and other issues, to achieve the effect of reducing phase error, improving overall performance, and fast transmission rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

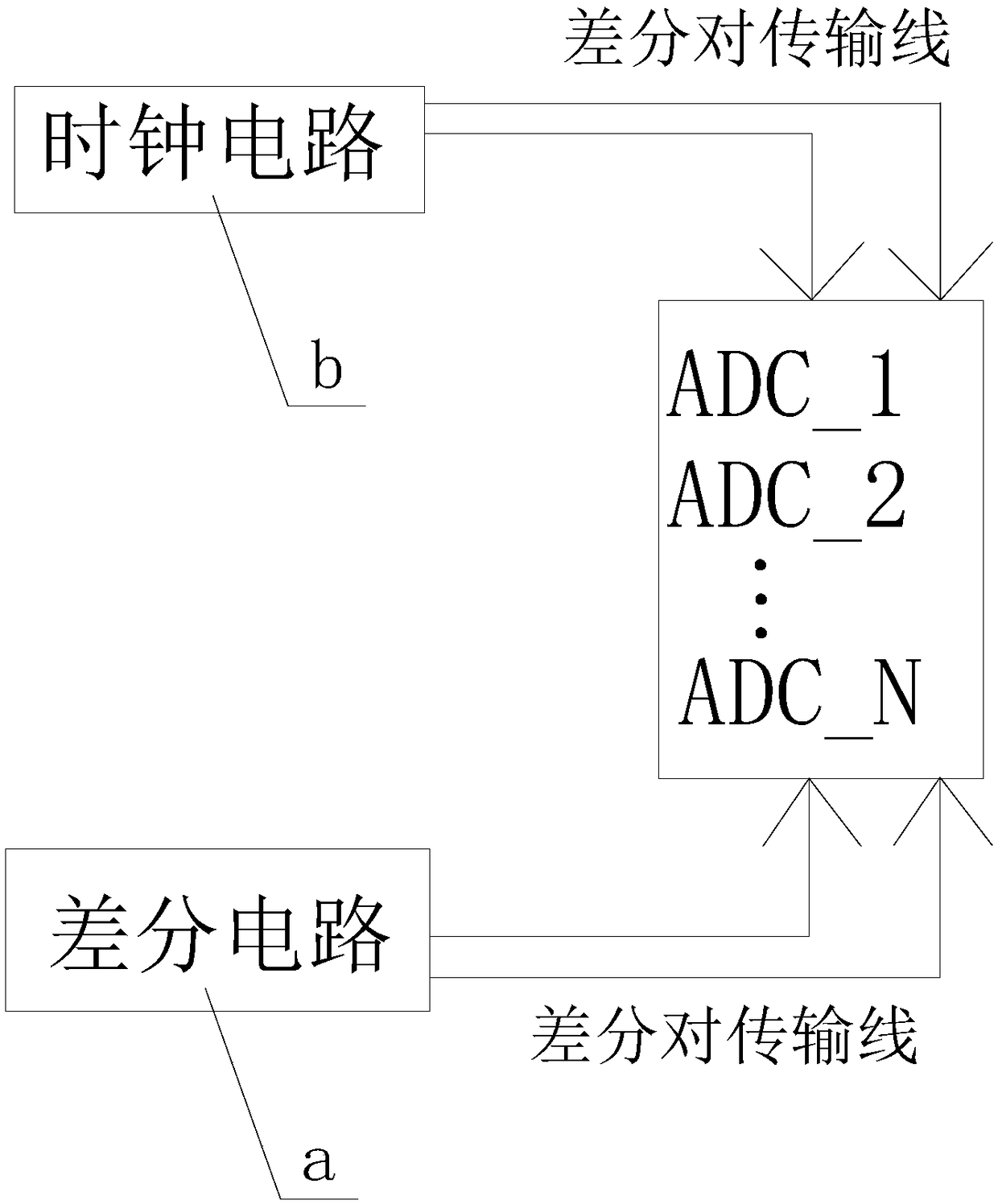

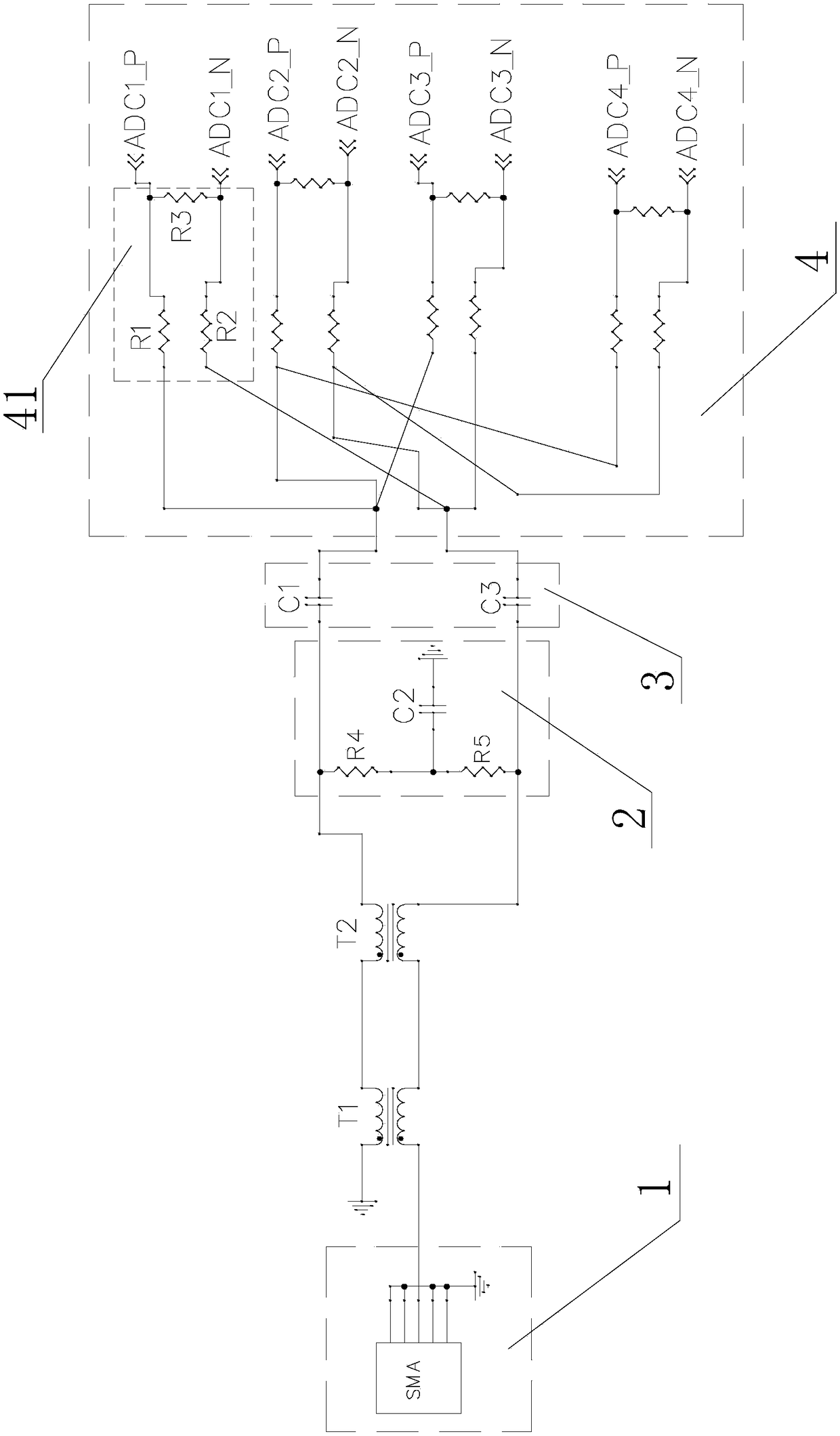

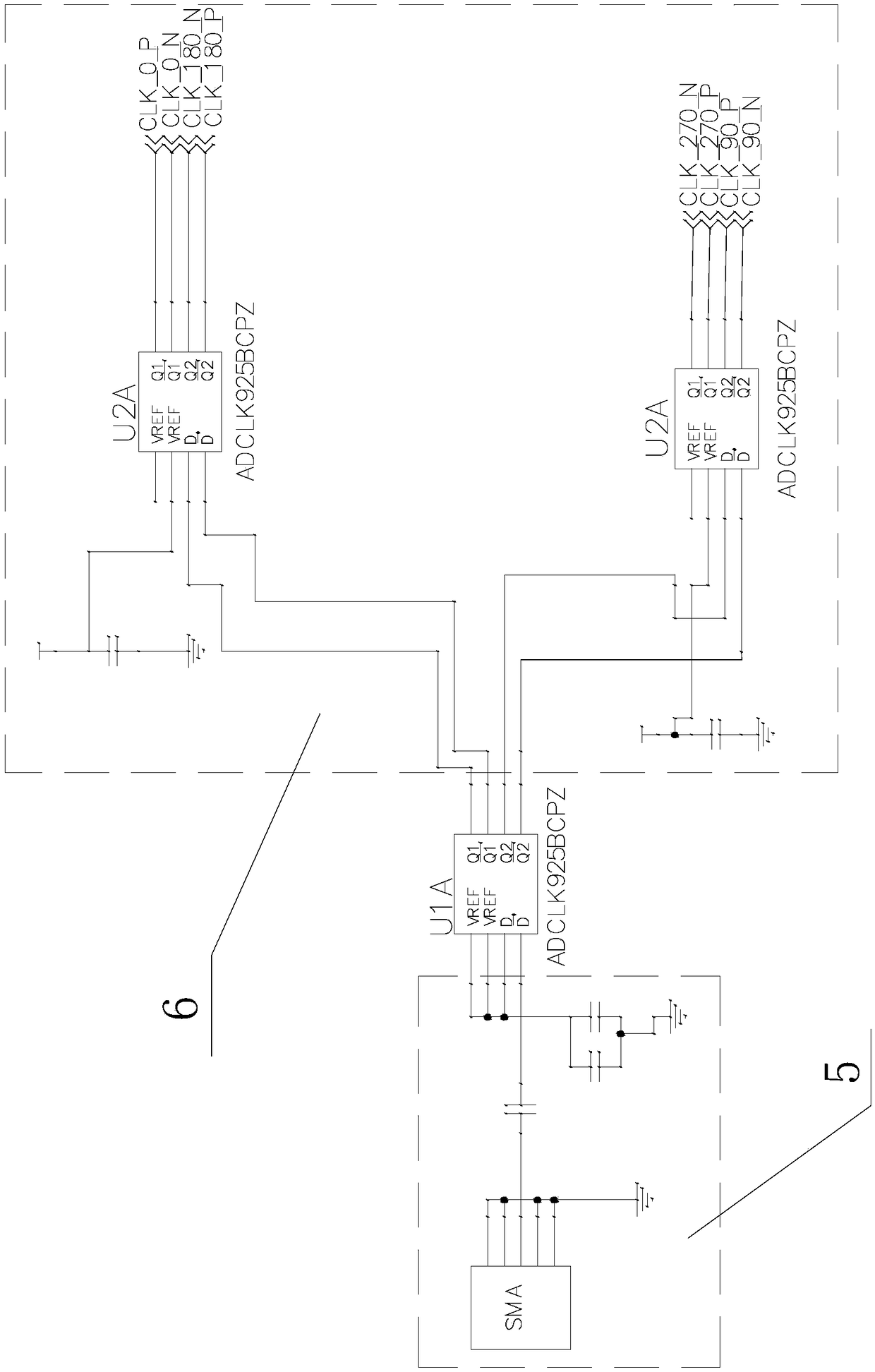

[0018] refer to Figure 1-Figure 3 , a high-speed ADC interleaving sampling system of the present invention, comprising a differential circuit a and a clock circuit b, the differential circuit a and the clock circuit b are respectively connected to the ADC of N channels through a differential pair transmission line; the differential circuit a includes sequentially cascaded first Transformer T1 and the second transformer T2, and the signal output module 4 for respectively inputting the differential pair signal to the ADC of the N channel, the input end of the signal output module 4 is connected to the output end of the second transformer T2; the clock circuit b includes To the ADC of the N channel, respectively input the post-stage clock module 6 of the differential pair clock signal, and the first clock chip U1A for inputting the differential pair signal with a phase difference to the post-stage clock module 6; the post-stage clock module 6 includes N / Two second clock chips U...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More