Three-dimensional integrated cooling gain-type semiconductor assembly and fabrication method thereof

A semiconductor, gain-type technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of low production qualification rate, complex process, high cost, etc., and achieve the effect of reliable connection channels

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

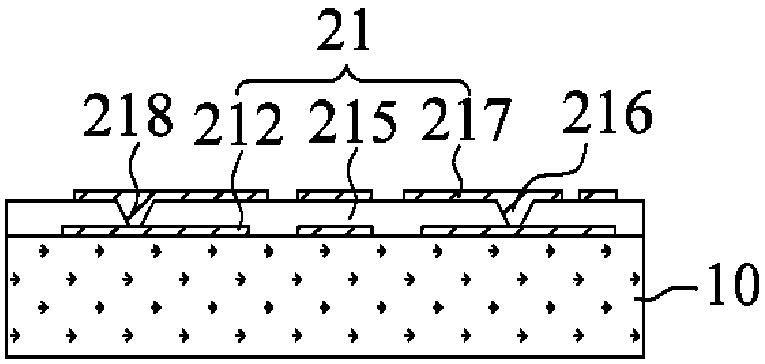

[0088] Figure 1-13 It is a diagram of a manufacturing method of a semiconductor component in the first embodiment of the present invention, which includes a first routing circuit 21, a first device 22, a molding material 25, a second device 27, a heat sink 30 and Bonding wires 41,43.

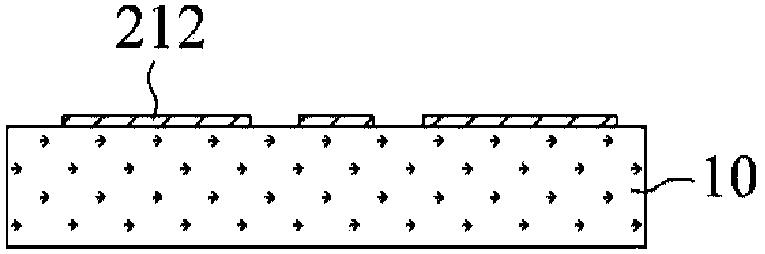

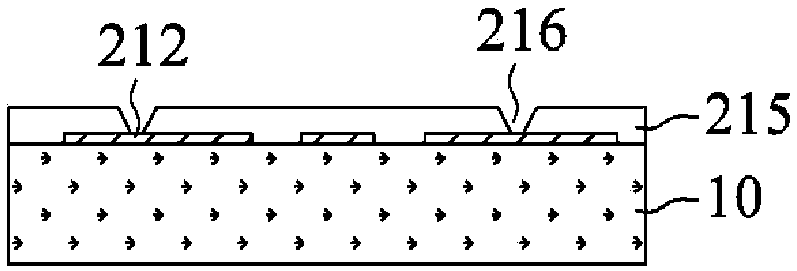

[0089] figure 1 It is a cross-sectional view of the routing lines 212 formed on the sacrificial carrier 10 . The sacrificial carrier 10 is typically made of copper, aluminum, iron, nickel, tin, stainless steel, silicon or other metals or alloys, but any other conductive or non-conductive material could also be used. In this embodiment, the sacrificial carrier 10 is made of ferrous material. Routing lines 212 are usually made of copper and can be patterned and deposited by various techniques, such as electroplating, electroless plating, evaporation, sputtering or a combination thereof, or formed by thin film deposition followed by a metal patterning step. As far as the conductive sacrificial...

Embodiment 2

[0114] Figure 18-20 In the second embodiment of the present invention, it is a diagram of a manufacturing method of a semiconductor device in which a second routing circuit is electrically coupled to a metal post.

[0115] For the purpose of brief description, any statements in the above-mentioned embodiment 1 that can be used for the same application are incorporated here, and there is no need to repeat the same statements.

[0116] Figure 18 It is a sectional view of the heat sink 30 . The heat sink 30 with Figure 11 The structures shown are similar, but the difference is that the second routing circuit 33 further includes a build-up insulating layer 361 and a fourth wire 364, wherein the build-up insulating layer 361 is laminated / coated on the routing substrate 351 and the metal pillars 323, 324 , and the fourth wire 364 is deposited on the build-up insulating layer 361 . The build-up insulating layer 361 contacts the routing substrate 351 and the metal pillars 323 ,...

Embodiment 3

[0125] Figure 24-27 It is a diagram of another method of manufacturing a semiconductor component in the third embodiment of the present invention, the metal plate has a through hole, and the through hole is aligned with the through opening of the second routing circuit.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More