Vertical pHEMT transistor structure and switch chip

A transistor and isolation layer technology, applied in semiconductor devices, electric solid state devices, semiconductor/solid state device components, etc., can solve the problem of low isolation, and achieve the effect of short interconnection distance, high integration and strong control ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

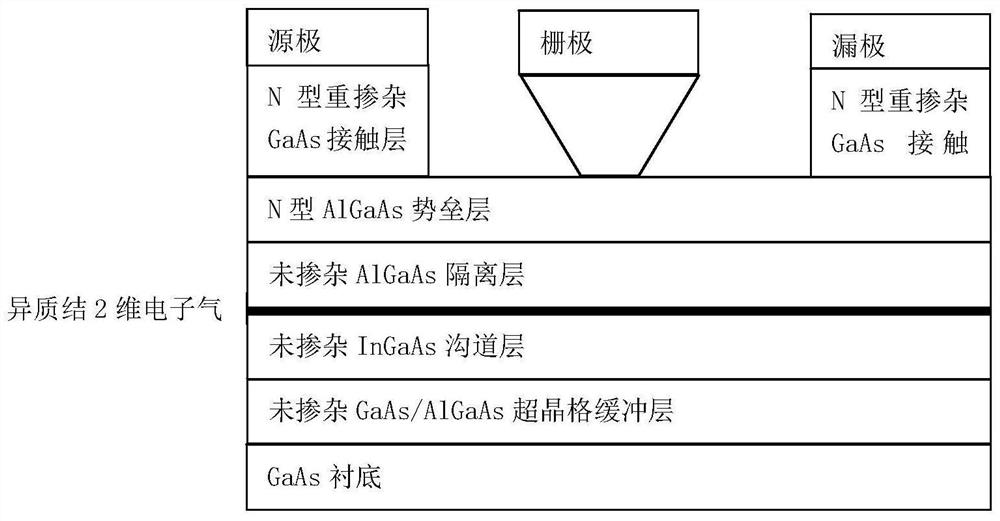

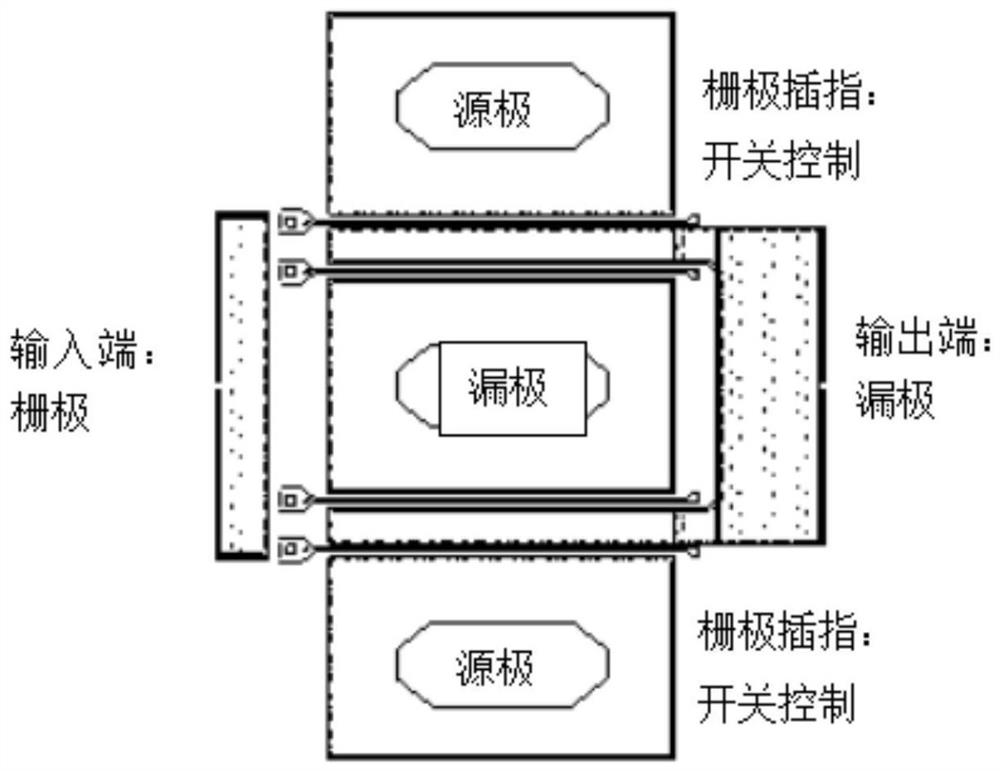

[0046] This embodiment discloses a vertical pHEMT microwave transistor structure, the transistor structure includes:

[0047] Around the metallized through hole, an undoped GaAs / AlGaAs superlattice buffer layer, an undoped InGaAs channel layer, an undoped AlGaAs isolation layer and an N-type AlGaAs barrier layer are sequentially arranged from the inner layer to the outer layer, The axial direction of the metallized through hole is the same as the normal direction of the substrate; the source, gate, and drain are set on the side wall of the N-type AlGaAs barrier layer, and the source and drain are set on the side wall of the N-type AlGaAs barrier layer. The GaAs contact layer is heavily doped such that the 2D electron gas is distributed axially around the metallized via. The metallized through hole forms a columnar structure along the normal direction of the substrate. Correspondingly, each layer structure around the metallized through hole also forms a columnar structure, and ...

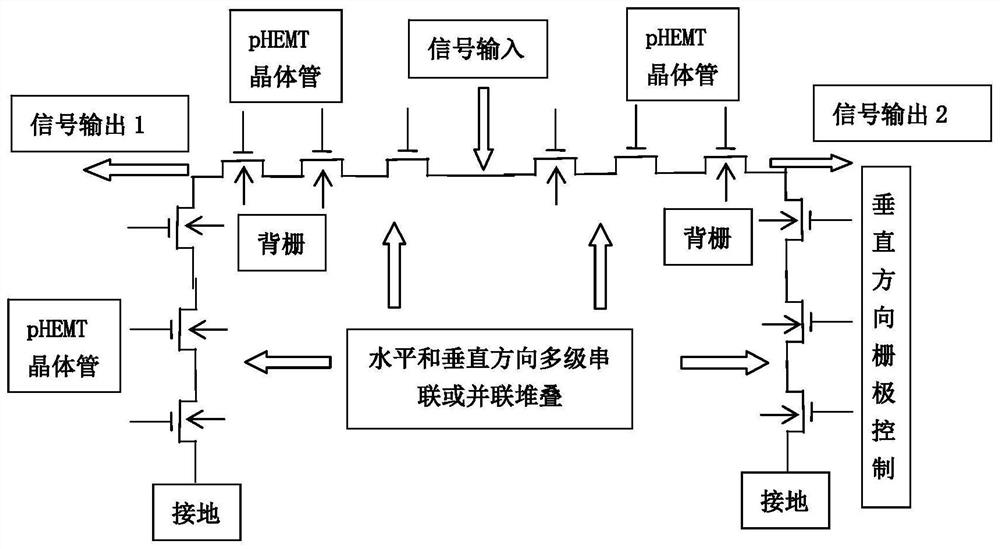

Embodiment 3

[0049] This embodiment discloses a vertical stacking structure of pHEMT transistors, which is formed by vertically stacking the vertical pHEMT microwave transistor structures in the above-mentioned embodiments on the substrate, and each adjacent two layers of vertical pHEMT microwave transistors include an upper layer transistor and a lower layer Transistors, upper layer transistors and lower layer transistors are vertically stacked (that is, stacked along the normal direction of the substrate), a second isolation layer is provided between the upper layer transistors and the lower layer transistors, and metallized vias for conduction and heat conduction are provided vertically through the second isolation layer . The structure of the upper layer transistor and the lower layer transistor adopts the above-mentioned pHEMT microwave transistor structure respectively. It should be noted that although the vertical pHEMT microwave transistor structure of the above-mentioned embodiment...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More