A cmp simulation method and simulation system for multilayer interconnect structure

A technology of multilayer interconnection and simulation method, which is applied in the field of chemical mechanical polishing, can solve the difficulty of process control, the increase of factors affecting the surface morphology of multilayer interconnection structure, and the inability to reflect the middle layer of multilayer interconnection structure. Interaction with layers and other issues to achieve the effect of eliminating the stack effect, the simulation process is simple and fast, and the simulation results are accurate and credible

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

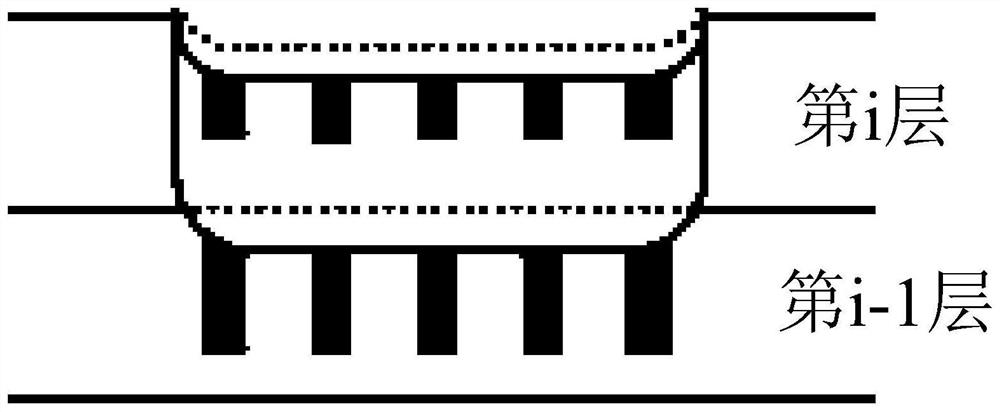

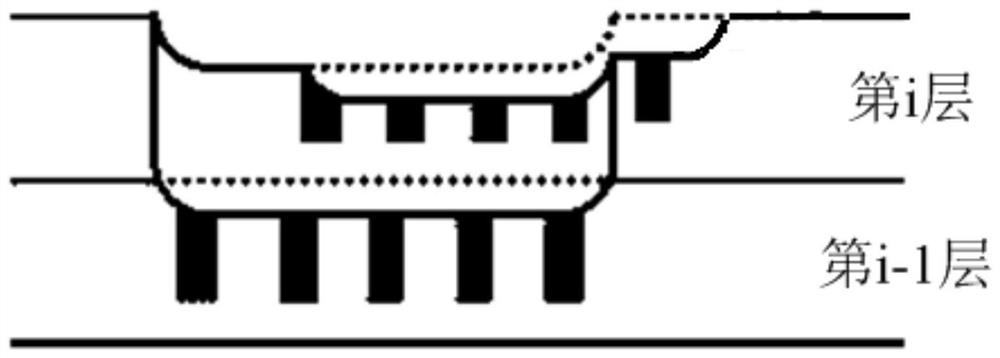

[0048] As mentioned in the background art, after forming the first layer of metal interconnection lines on the substrate and undergoing chemical mechanical polishing, the unevenness of the metal surface will remain. After forming the second layer of metal interconnection lines on this basis, due to The lower metal interconnection will affect the surface topography of the upper metal interconnection, therefore, it will increase the complexity of the CMP simulation of the upper metal interconnection.

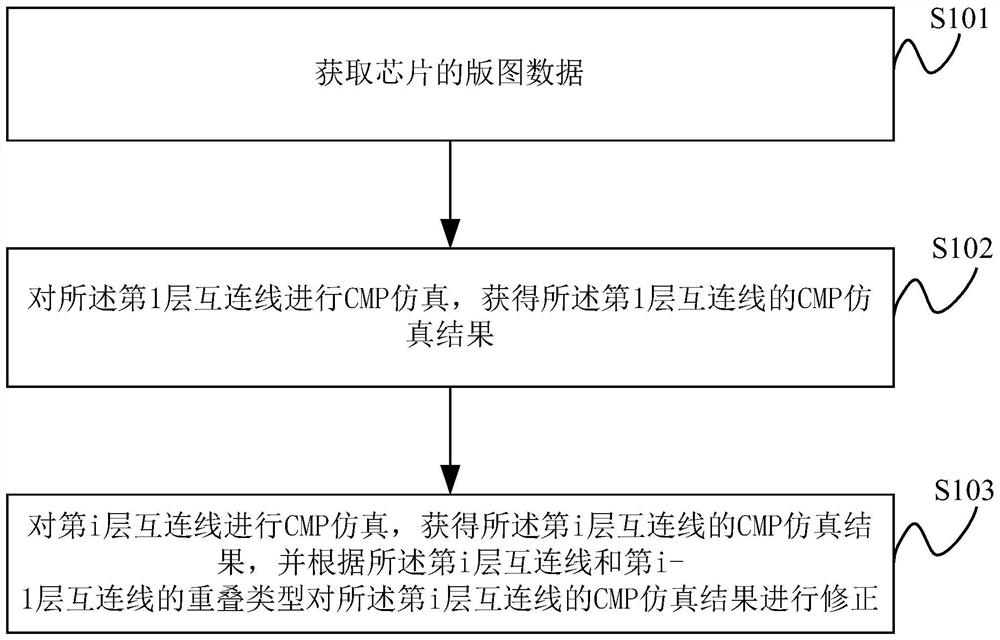

[0049] Based on this, the present invention provides a CMP simulation method of a multilayer interconnection structure to overcome the above-mentioned problems in the prior art, including:

[0050] Acquiring the layout data of the chip, the layout data including the surface topography data of the first layer interconnection line to the nth layer interconnection line arranged from bottom to top, n is an integer greater than or equal to 2;

[0051] Carrying out CMP simulation on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More