Self-correction method of multi-device data synchronization

A data synchronization and self-calibration technology, which is applied in analog/digital conversion calibration/testing, electrical components, analog/digital conversion, etc., can solve problems such as restricting the commercialization of high-speed acquisition systems, increasing system complexity, and having a greater impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

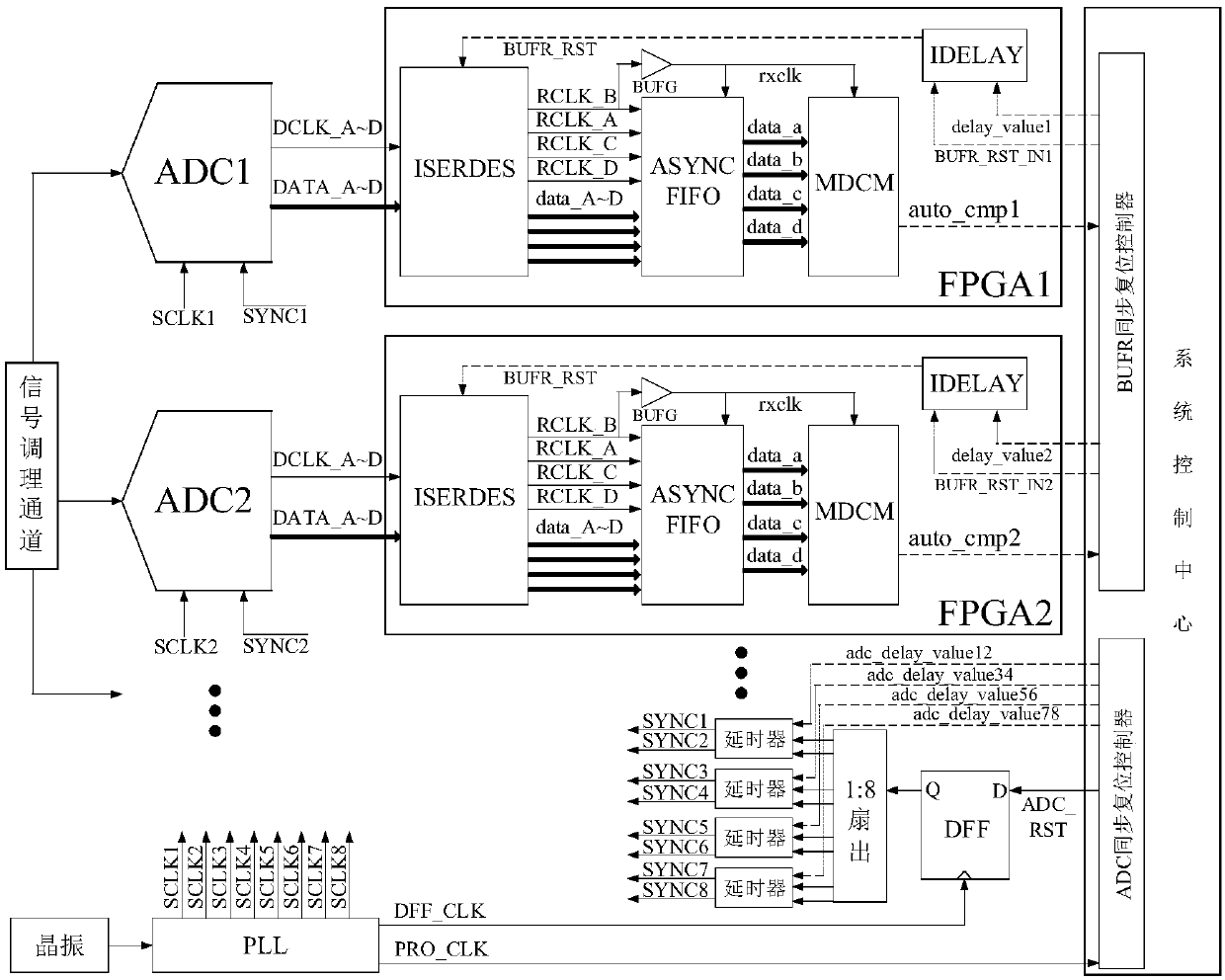

[0057] figure 2 It is a schematic diagram of a multi-device data synchronization self-calibration method of the present invention.

[0058] In this example, if figure 2 As shown, a self-calibration method for multi-device data synchronization of the present invention comprises the following steps:

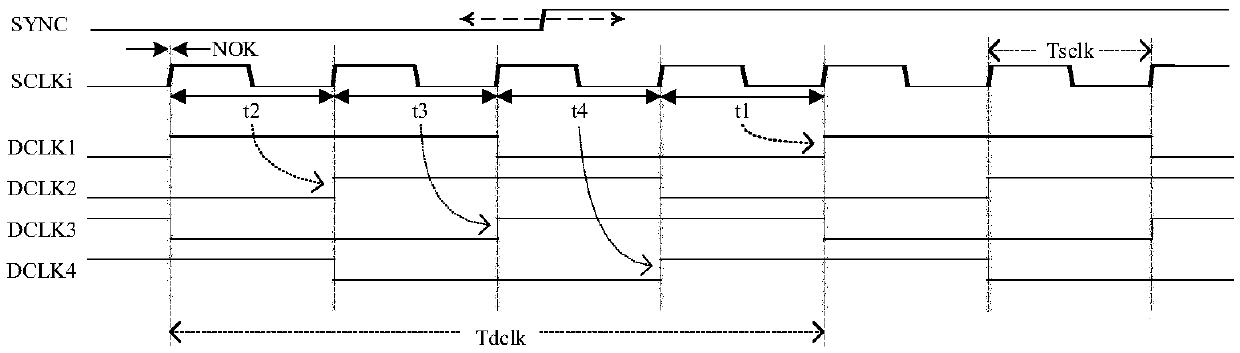

[0059] S1. Configure 8 high-speed multi-core ADC chips into test mode; configure the phase-locked loop to output 8 sampling clock signals SCLK with a frequency of 2.5GHz and a constant phase difference 1-8 To each multi-core ADC;

[0060] S2. The ADC synchronous reset controller sends the reset signal ADC_RST, which is sent to each delayer after fan-out at 1:8;

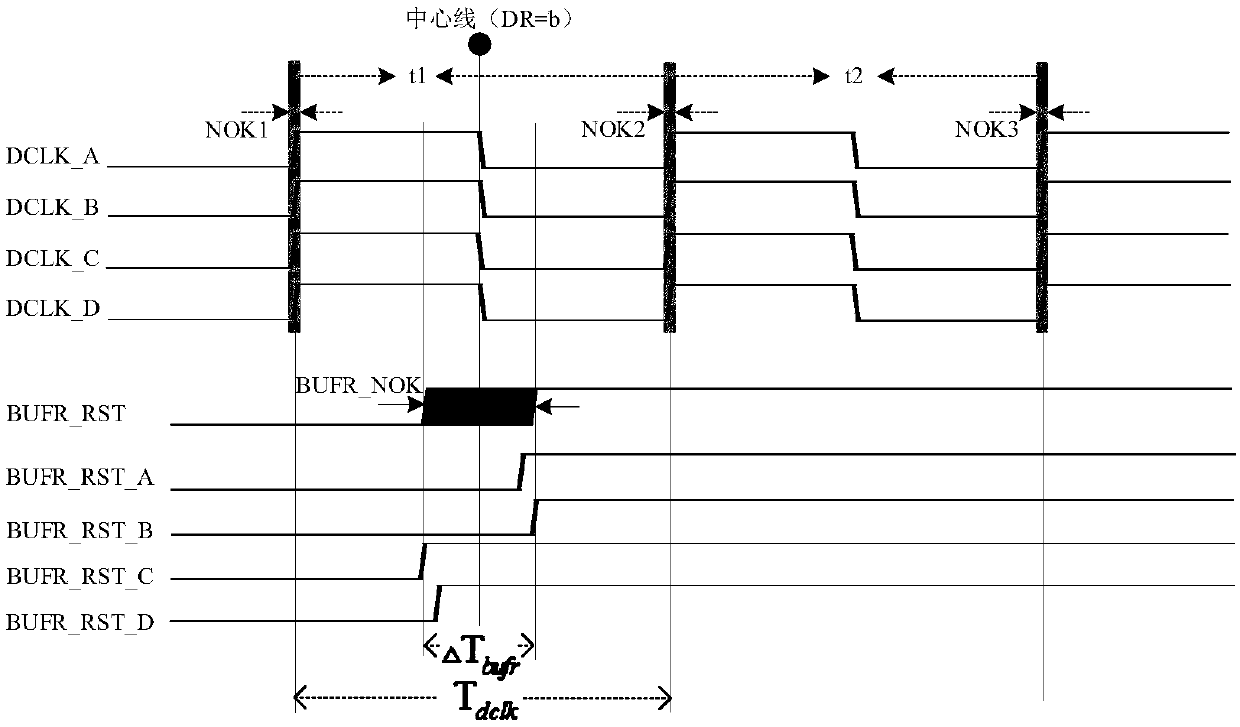

[0061] S3. Calculate the optimal delay value of multi-core ADC synchronous reset and the optimal delay value of BUFR synchronous reset

[0062] S3.1. Set the initial delay value of the input delay unit IDELAY to 0, the adjustment range of the delay value is 0 to 31, the adjustment step is 1, and the number of iterati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More