Hardware circuit implementation method for image matching descriptor generation scale space

A technology of scale space and hardware circuit, applied in computer parts, instruments, characters and pattern recognition, etc., can solve the problems of amazing calculation amount and low operation speed, save processing time, optimize performance, and reduce hardware resource occupancy rate Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] Such as figure 1 As shown, the present invention provides a hardware circuit implementation method for image matching descriptor generation scale space, including the following steps:

[0041] 1) In a specific application, load the image that needs to be matched, and the specific process is as follows:

[0042] 1.1) read the grayscale floating-point data of the image into DDR through Ethernet;

[0043] 1.2) Read the image data in the DDR into the Buffer sequentially in the order of row first and column second.

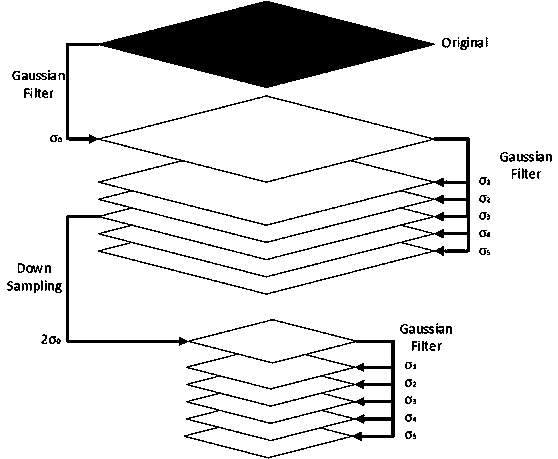

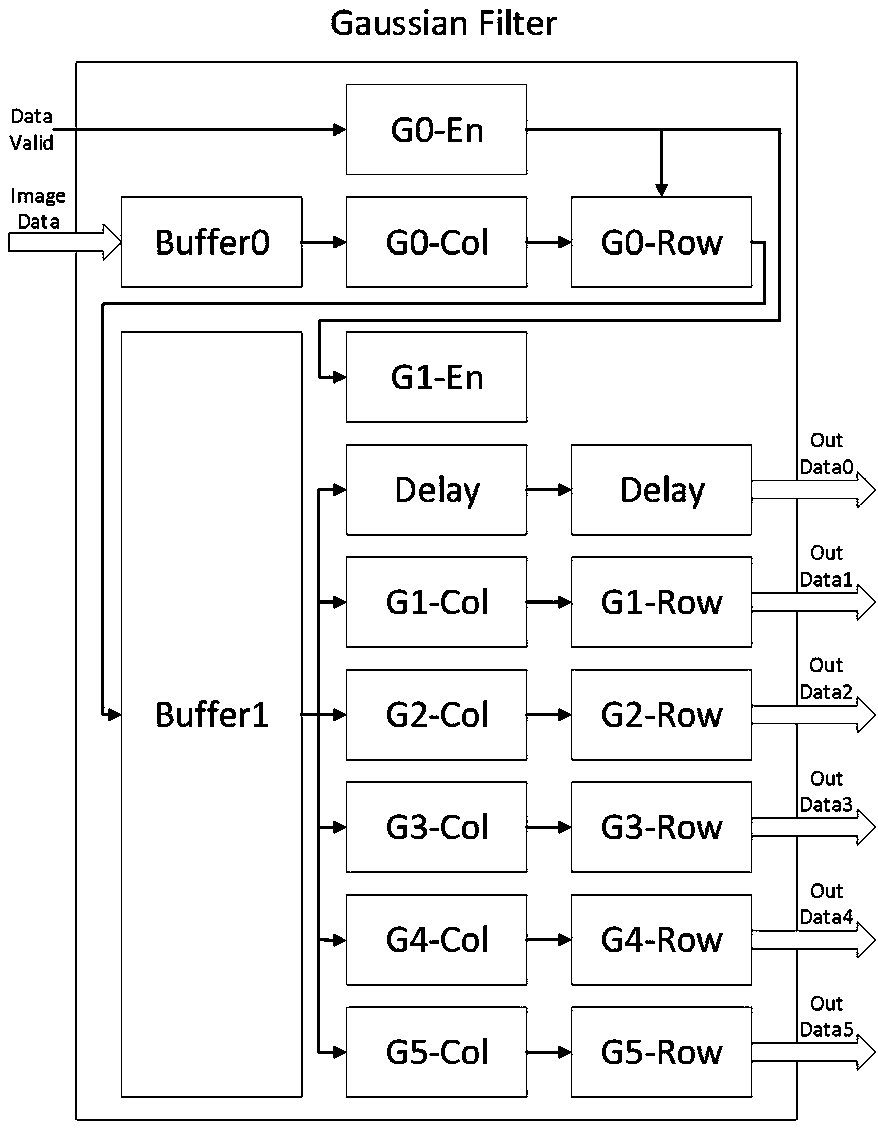

[0044] 2) Perform Gaussian smoothing on the image to generate the first group of images, the specific process is:

[0045] 2.1) Using the separability of the Gaussian function, split the two-dimensional Gaussian filter into the convolution of two one-dimensional Gaussian filters, and perform fixed-point processing on the one-dimensional filter template coefficients that need to be used, where the width of the Gaussian template is The size should be proportion...

Embodiment 2

[0079] The scale invariance test of this method is carried out below, and the specific test steps are as follows:

[0080] a) Scale space generation steps of optimizing the source image and the matching image respectively to obtain the respective image scale spaces, that is, the final Gaussian difference pyramid;

[0081] b) The two sets of Gaussian difference pyramids are respectively used to obtain the descriptors of the feature points by the classic SIFT method;

[0082] c) Perform Euclidean distance matching between the matching graph descriptor and the source graph descriptor. The method is: a descriptor whose nearest neighbor distance / second nearest neighbor distance is less than 0.6 is determined as a matching pair, and the number of matching pairs is counted and the time required to complete the matching time consumed.

[0083] By testing the scale invariance of two 640*512 image matching under different platforms and scale space generation methods, Table 1 and Table ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More