A successive approximation analog-to-digital converter and a low power switching algorithm thereof

An analog-to-digital converter, successive approximation technology, applied in the direction of analog/digital conversion, code conversion, instrument, etc., can solve the problems of power consumption and large occupied area, so as to simplify the design, save the chip area, reduce the switch Toggle the effect of energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

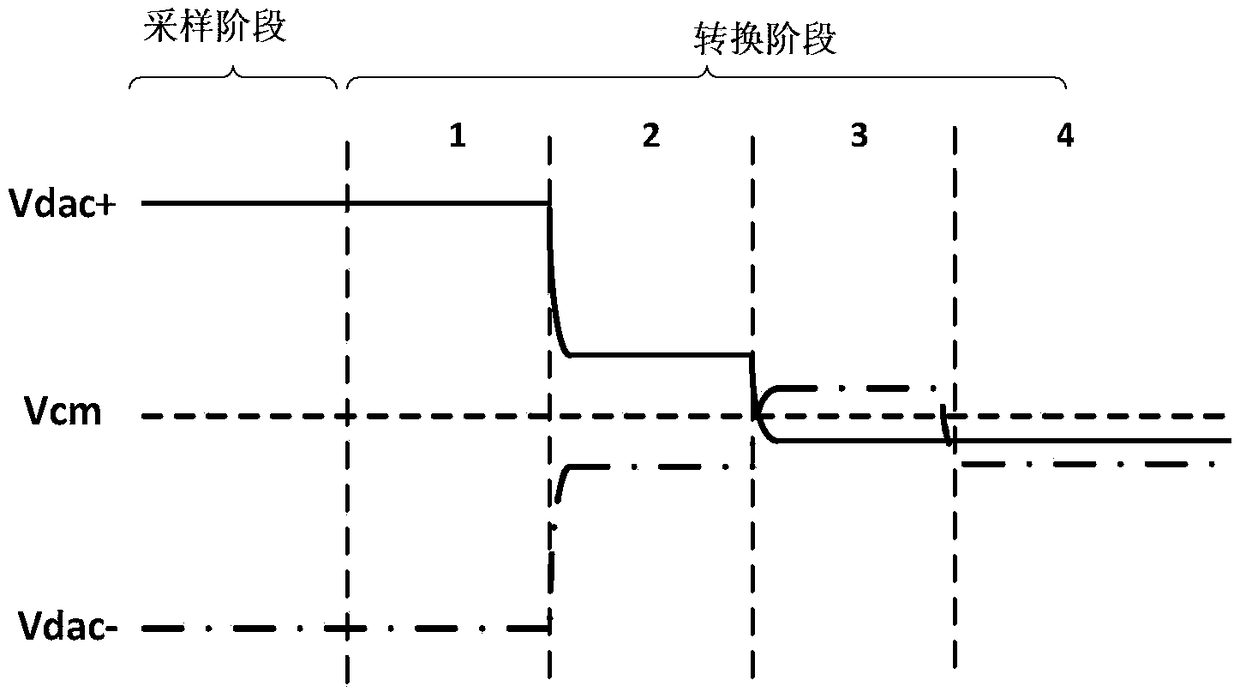

[0051] The present invention will be further described below in conjunction with the accompanying drawings.

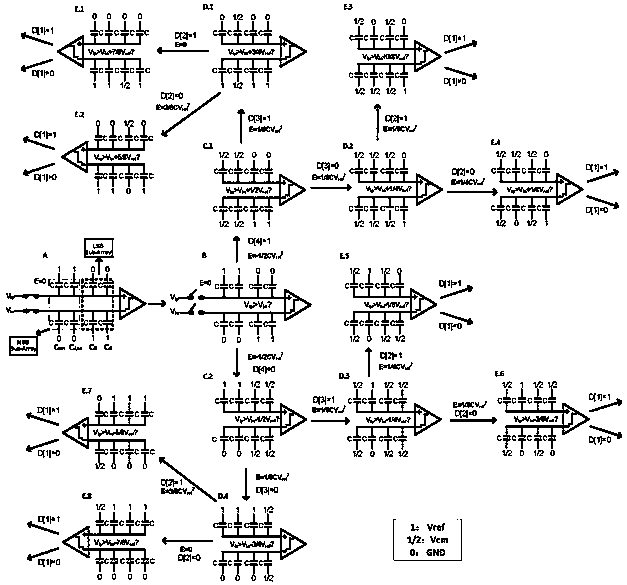

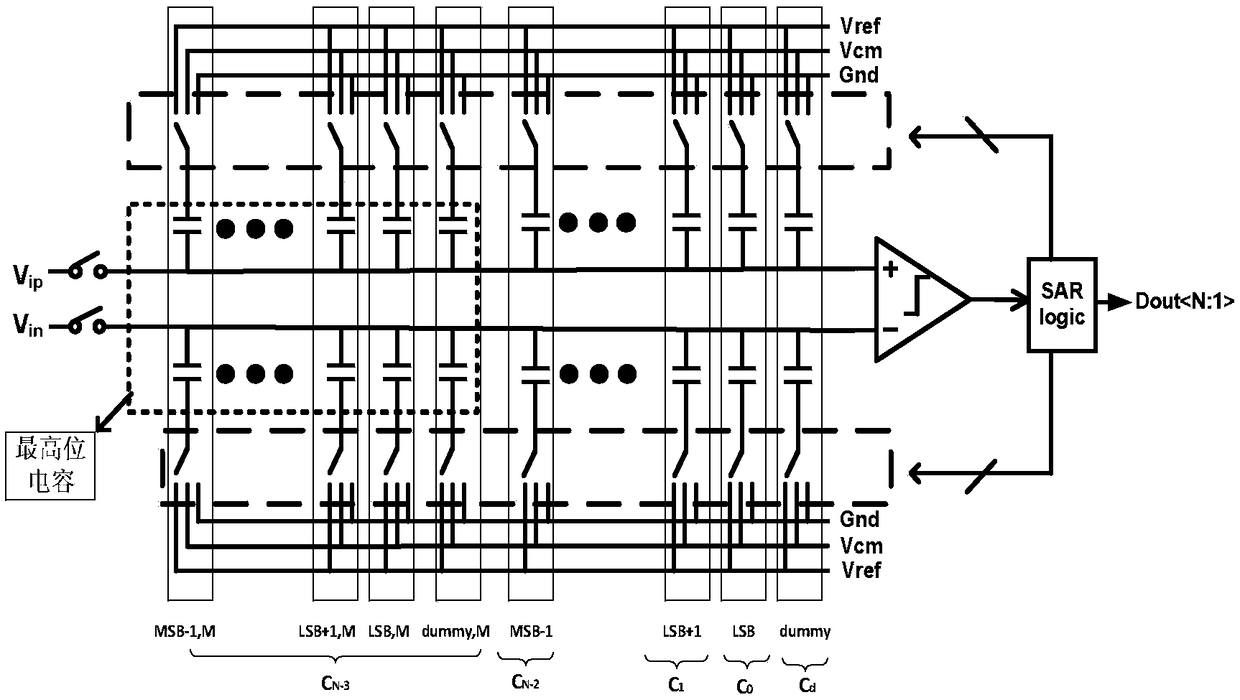

[0052] figure 1 Shown is a successive approximation analog-to-digital converter structure using upper plate sampling technique.

[0053] figure 1 The capacitor array shown can realize the conversion of N-bit SARADC. The entire capacitor is divided into identical upper and lower capacitor arrays. Each capacitor array mainly includes a dummy capacitor C d , the lowest bit capacitance C u and the highest bit capacitance C N-3 , other capacitors are allocated according to binary weights, specifically:

[0054] ①The highest capacitance C N-3

[0055] Highest capacitance C N-3 splits into the exact same structure as all other low-position capacitive structures, namely C N-3 Numerically equal to the sum of all other low capacitances, the expression is:

[0056] C N-3 =C D +C 0 +C 1 +C 2 +…+C N-4 = 2 N-3 C u

[0057] ②The lowest capacitance C 0 To the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More