Optimization method of CSP solder joint structural parameters for reducing stress in power cycle-harmonic response coupling

A power cycle and structural parameter technology, applied in the field of CSP solder joint structural parameter optimization, can solve problems such as inability to ensure reliable operation of CSP solder joints, inability to fully reflect the reliability of solder joints, and complex solder joint environments

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0060] A CSP solder joint structure parameter optimization method for reducing the stress under the power cycle-harmonic response coupling, specifically includes the following steps:

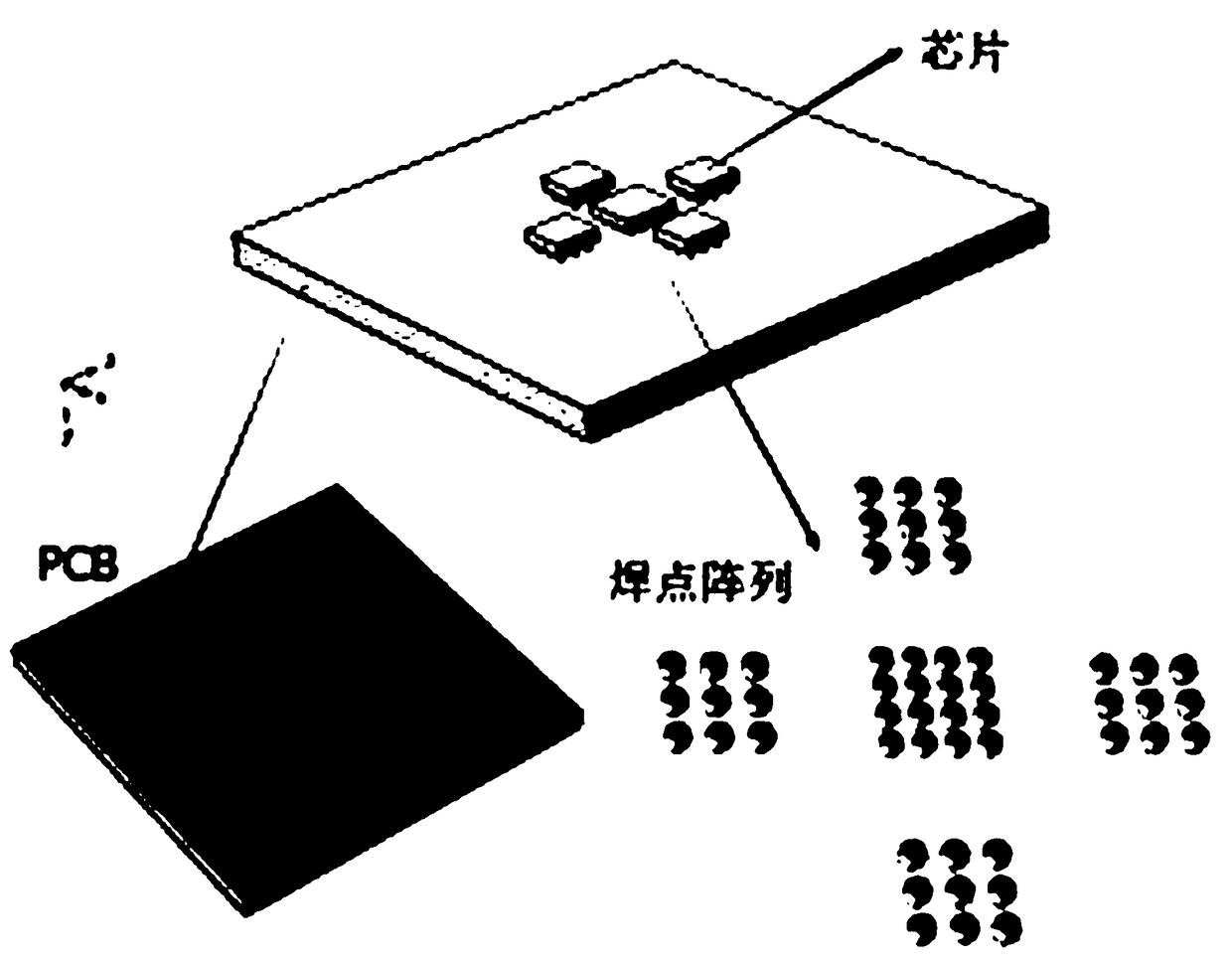

[0061] 1) Establish a simulation analysis model of COMSOL solder joints, such as figure 1 As shown, the material parameters are shown in Table 1 below;

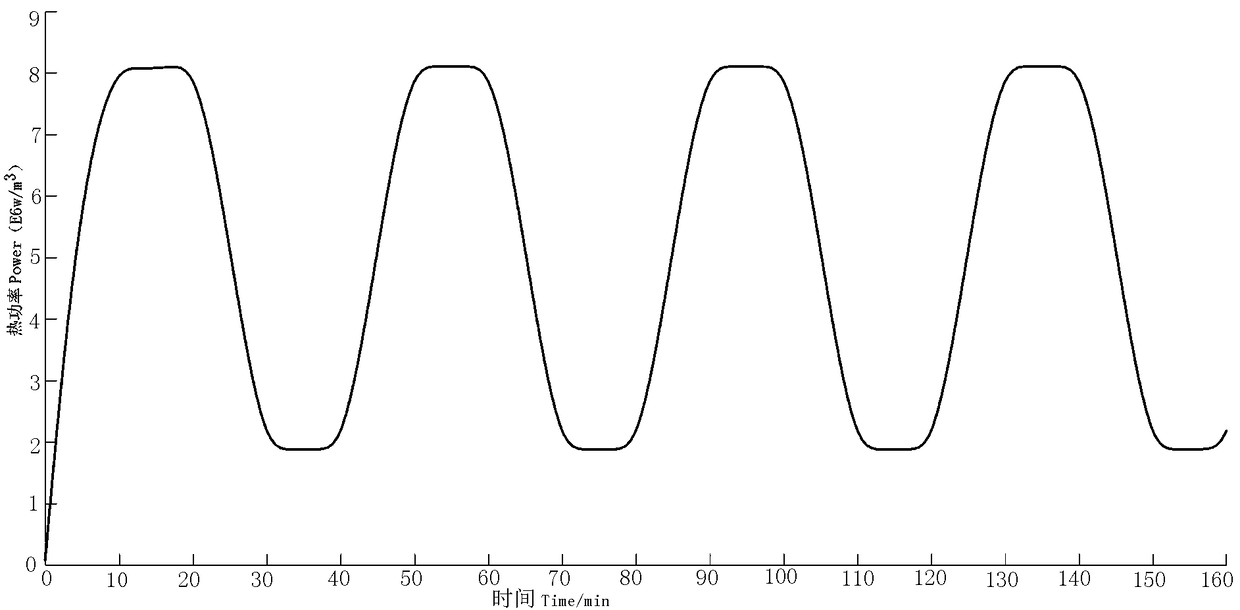

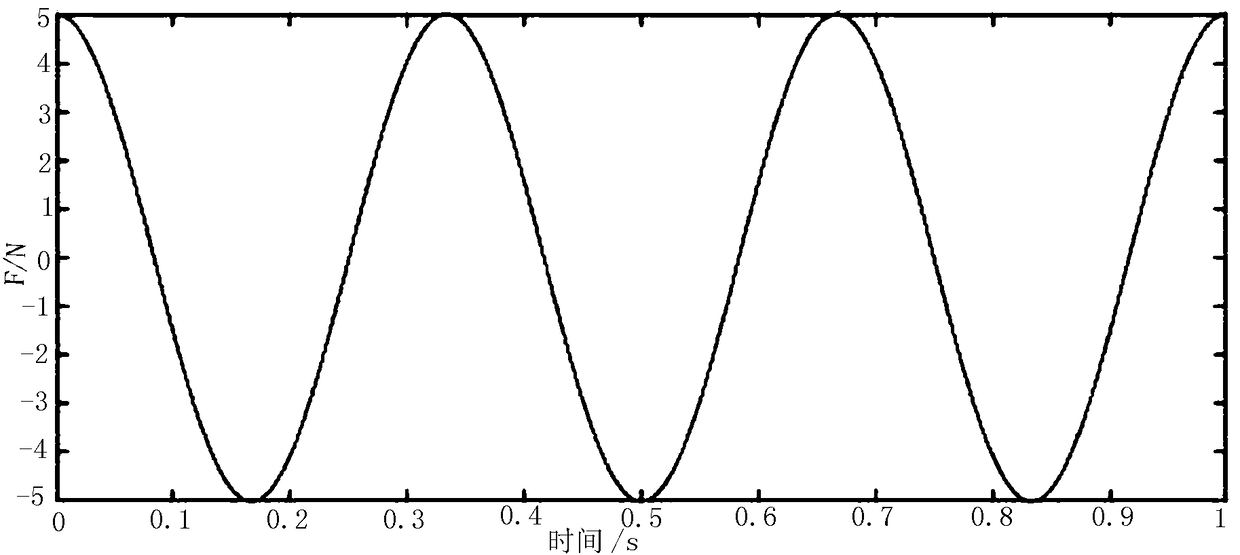

[0062] 2) Obtain the stress value under the power-harmonic response coupling load, and the applied power load curve and the harmonious response load curve are as figure 2 with image 3 As shown, the simulated stress map is as Figure 4 Shown

[0063] 3) Establish the influencing factors that affect the stress value obtained in step 2): the straight length of the large chip solder joint, the height of the large chip solder joint, the diameter of the small chip solder joint and the height of the small chip solder joint;

[0064] 4) Establish the parameter level value of the influencing factors that affect the stress value: select 3 level values for eac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More