A vdmos device structure with self-shutoff capability and its preparation method

A device structure and self-shutdown technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of VDMOS devices being turned on for a long time, irreversible post-stage load, and large current, so as to improve the reliability of use, Solve the reliability risk of the gate floating, the effect of high implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

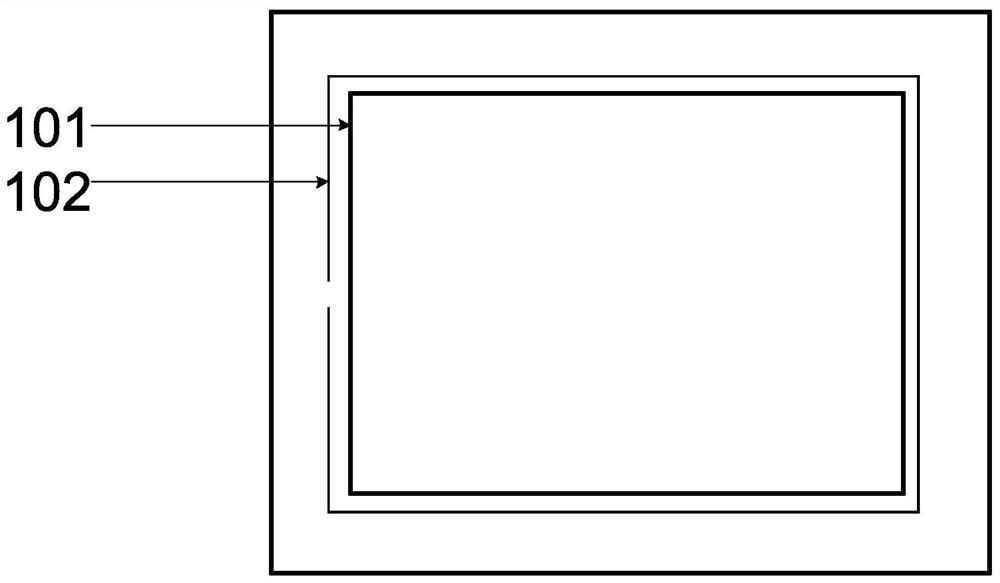

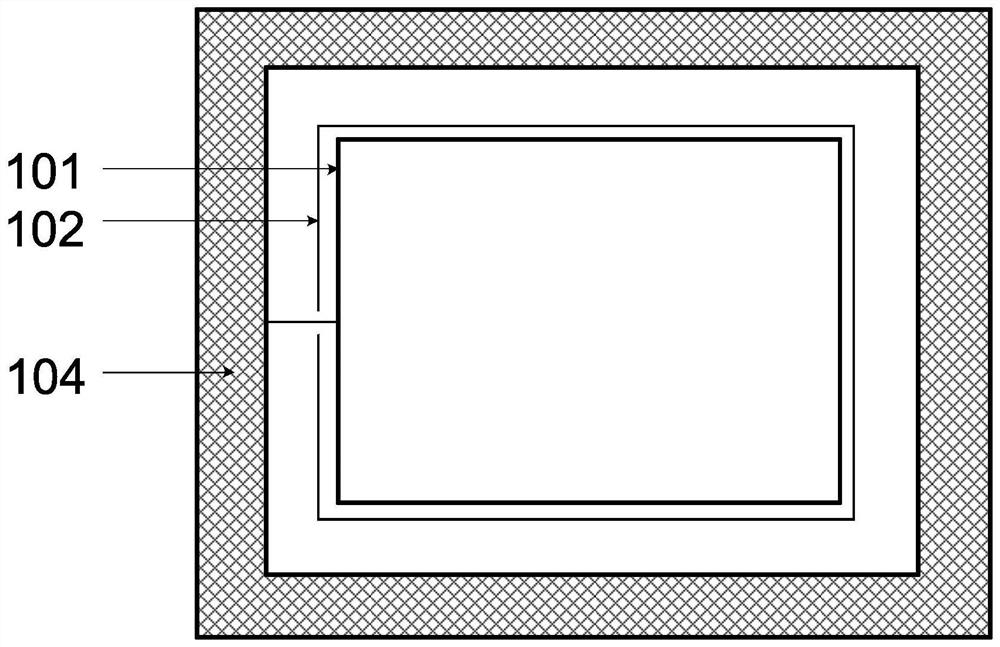

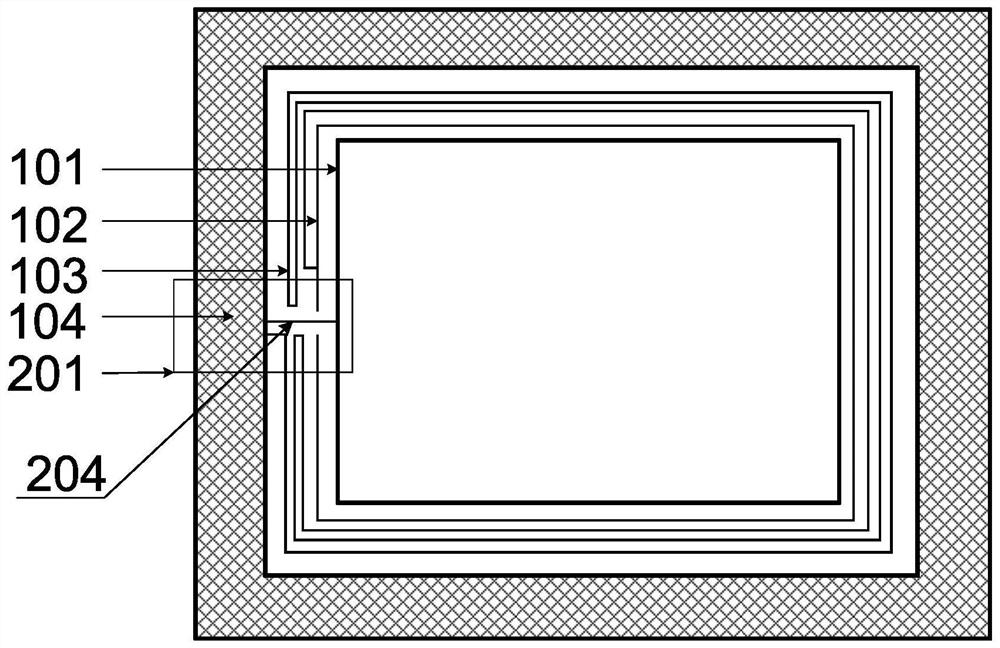

[0041]The present invention provides an embodiment. In this embodiment, if the chip cell 101 adopts a square cell of 3mm×3mm, the polysilicon resistor 103 surrounds the chip cell 101 for three weeks, and the polysilicon resistor 103 between adjacent two weeks 1um apart, this embodiment selects the block resistance R of the polysilicon resistor 103 □ =0.15Ω, wherein the width of the polysilicon resistance 103 is 0.5 μm, and the length of each cycle is about 12000 μm, then the resistance value of the polysilicon resistance 103 between the gate and the source is about 10K, and this value is used as the pull-up resistance resistance between the gate and the source The value is more reasonable; the calculation of the resistance is well known to those skilled in the art, and will not be repeated here.

[0042] In order to realize the special performance of the self-shutoff capability of the VDMOS device, the present invention provides a new terminal structure by adding a polysilicon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistance | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More