Method and device for automatically repairing the bit line fault of a NOR type memory array

A storage array and automatic repair technology, applied in information storage, static memory, read-only memory, etc., can solve the problems of few storage units and large overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

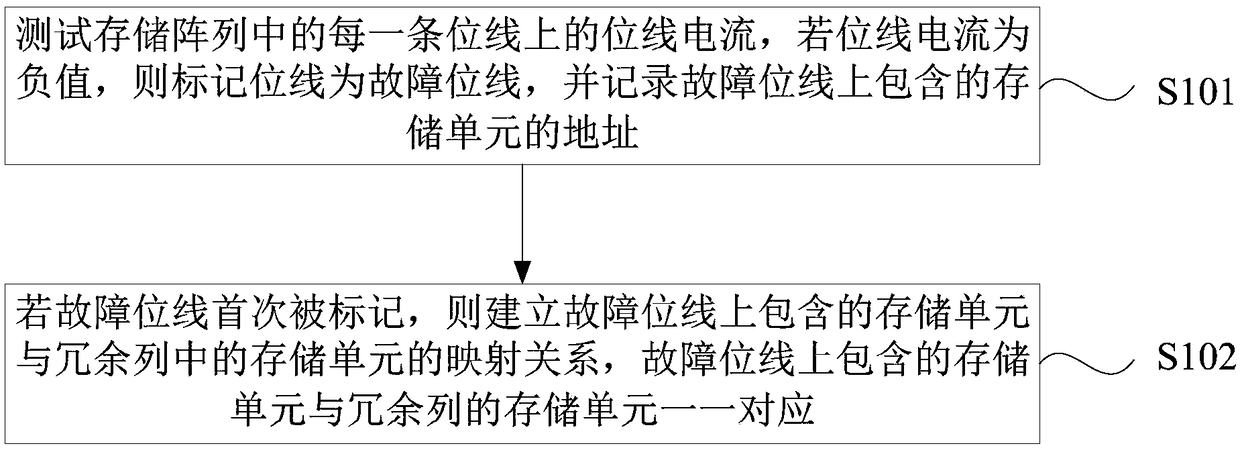

[0028] figure 1 A schematic flowchart of a method for automatically repairing bit line faults in a NOR memory array provided in Embodiment 1 of the present invention. The method can be performed by a device for automatically repairing bit line failures in a NOR memory array, wherein the device can be Hardware and / or software to achieve, specifically including the following steps:

[0029] Step 101: Test the bit line current on each bit line in the memory array. If the bit line current is negative, mark the bit line as a faulty bit line, and record the address of the memory cell included on the faulty bit line.

[0030] In this embodiment, the drains of a plurality of memory cells are connected to one bit line in the NOR type memory array, and the bit line current on each bit line in the memory array is tested. Specifically, on the bit line The voltage on the word line of a memory cell above is about 7V, the voltage on the bit line is about 1V, the source is grounded, and the ...

Embodiment 2

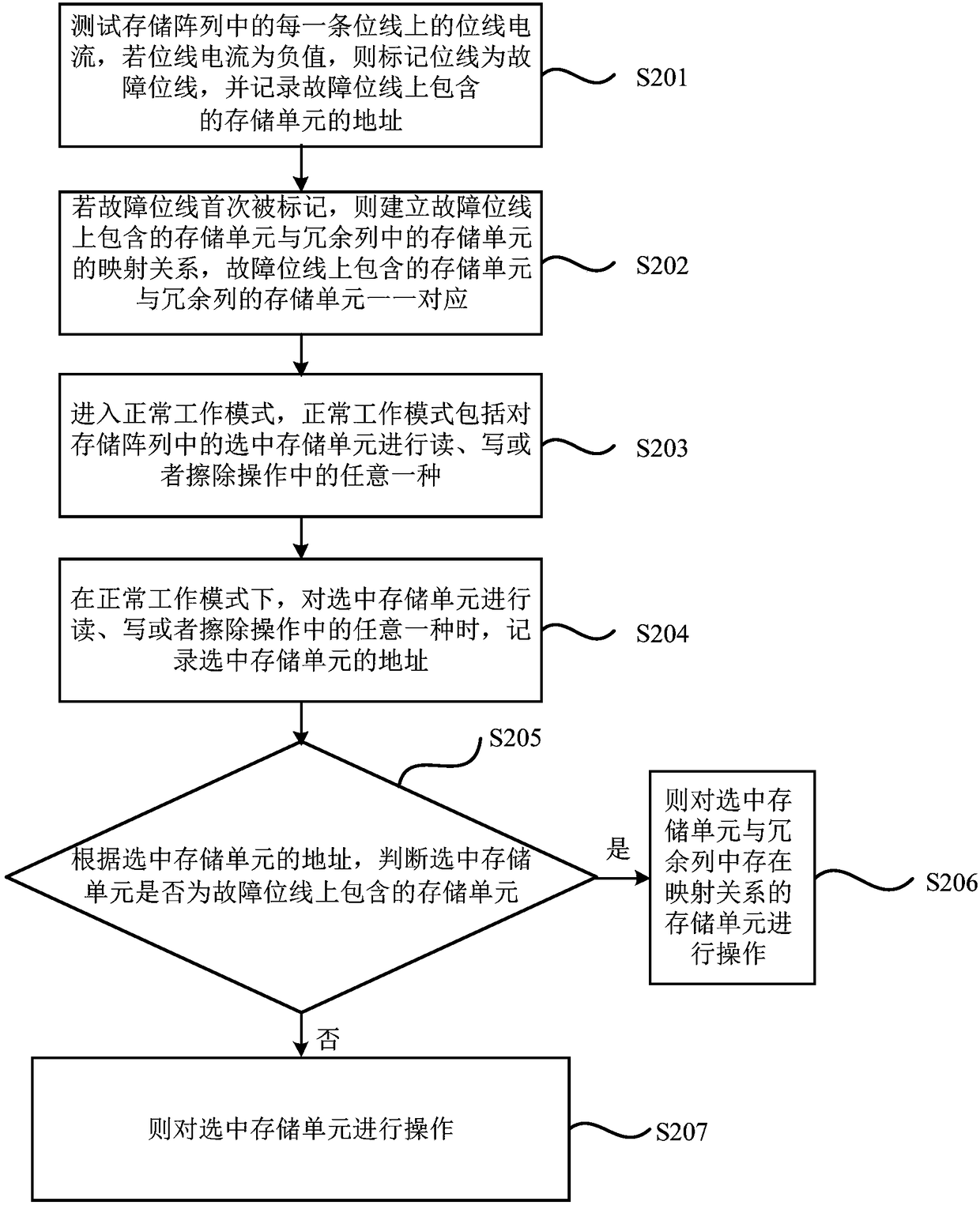

[0037] figure 2 This is a schematic flowchart of a method for automatically repairing bit line faults in a NOR memory array provided by an embodiment of the present invention. This embodiment is based on the above-mentioned embodiment. After step 102 is completed, step 202 in this embodiment is performed. , the storage array still has to enter the normal working mode. When the selected storage unit is the storage unit included in the faulty bit line, the corresponding operation is performed on the selected storage unit and the storage unit with the mapping relation in the redundant column according to the mapping relationship. . like figure 2 As shown, the method includes the following steps:

[0038] Step 201: Test the bit line current on each bit line in the memory array. If the bit line current is negative, mark the bit line as a faulty bit line, and record the address of the memory cell contained on the faulty bit line.

[0039] Step 202: If the faulty bit line is mar...

Embodiment 3

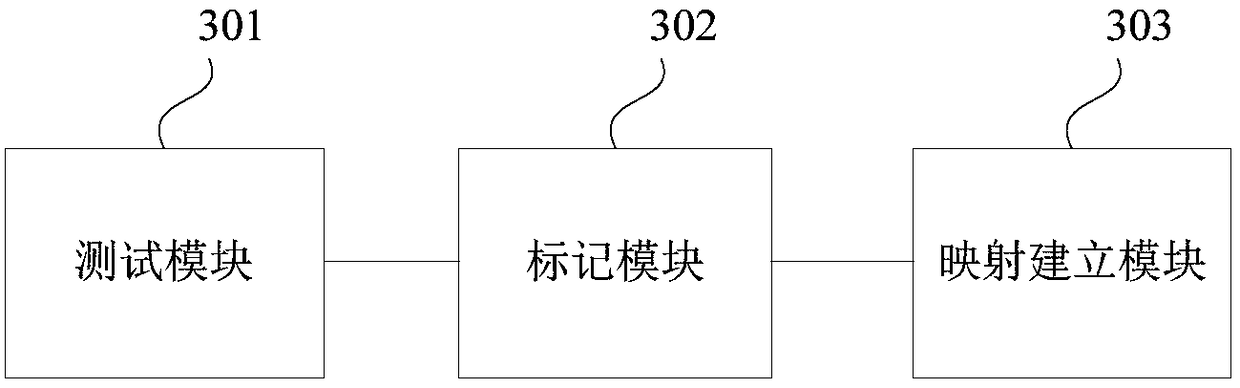

[0050] image 3 Shown is a schematic structural diagram of a device for automatically repairing bit line faults in a NOR memory array provided in Embodiment 3 of the present invention. The device can be implemented by hardware, such as image 3 As shown, the device includes:

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap