A descriptor-based PCIE bus DMA controller and a data transmission control method

A DMA controller, data transmission control technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems that do not involve multi-channel transmission, can not meet, do not consider the different priorities of data of multiple channels of DMA, and achieve improvement The effect of improving transmission efficiency, increasing transmission size, and reducing CPU burden

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

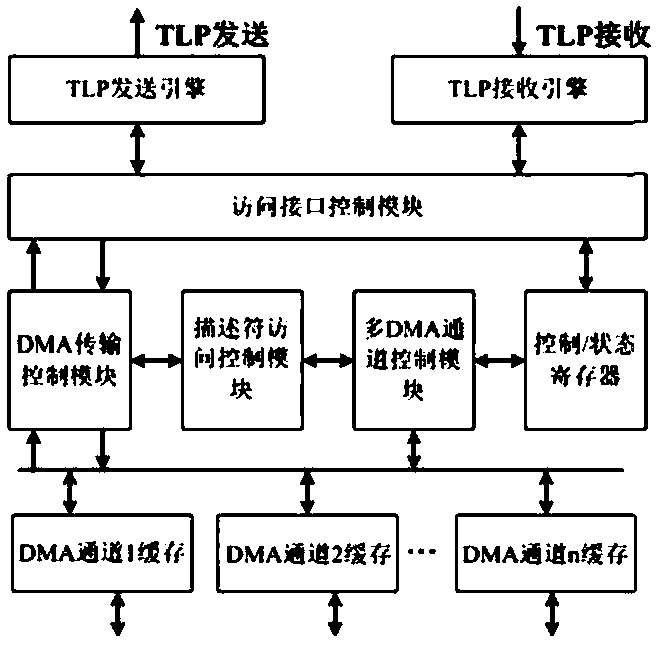

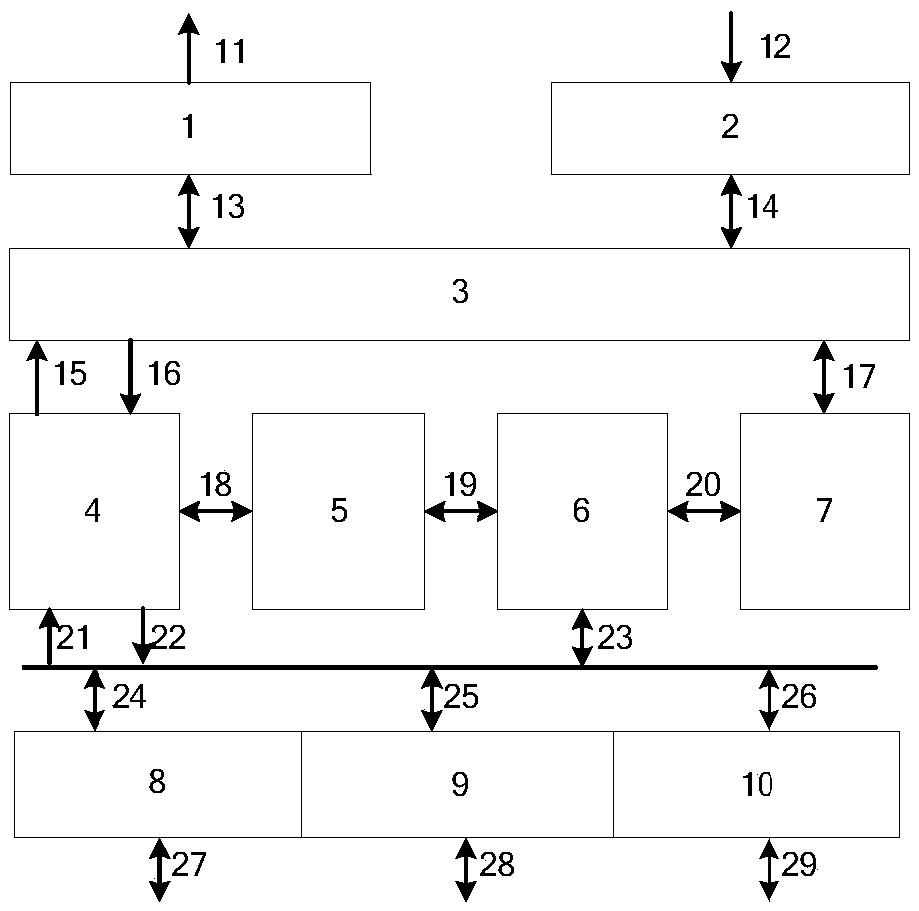

[0053] According to content of the present invention, design detailed implementation scheme, DMA controller structure is as figure 2 shown. The DMA controller of the present invention needs to perform an initialization operation before use, and the initialization operation includes two parts:

[0054] (1) Initialization of the host memory. The host memory needs to open up a descriptor table space and a data cache space. Each DMA channel has two descriptor tables, which are the upload data descriptor table and the send data descriptor table. Each descriptor table contains multiple descriptors with consecutive addresses, and each descriptor points to a buffer in the unique host system memory.

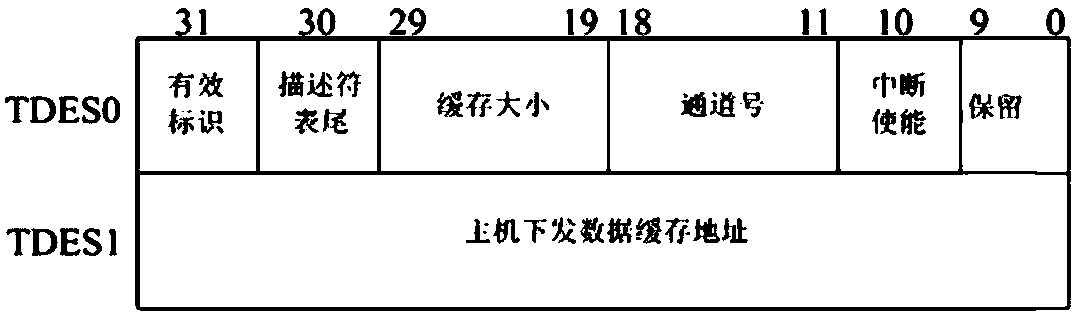

[0055] Figure 4 The DMA upload data cache descriptor, the upload descriptor (TDES) is used for data upload data transmission from the PCIE node device to the host memory. image 3 The data cache descriptor is issued for DMA, and the delivery descriptor (RDES) is used for data transmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More