Fast Fourier transform hardware design method based on base 2-2 algorithm

A technology of Fourier transform and hardware design, applied in CAD circuit design, calculation, complex mathematical operations, etc., can solve the problems of adding storage units, consuming large hardware resources, and not improving the utilization rate of butterfly units, etc., to achieve high hardware Efficiency, the effect of saving hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings.

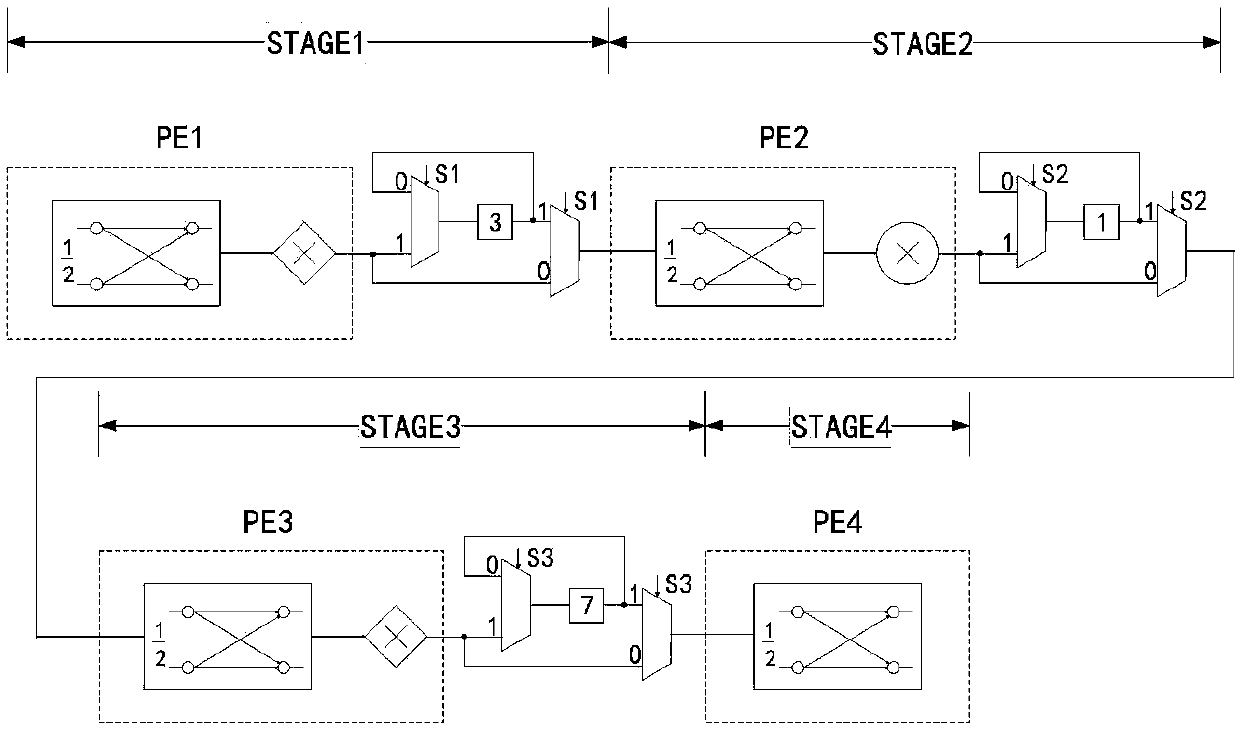

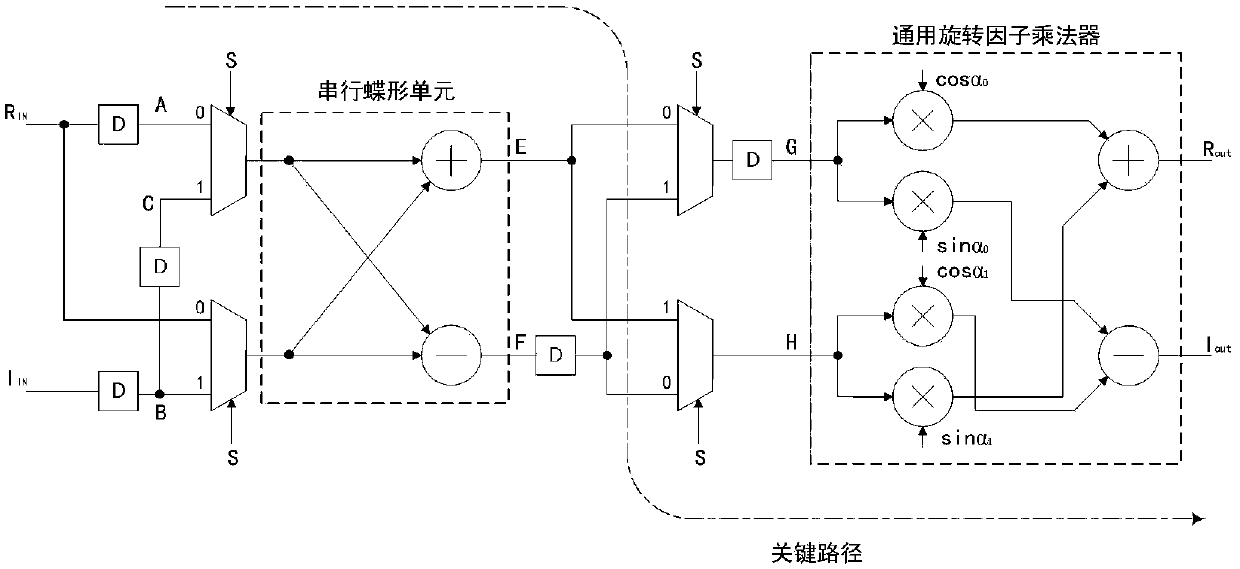

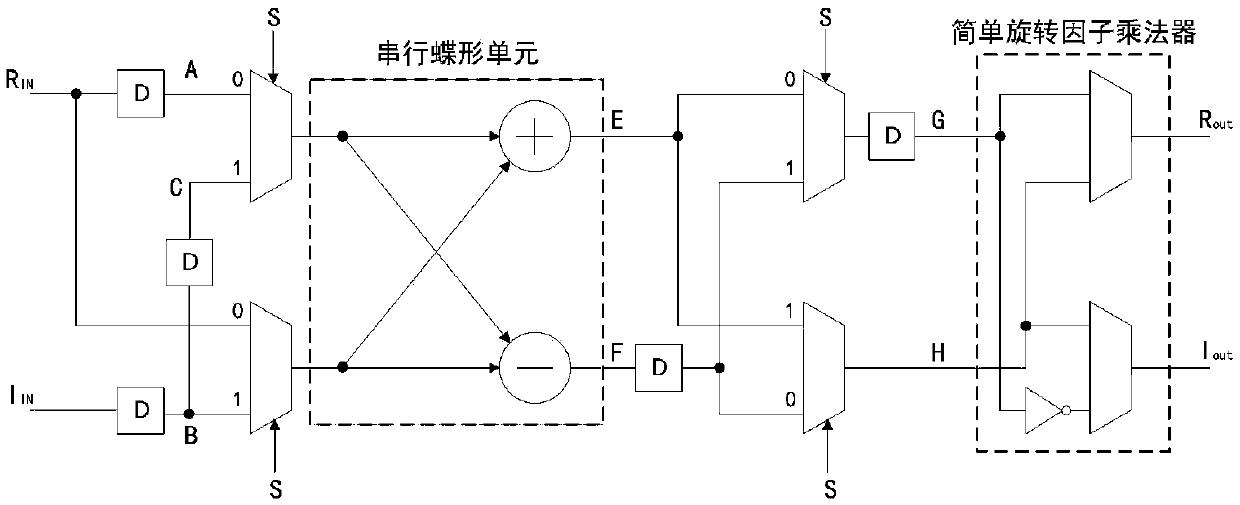

[0024] Such as figure 1 As shown, the base 2 of the 16-point frequency domain decimation is given 2 The FFT of the structure. This structure consists of 4 levels, which contain processing units and reverse order units respectively. The processing unit includes a butterfly unit and a twiddle factor multiplier unit. The simple twiddle factor multiplier is represented by a diamond, and the complex twiddle factor multiplier is represented by a circle. The complex twiddle factor multiplier is the general twiddle factor multiplier in the prior art. In order to distinguish it from the simple twiddle factor multiplier, it is called here is a complex twiddle factor multiplier.

[0025] processing unit

[0026]The number 1 / 2 is marked on the serial butterfly unit, which means that it only needs half the logic units compared with the traditional butterfly processing unit, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More