Software and hardware partitioning method for a dynamic part reconfigurable system-on-chip

A technology of software and hardware division and dynamic part, which is applied to digital computer components, architecture with a single central processing unit, instruments, etc., can solve the problems of local optimal solution existing model complexity, too large, etc., and achieve guaranteed matching Degree, reduce complexity, improve the effect of solving speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The present invention will be further described below in conjunction with accompanying drawing:

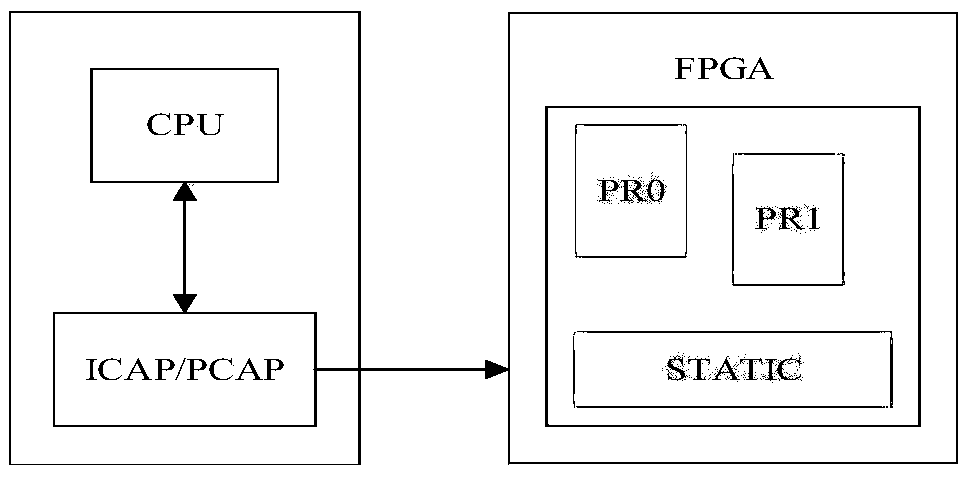

[0058] figure 1 is the SoC heterogeneous system targeted by the present invention. like figure 1 As shown, the heterogeneous system-on-chip integrates CPU and field-programmable gate array (FPGA), and the FPGA in this system has the characteristic of dynamic partial reconfiguration. The FPGA programmable logic unit in the system can be divided into several partially reconfigurable areas, such as PR0 and PR1 in the figure, each reconfigurable area can realize functional reconfiguration by downloading different configuration files through ICAP / PCAP according to actual needs;

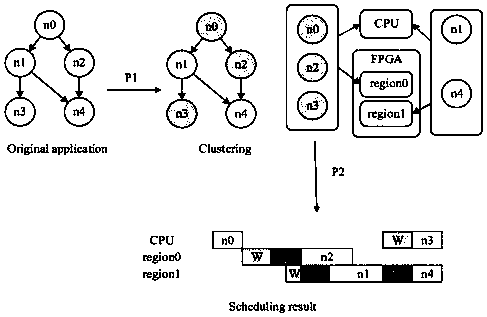

[0059] figure 2 It is the software and hardware division process described in 1.2.

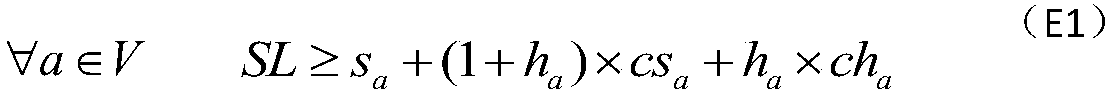

[0060] To sum up, the efficient MILP model proposed by the present invention speeds up the problem-solving speed by reducing the complexity of variables and constraint equations, and can provide developers of dynam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More