A reference clock frequency multiplier circuit and algorithm based on numerical control delay duty ratio calibration

A duty cycle and duty cycle detection technology, which is applied in the field of analog integrated circuits and radio frequency design, can solve the problems of cumbersome, large frequency multiplication noise, and poor output signal phase noise performance, and achieve small area, low power consumption, and suitable Good matching effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

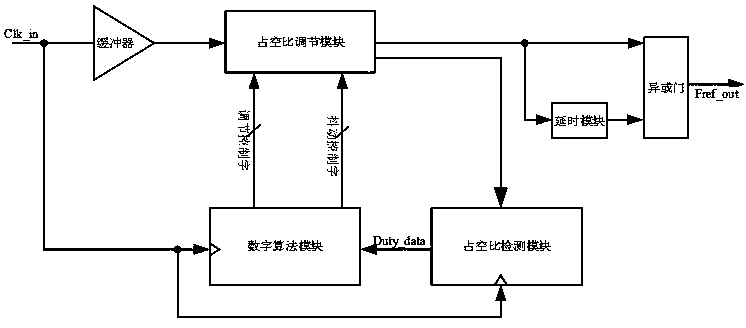

[0024] The XOR gate frequency multiplier structure with digital duty cycle calibration of the present invention is as follows figure 1 Shown:

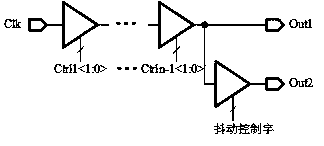

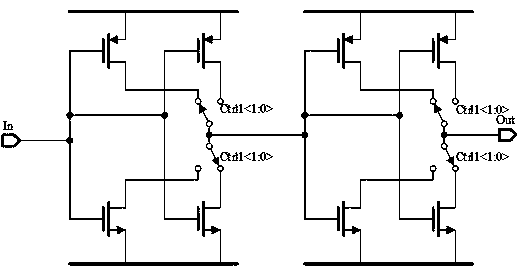

[0025] The externally supplied clock signal enters the buffer, and also enters the digital algorithm module and the duty ratio detection module to provide the clock signal through its internal frequency division. The output signal of the buffer enters the duty ratio adjustment module, and the first output of the duty ratio adjustment module The signal is divided into two channels and enters the delay module and the XOR gate respectively, wherein the output signal of the delay module also enters the XOR gate, and the XOR gate outputs a double frequency signal; the second output signal of the duty cycle adjustment module is controlled by the duty cycle The detection module monitors, and the duty cycle d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More