Semiconductor chip test system and method

A chip testing and semiconductor technology, applied in the testing field of semiconductor chip testing interface devices, can solve problems such as expensive and time-consuming testing, and achieve the effects of reducing quantity, shortening downtime, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In the following description, several specific details are set forth. However, embodiments as described herein may be practiced without some of the specific details. In particular embodiments, well-known structures and techniques have not been shown in detail in order not to obscure the understanding of the description.

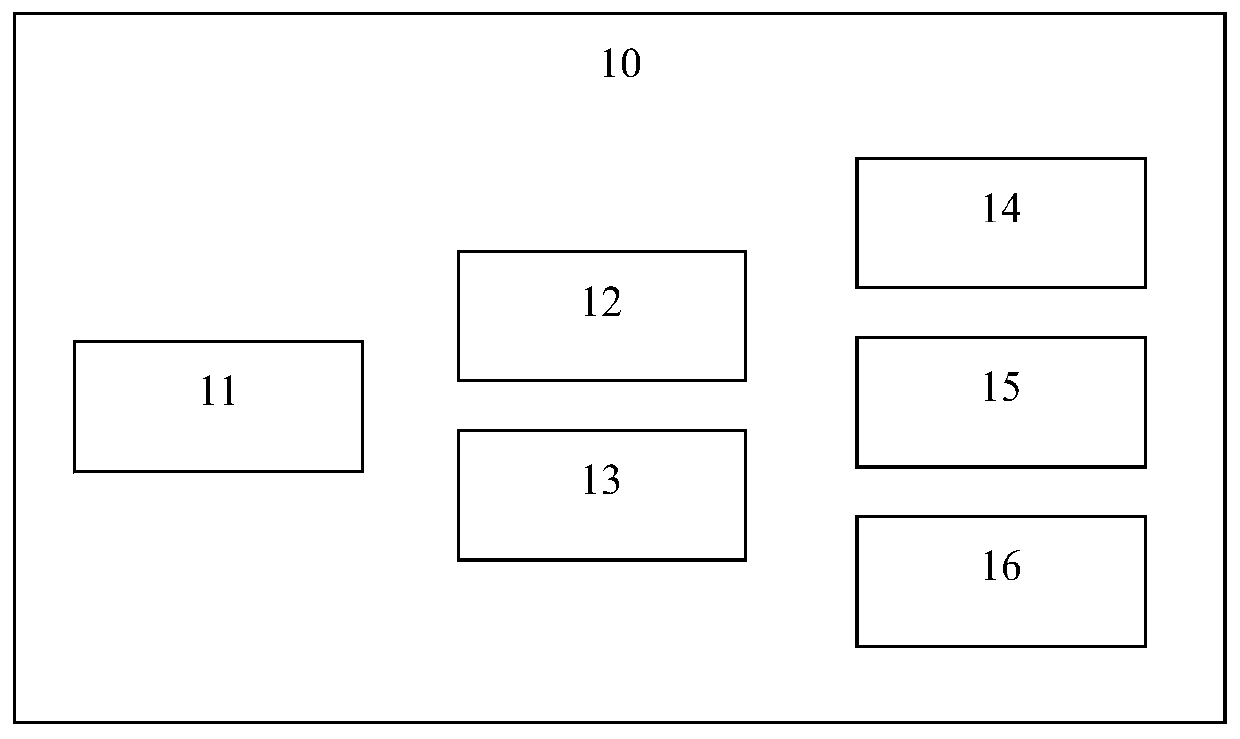

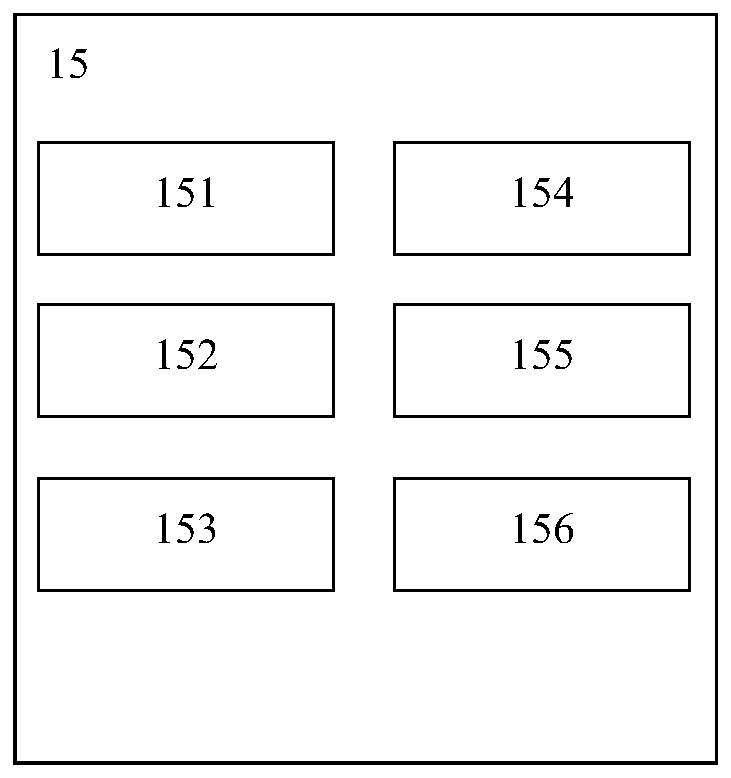

[0016] figure 1 A block diagram of a semiconductor chip testing system 10 according to one embodiment of the present invention is shown. The semiconductor chip test system 10 includes a robot arm 11 , a test interface device 12 , a test circuit 13 , an image acquisition device 14 , a processor 15 and a controller 16 .

[0017] The robotic arm 11 is used to pick up a semiconductor chip to be tested, such as a wafer to be tested or a packaged die, and place the semiconductor chip in the test interface device 12 or remove it from the test interface device 12 . In some cases, the robot arm 11 may be omitted from the semiconductor chip testing system 10 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More