A High Speed Sensitive Amplifier Circuit of SRAM Type Memory

A sensitive amplifier and memory technology, which is applied in the direction of static memory, digital memory information, information storage, etc., can solve the problems of affecting the memory reading speed and large input voltage difference, so as to improve the reaction speed and processing ability, and the input voltage difference The effect of reducing the requirements and speeding up the readout speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with accompanying drawing and concrete implementation the present invention is described in further detail:

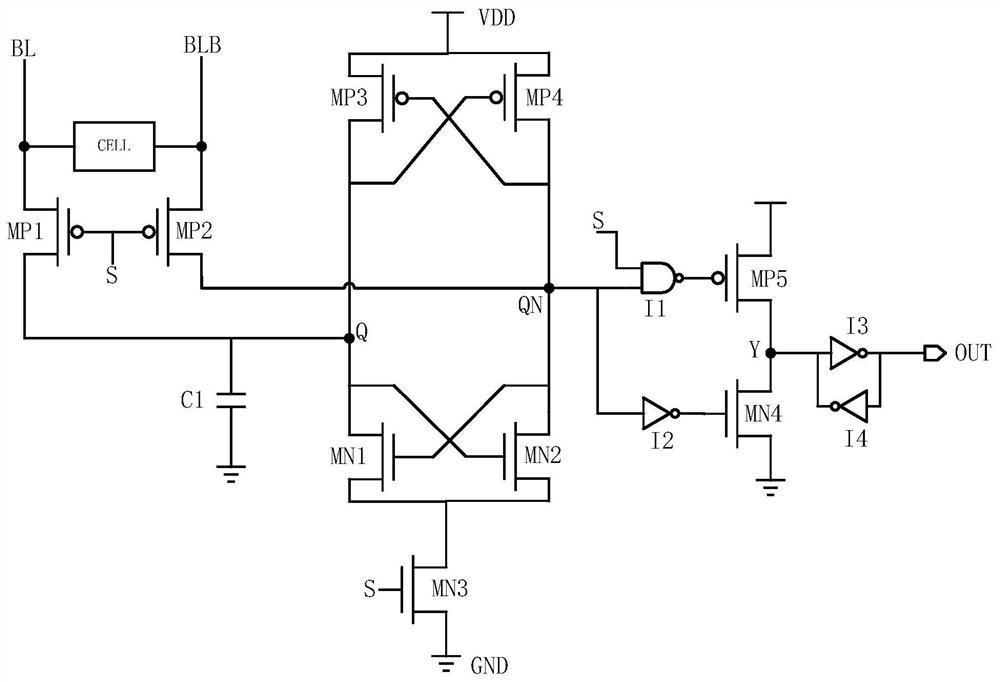

[0024] Such as figure 1 Shown is the circuit structure diagram of the high-speed sense amplifier of the SRAM type memory of the present invention. Consists of: bit line read switch module, latch type amplifier module and output module. The bit line read switch module includes PMOS transistors MP1, MP2, capacitor C1; the latch type amplifier module includes PMOS transistors MP3, MP4, NMOS transistors MN1, MN2, MN3; the read module includes NAND gate I1, inverter I2 -I4, PMOS transistor MP5, NMOS transistor MP4.

[0025] The source terminals of the PMOS transistors MP1 and MP2 in the bit line read switch module are respectively connected to the SRAM unit bit line (CELL) output BL and BLB terminals, and the gate terminals of the PMOS transistors MP1 and MP2 are connected in common, controlled by the read enable input signal S, and the drain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More