A four-stage assembly line RISC-V processor with a rapid data bypass structure

A RISC-V and pipeline technology, applied in the direction of machine execution devices, etc., can solve the problems of lack of versatility, lack of tool chain support, etc., and achieve the effect of simple structure, high hardware resources, and reduced information transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

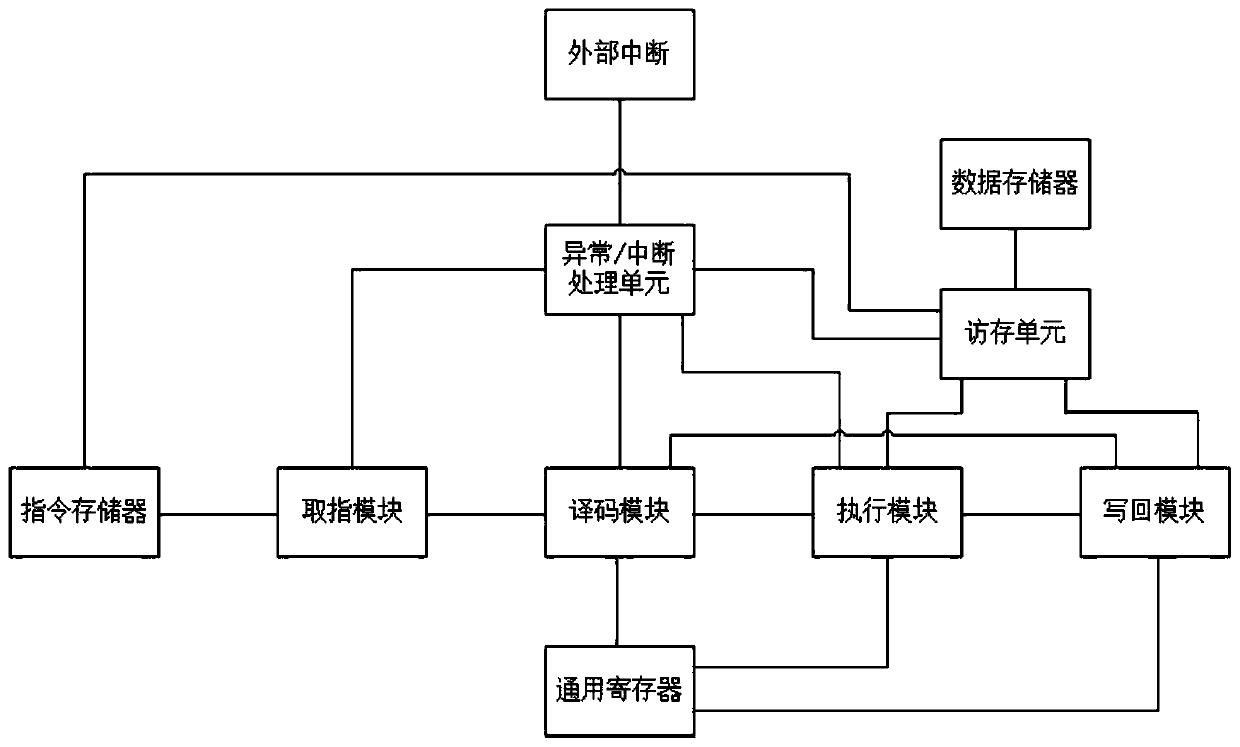

[0044] This embodiment provides a four-stage pipeline RISC-V processor with a fast data bypass structure proposed by the present invention, which includes a four-stage pipeline structure with a total length of four stages that can be dynamically adjusted according to the instruction type, a memory access unit, an exception / interrupt Processing unit, instruction memory, and data memory. Both the data bus and the address bus between the memory and the CPU are 32 bits wide.

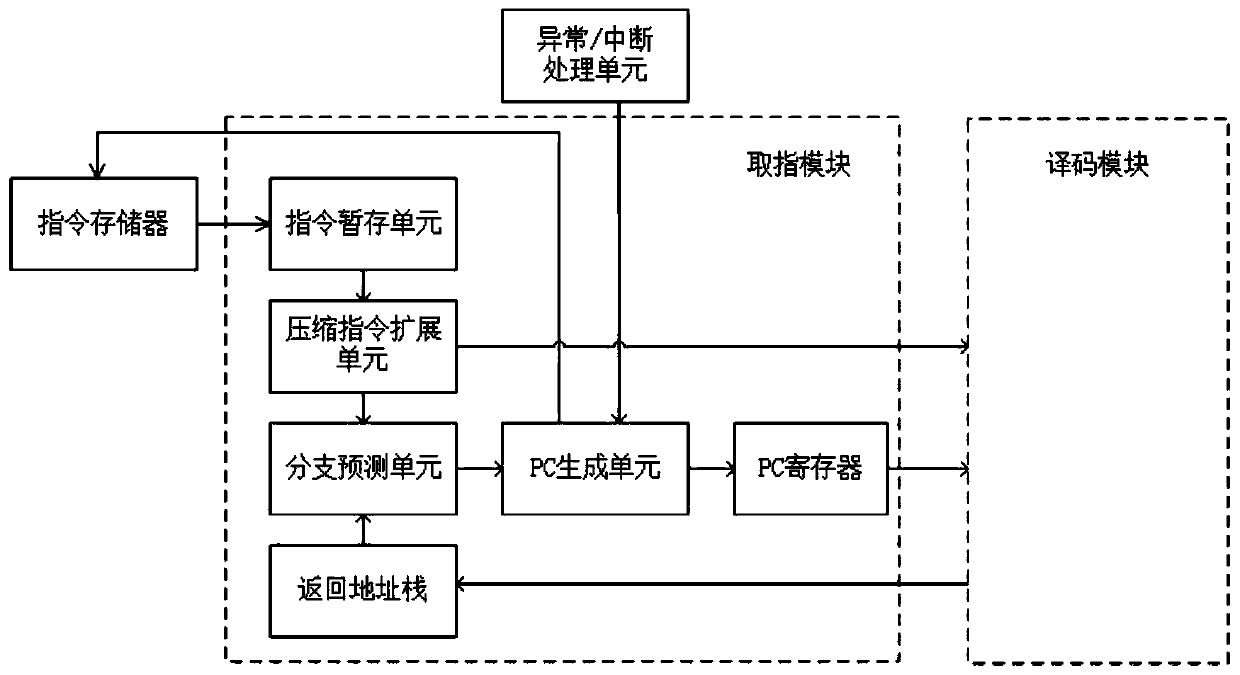

[0045] The first stage of the pipeline is the instruction fetch module. The function of the instruction fetch module is to continuously fetch the instruction to be executed by the CPU from the instruction memory according to the running condition of the program. The instruction fetch module includes the following parts:

[0046] 1. PC register

[0047] The PC register stores the PC corresponding to the instruction passed from the instruction memory of the current cycle to the instruction fetch module.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More