Method for manufacturing 3D NAND flash memory with large number of stacked layers and 3D NAND flash memory

A manufacturing method and technology of stacking layers, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as difficulties, unbalanced stress between films, affecting the accuracy of photolithography process, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

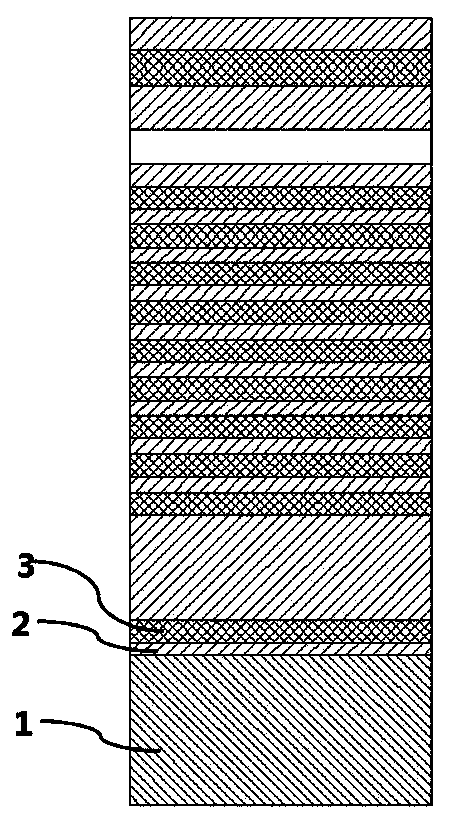

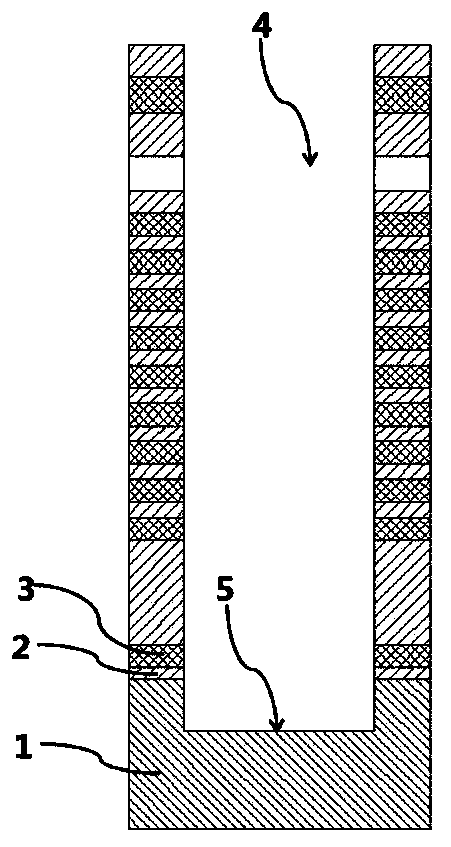

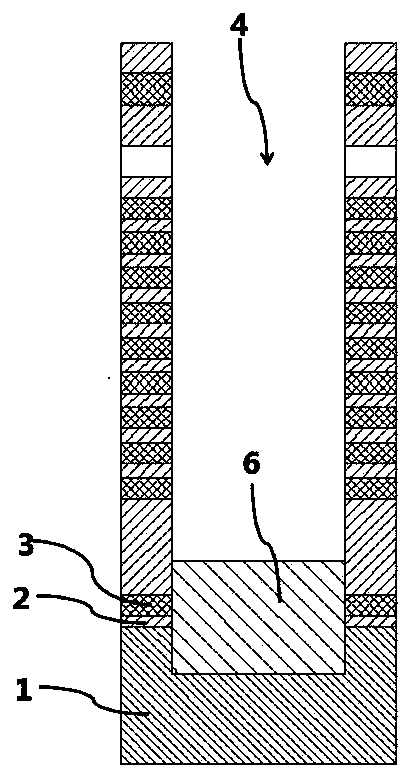

[0089] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

[0090] In the interest of clarity, not all features of an actual implementation are described. In the following description, well-known functions and constructions are not described in detail since they would obscure the invention with unnecessary detail. It should be appreciated that in the development of any actual embodiment, numerous implementation details must be worked out to achieve the developer's specific goals, such as ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More