Method for forming semiconductor device and semiconductor device

A semiconductor and device technology, applied in the formation method of semiconductor devices and the field of semiconductor devices, can solve the problems of reducing the AC performance of devices, large parasitic capacitance, etc., and achieve the effect of improving AC performance, small parasitic capacitance, and improving DC performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

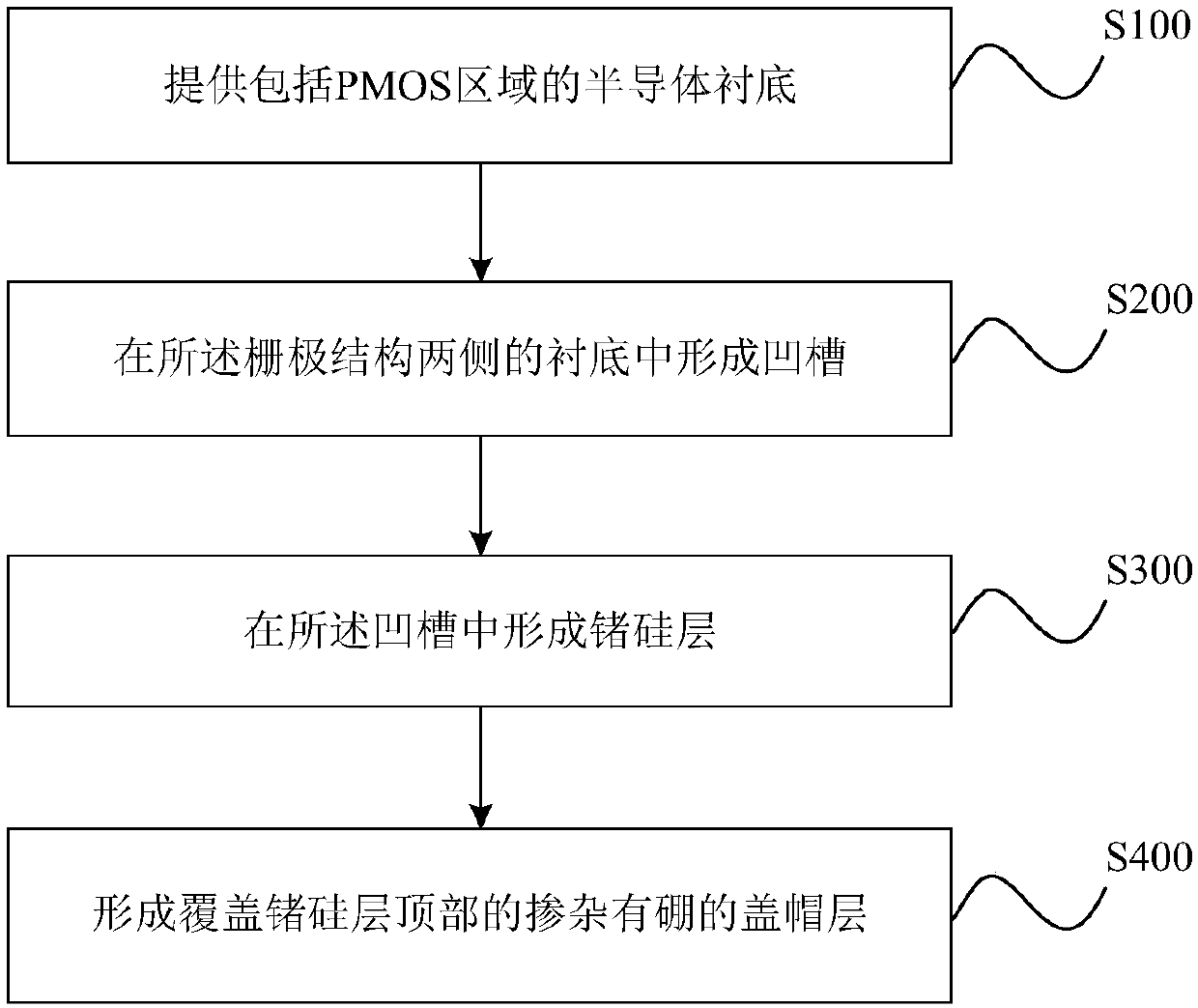

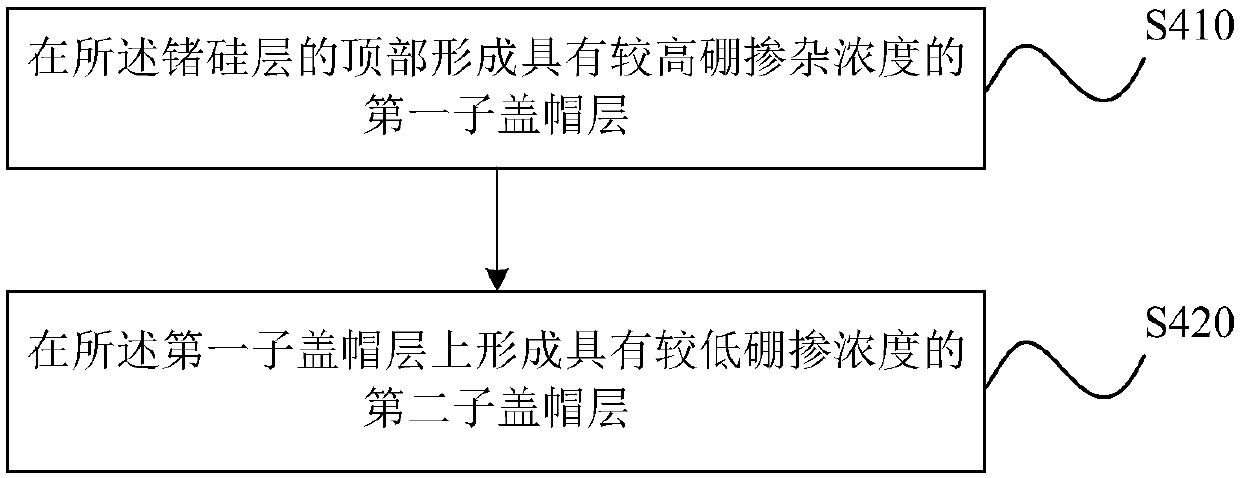

Method used

Image

Examples

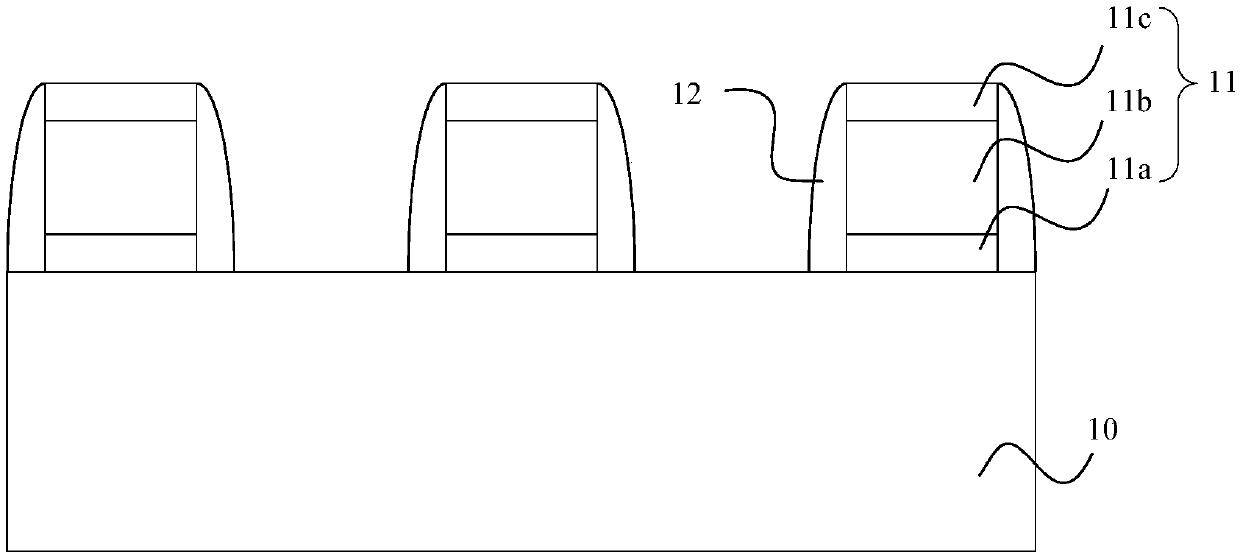

Embodiment Construction

[0045] The present invention is described below based on examples, but the present invention is not limited to these examples. In the following detailed description of the invention, some specific details are set forth in detail. The present invention can be fully understood by those skilled in the art without the description of these detailed parts. In order not to obscure the essence of the present invention, well-known methods, procedures, procedures, components and circuits have not been described in detail. Additionally, those of ordinary skill in the art will appreciate that the drawings provided herein are for illustrative purposes and are not necessarily drawn to scale.

[0046] Unless the context clearly requires, throughout the specification and claims, "comprises", "comprises" and similar words should be interpreted in an inclusive sense rather than an exclusive or exhaustive meaning; that is, "including but not limited to" meaning. In the description of the pres...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More