Semiconductor device having body contacts with dielectric spacers and corresponding methods of manufacture

A semiconductor and spacer technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as increasing the quality factor of the total gate charge

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

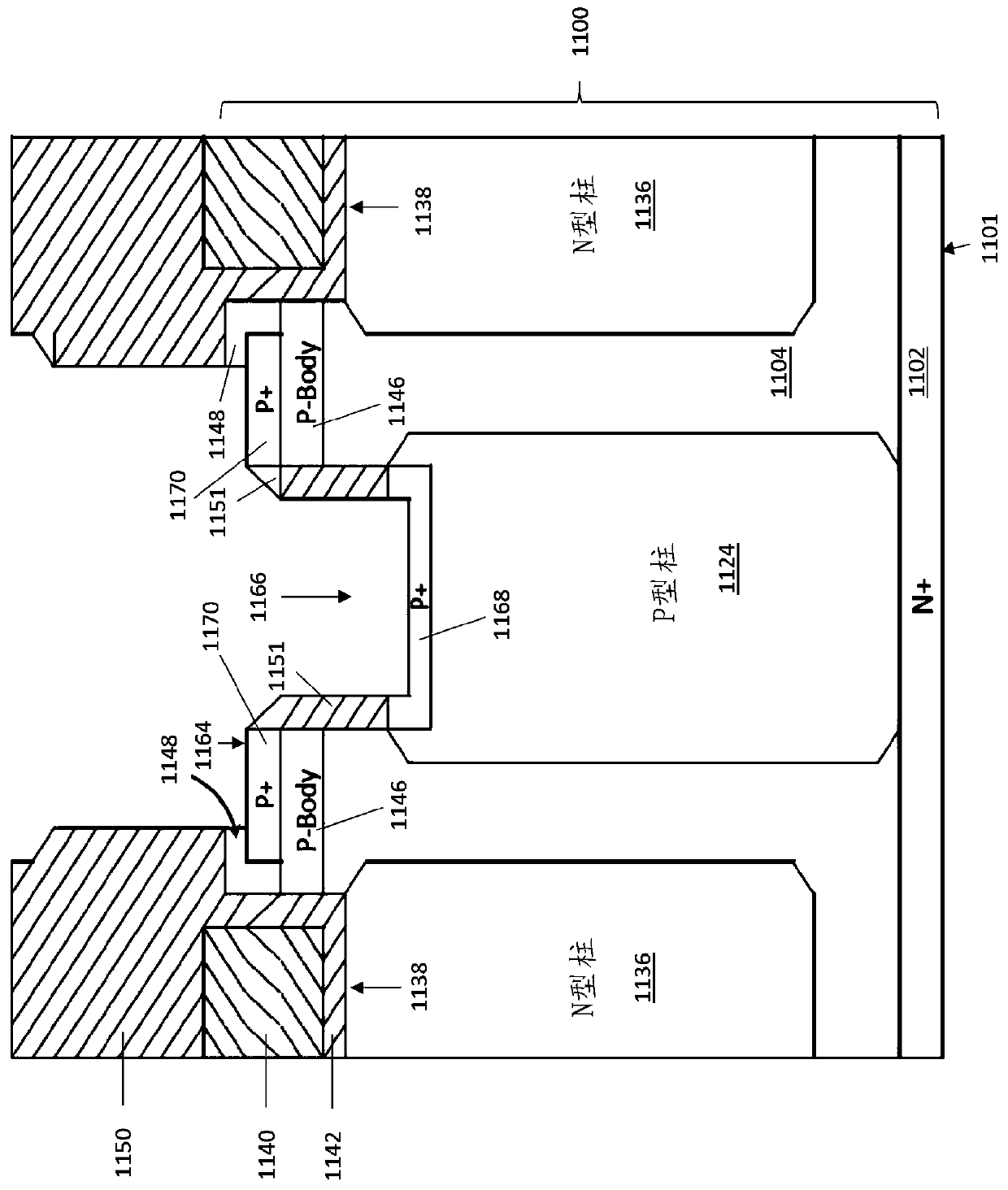

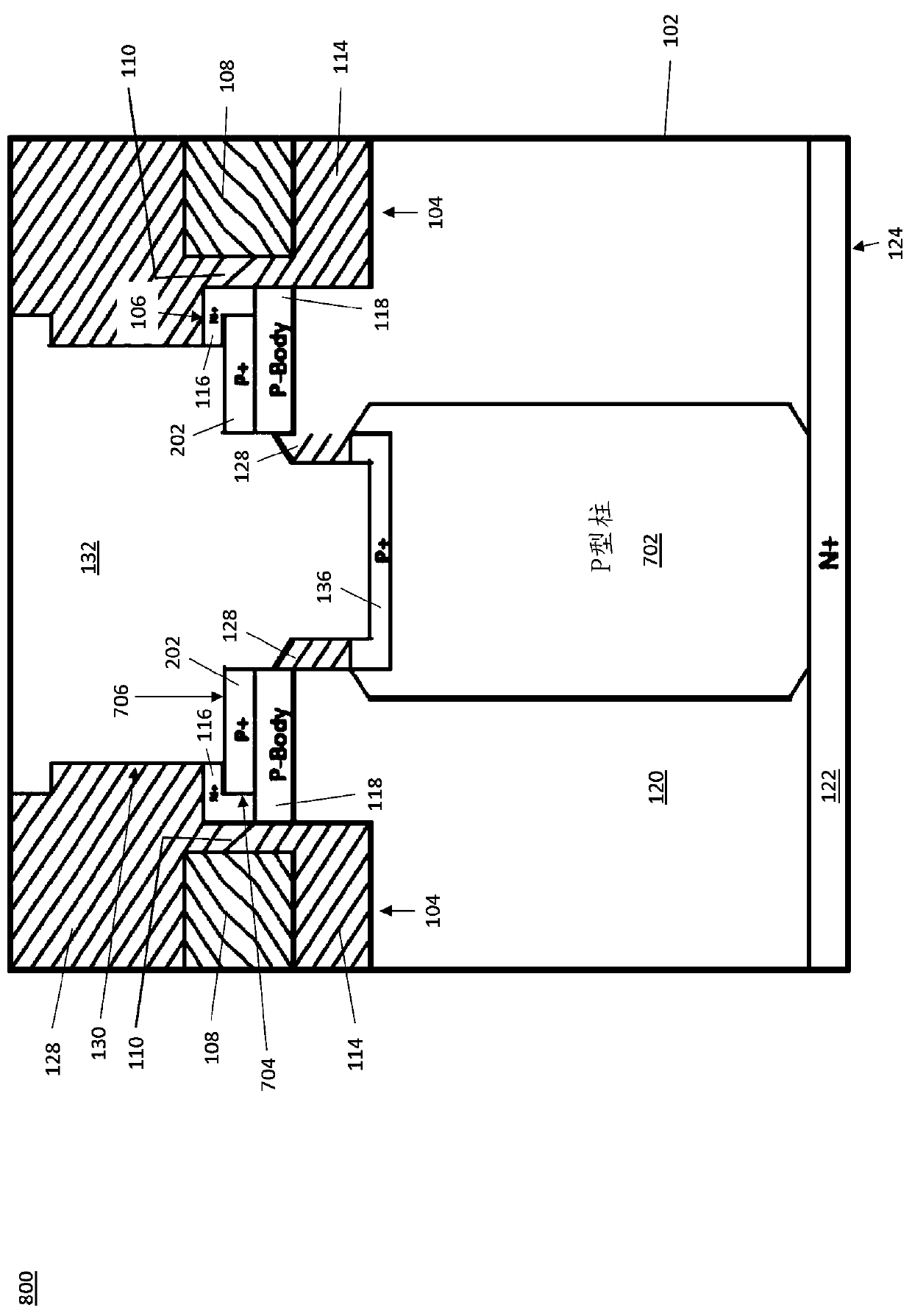

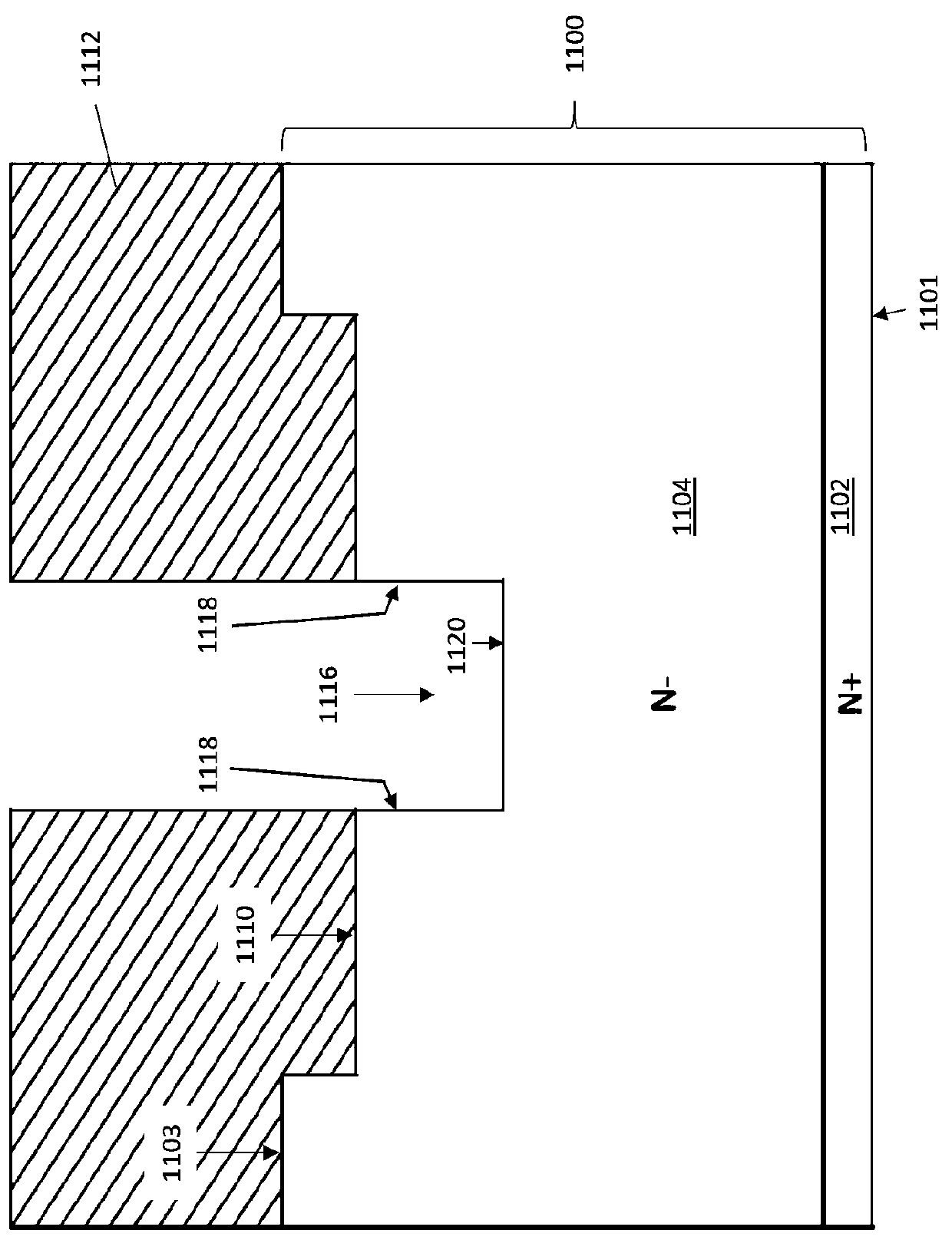

[0014] The embodiments described herein provide a power MOSFET with a reduced channel size and a good FOMg, and a corresponding manufacturing method. By introducing a spacer dielectric along the sidewall of the contact to the highly doped body contact region of the power device, the lateral dimension of the channel region can be further reduced, while the source capacitance is reduced and the highly doped body contact region and the trench are increased. The distance between road areas. The small fin-shaped part of the device body region between the contact opening / groove and the gate trench in the semiconductor substrate is connected in parallel with the contact opening / groove, thereby reducing the IV curve and DIBL (drain induced barrier drop) )swing. The highly doped body contact region is decoupled from the channel region by dielectric along the spacers of the contact opening / groove, thereby improving threshold voltage stability. The dielectric spacer also introduces stre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com