Hybrid architecture for signal processing

A technology for processing blocks, devices, applied in the direction of electrical digital data processing, special data processing applications, logic circuits using specific components, etc., can solve problems such as waste, family is not cost-effective, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

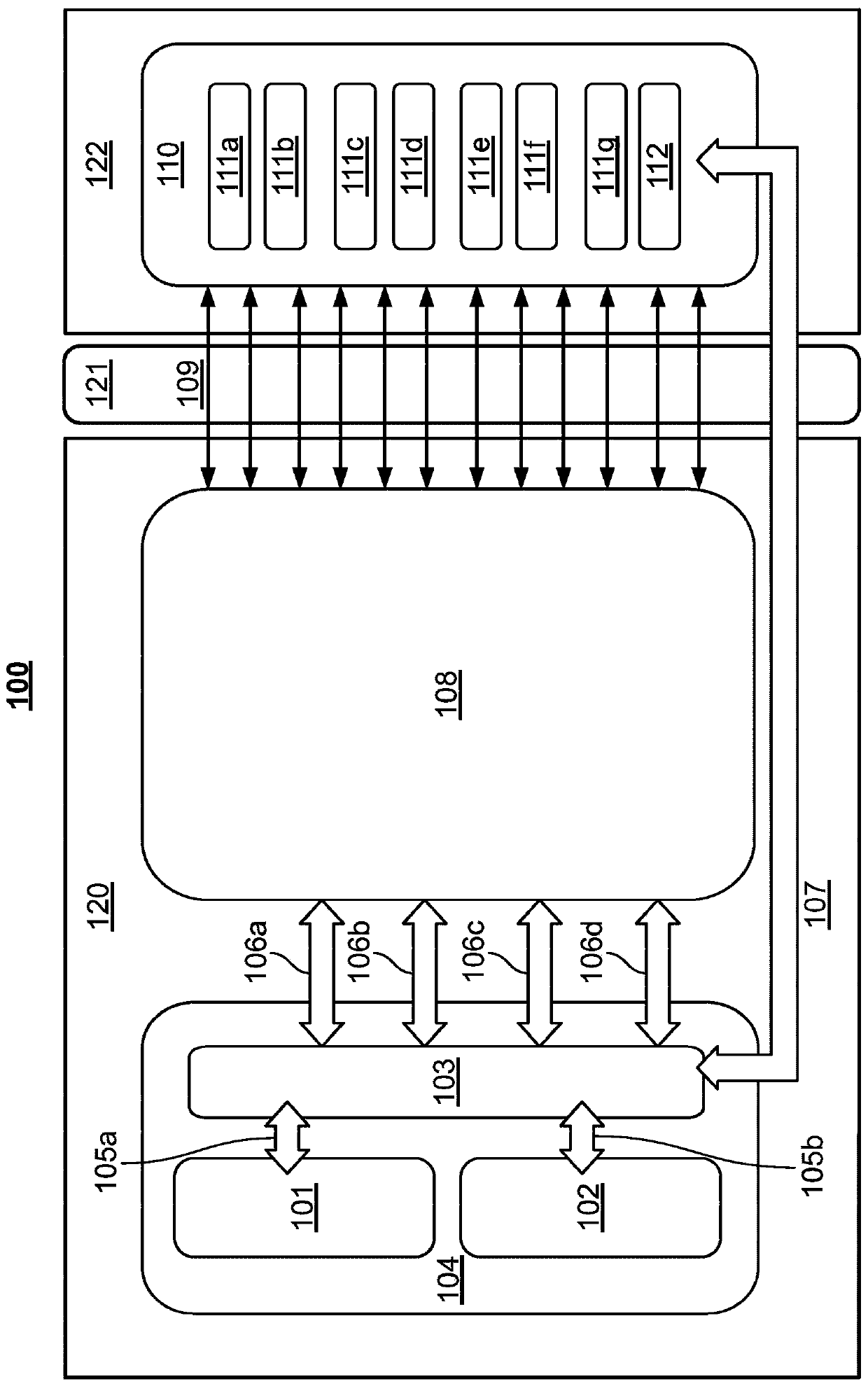

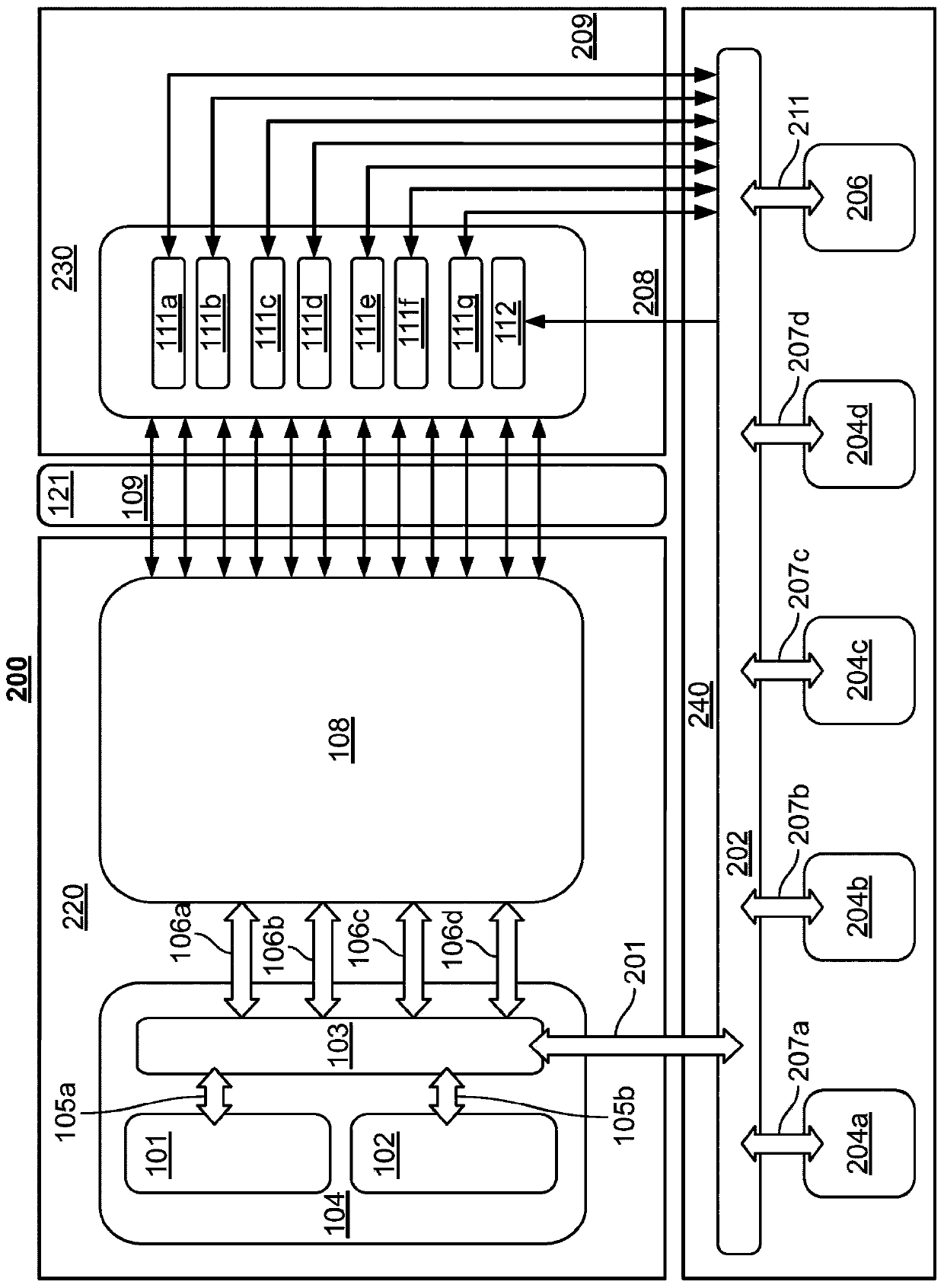

[0022] The systems and methods of the present disclosure include hybrid architectures of integrated circuits for signal processing. Different types of embedded features can operate consistently over a dedicated bus such as a Network-on-Chip (NoC) system. Additionally or alternatively, one feature can be configurably connected to another feature of the same type, thereby building a more powerful dedicated accelerator.

[0023] It can generally be desirable to create integrated circuits that are cheaper and consume less power, while being able to provide desired functionality and maintain a level of programmability. Hybrid architectures described herein include programmable architectures that are a mixture of programmable elements such as, for example, FPGAs, accelerators, and processors. Basically, the hybrid architecture described here has the low cost and low power consumption of an ASIC, but with the programmability of an FPGA.

[0024] figure 1 An illustrative floor pla...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com