Built-in self-test method and system of FPGA input and output logic module

A logic module, input and output technology, applied in the electronic field, can solve the problems of high requirements, high test cost, inconvenient test, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

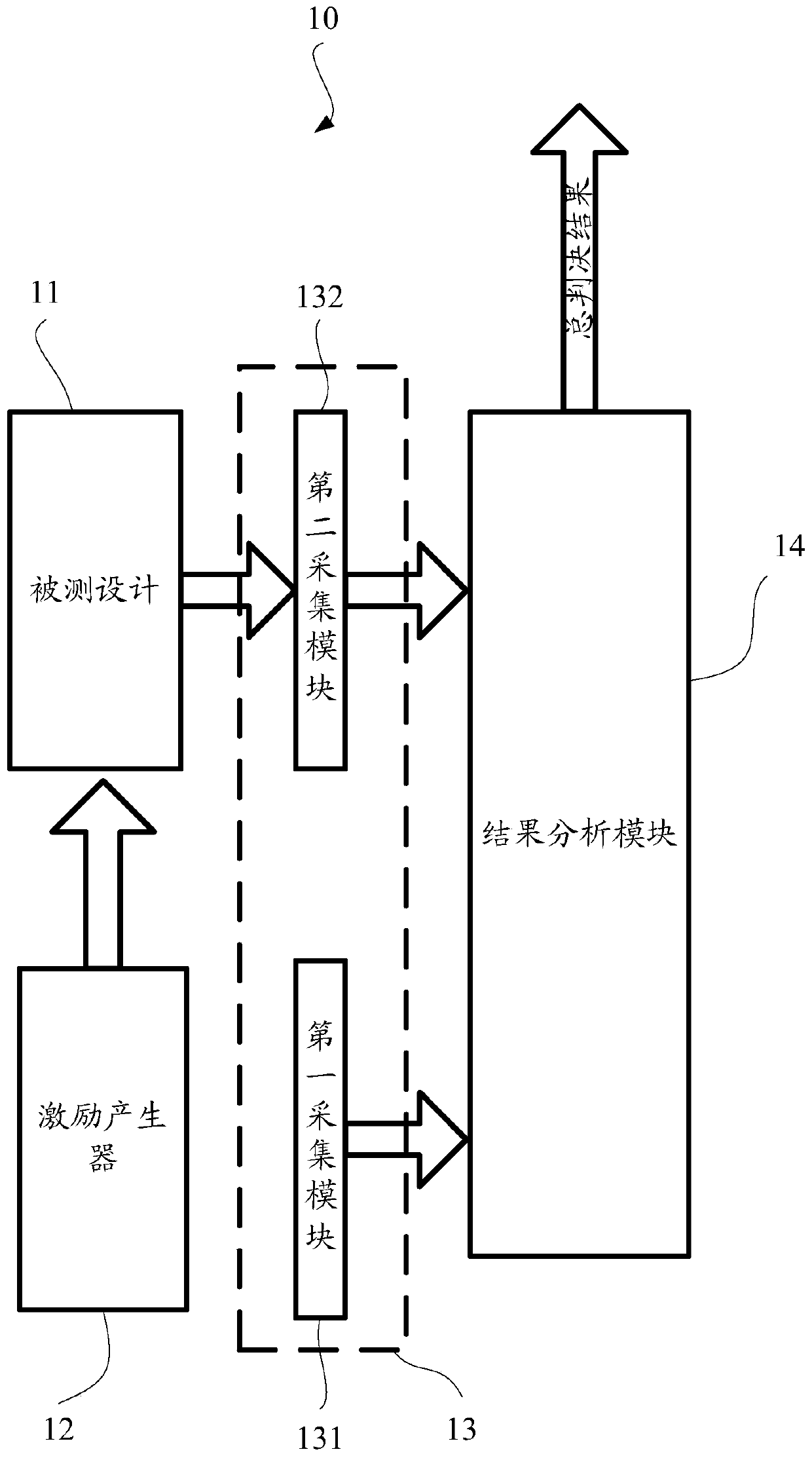

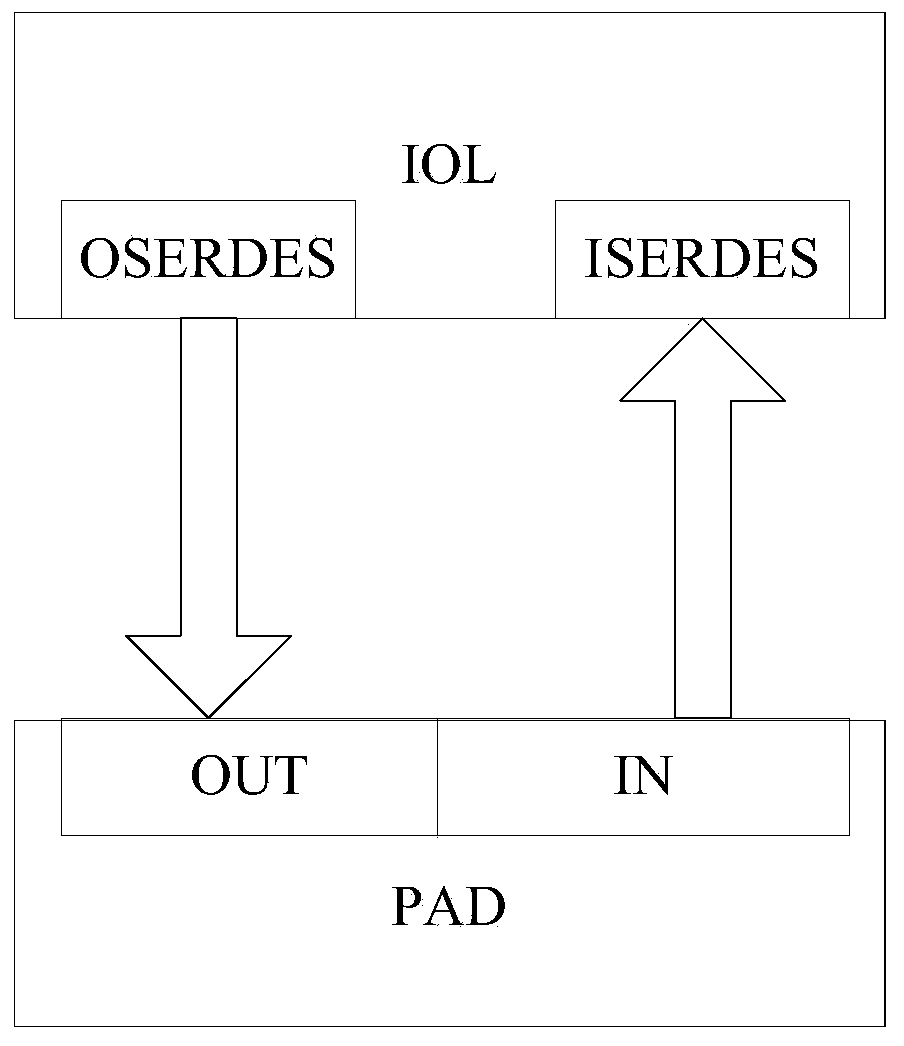

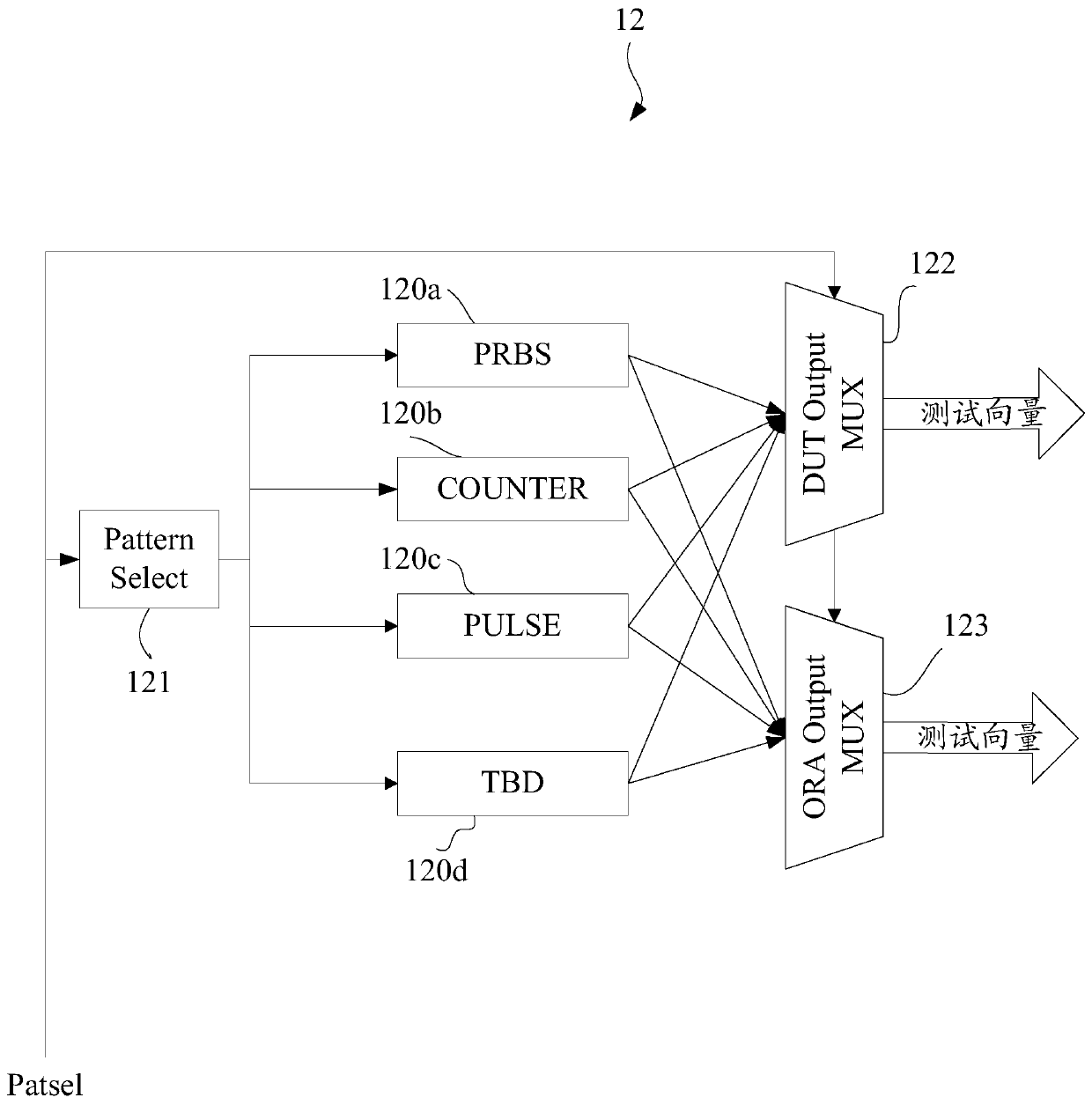

[0042] At present, the application of domestic FPGA mainly depends on the import of several international FPGA giants such as Xilinx and Altera. Domestic FPGA design has technical barriers such as difficult design, long R&D cycle, and difficult design. Especially in terms of the testing methods of each module in the FPGA testing stage, the domestic FPGA field can be said to be a blank, the main reason is that foreign giant companies have mastered the advanced technology in this area but do not disclose it to the public. There is less research, so that the technology accumulation in this area is too little, the design technology is more difficult, and important technologies cannot be broken. In order to solve the problems in the related art that the IOL test scheme relies heavily on external test equipment, the test cost is high, and the test is inconvenient, this embodiment provides a new IOL test scheme. In this IOL test scheme, a kind of FPGA IOL built-in self-test system is...

Embodiment 2

[0064] This embodiment will combine the built-in self-test system of the aforementioned FPGA input-output logic module and the IOL test structure to propose a built-in self-test method for the FPGA input-output logic module. Figure 1-6 combined on the basis of Figure 7 , Figure 7 Shown is the flowchart of the built-in self-test method of the FPGA input and output logic module:

[0065] S702: Configuring an IOL testing framework for testing the IOL in the FPGA.

[0066] The specific structure of the IOL test framework 10 has been introduced in detail above, and will not be repeated here.

[0067] It can be understood that the test scheme adopted in this embodiment is a BIST (Built-in Self Test, built-in self-test) scheme, so the IOL test framework 10 is directly implemented inside the FPGA without the participation of external test equipment : There is no doubt that the IOL of the tested design is inside the FPGA, and the excitation generator 12, the output acquisition mo...

Embodiment 3

[0085] The built-in self-test system and method of the IOL test framework, FPGA input and output logic modules provided in the aforementioned embodiments, although it can be judged whether each IOL in an FPGA is faulty, because the result analysis module is only a whole for the external test equipment The final judgment result can only indicate whether there is an IOL fault in the FPGA as a whole. Therefore, if there are IOL failures in the FPGA, the tester will not be able to determine how many and which IOL failures are in the FPGA. As a result, testers need to spend a lot of time and energy on fault location.

[0086] In order to further solve the above problems, the present embodiment also provides a new IOL test framework and a built-in self-test system of FPGA input and output logic modules, please refer to Figure 8 The IOL test architecture 80 is shown:

[0087] The IOL test structure 80 includes a design under test 81 , a stimulus generator 82 , an output acquisitio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More