Manufacturing method of interlayer film

A manufacturing method and interlayer film technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems affecting device performance, metal residue, cost increase, etc., to avoid electrical performance, eliminate metal residue, no The effect of metal residue

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

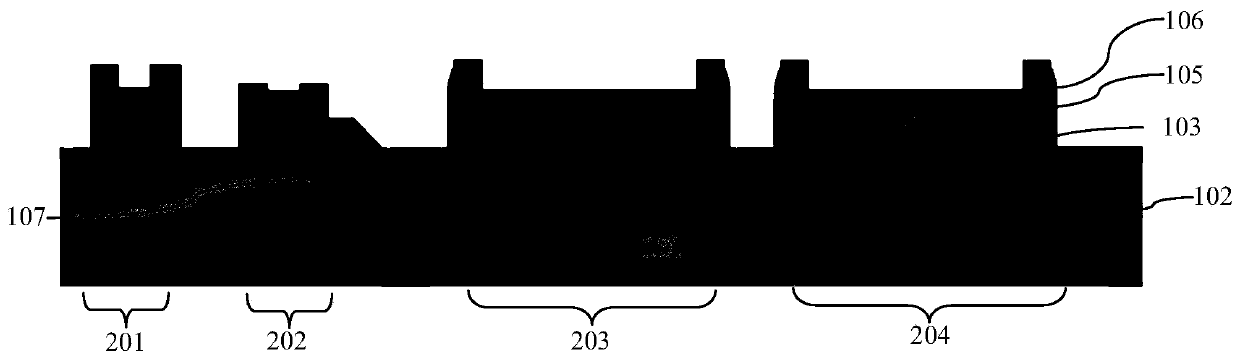

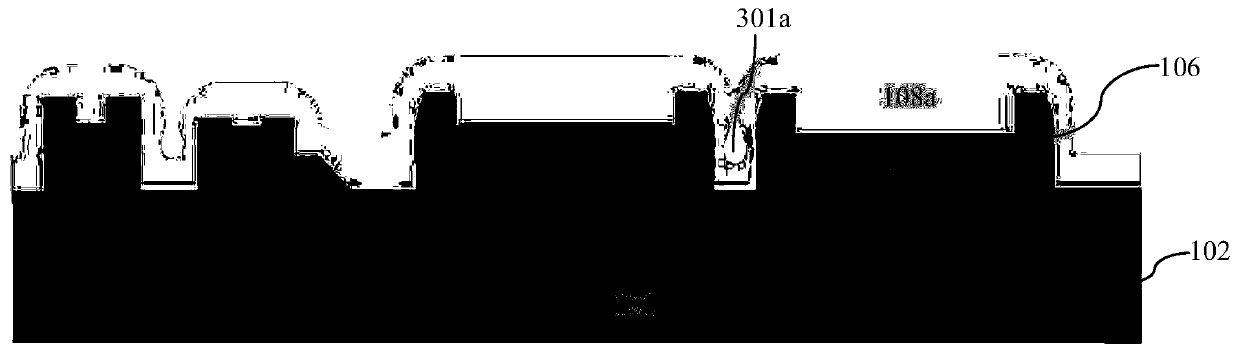

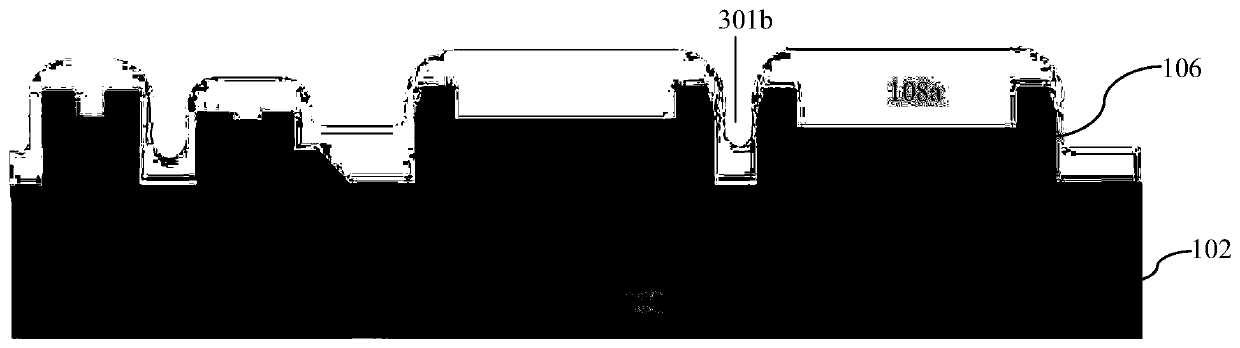

[0060] Such as figure 2 Shown is the flow chart of the manufacturing method of the interlayer film in the embodiment of the present invention; as Figure 3A to Figure 3D As shown, it is a device structure diagram in each step of the method of the embodiment of the present invention. The method for manufacturing the interlayer film of the embodiment of the present invention includes the following steps:

[0061] Step 1, such as Figure 3A As shown, a semiconductor substrate 1 is provided, on which pattern structures of semiconductor devices are formed, and the regions between the pattern structures are pattern spacers.

[0062] In the embodiment of the present invention, the semiconductor substrate 1 is a silicon substrate.

[0063] The semiconductor device is a MOS transistor with HKMG. The interlayer film is the zeroth interlayer film. Usually, the semiconductor device will form multiple layers of metal, wherein the metal layers of each layer need to be isolated by an in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More