High-performance data packet caching method and device based on hierarchical storage

A data packet, high-performance technology, applied in electrical components, transmission systems, etc., can solve problems such as restricting off-chip memory performance, immature technical limitations, and long design cycles, to ensure high-speed data processing capabilities, improve storage performance, The effect of solving data congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

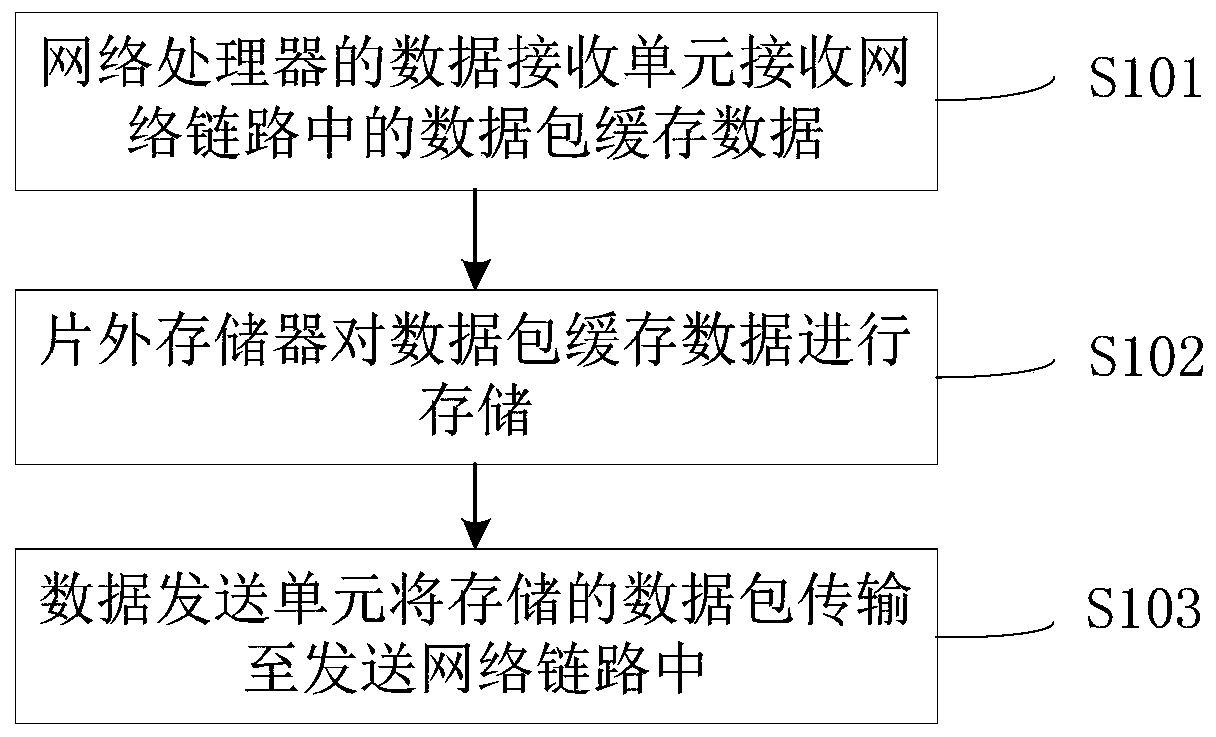

[0030] Such as figure 1 As shown, this embodiment provides a high-performance data packet caching method based on hierarchical storage, including the following steps:

[0031] S101. The data receiving unit of the network processor receives the packet buffer data in the network link;

[0032] S102. The off-chip memory stores the data packet cache data: when storing the data packet, it does not start storing from the starting address of the space allocated by the network processor system, but reserves space for the header of the data packet. After the network processor modifies the data packet header according to the network protocol, it stores it in the reserved space, and stores the entire data packet at the same time;

[0033] The storage data packet adopts a three-level storage method, including an input level, a cache level and an output level; the input level writes high-speed data packets in the network link, and the cache level stores large blocks of data packets to com...

Embodiment 2

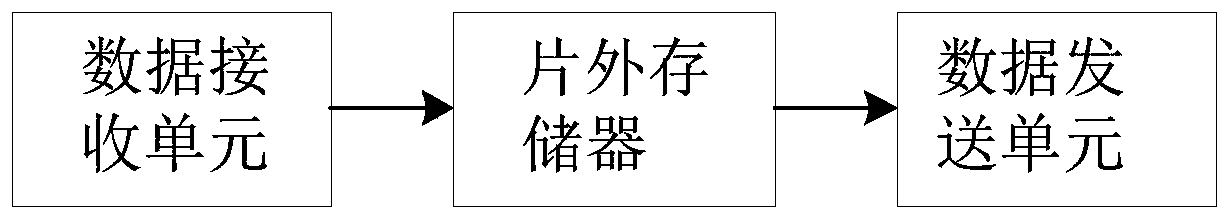

[0036] Such as figure 2 As shown, this embodiment provides a high-performance data packet buffer device based on hierarchical storage, including a data receiving unit, an off-chip memory, and a data sending unit; the data receiving unit is used to receive data packets in a network link Cache data; the off-chip memory is used to store data packet cache data: after modifying the data packet header, store it in the reserved space, and store the entire data packet at the same time; the data sending unit is used to The stored data packets are transferred to the sending network link.

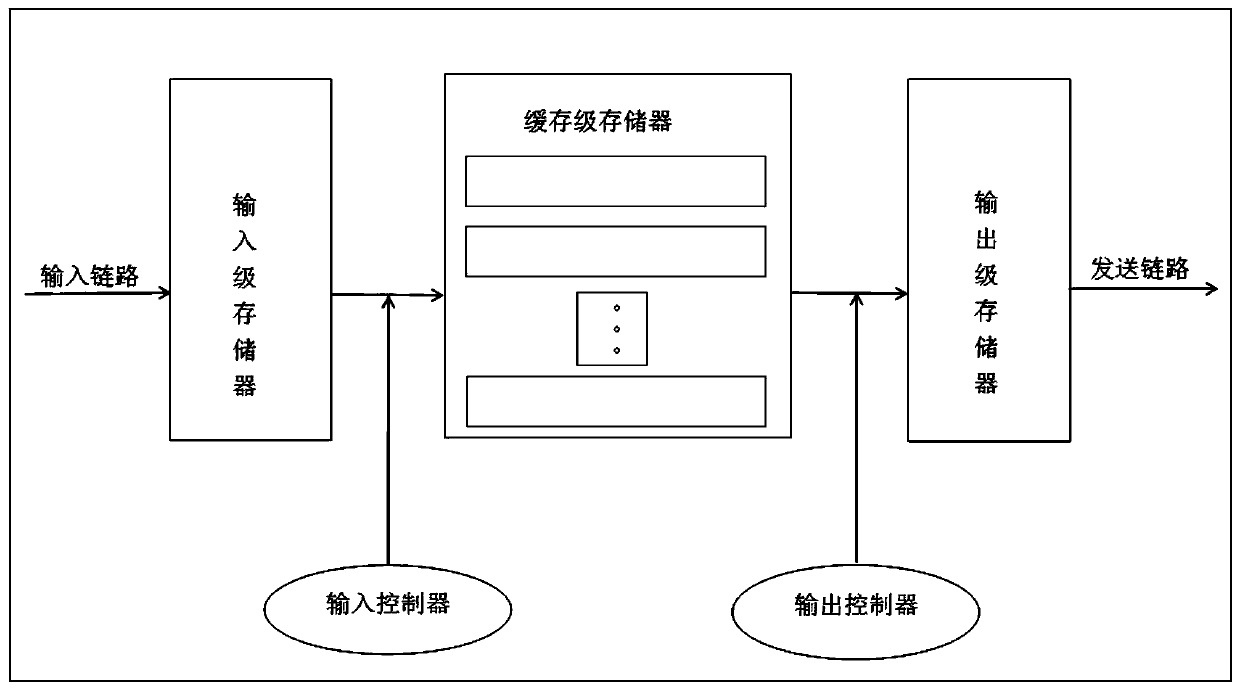

[0037] Such as image 3 As shown, the off-chip memory includes sequentially connected input-level memory, cache-level memory and output-level memory; the input-level memory is used to write high-speed data packets in network links, and the cache-level memory is used to store large block data packets, the output-stage memory is used to write out high-speed data packets. Both the input-level memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More