Multi-channel high-speed sampling data synchronous calibration method based on FPGA

A high-speed sampling and data synchronization technology, applied in the direction of analog/digital conversion calibration/test, analog/digital conversion, analog-to-digital converter, etc., can solve the problems of increased software workload, increased hardware cost, narrow adjustment range, etc., to achieve Reduce the follow-up software workload, reduce hardware costs, and wide adjustment range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

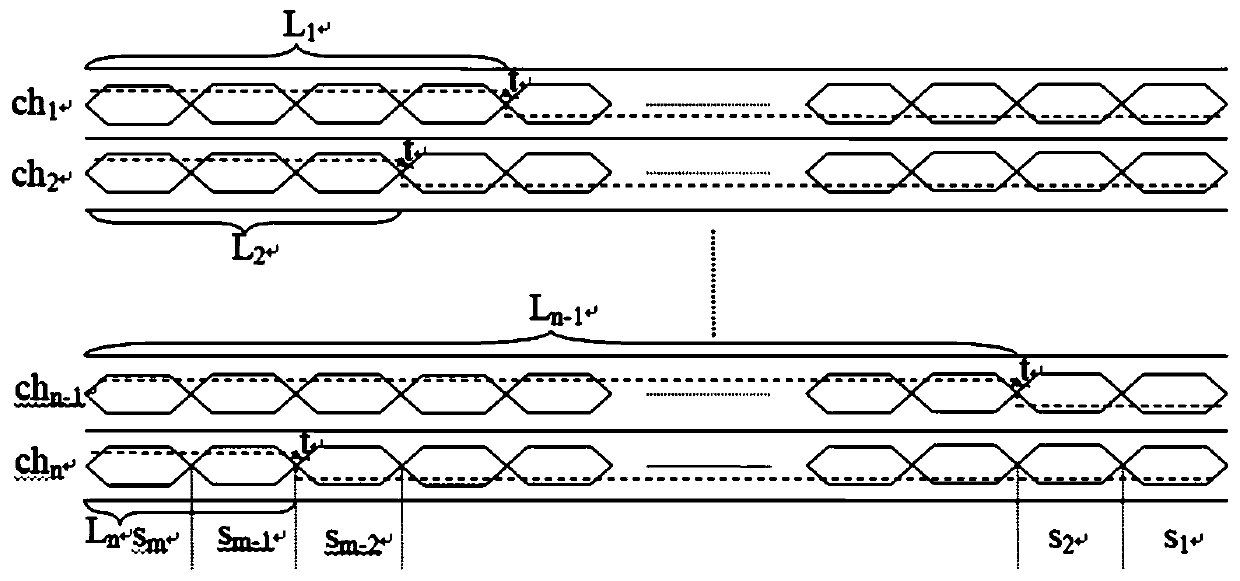

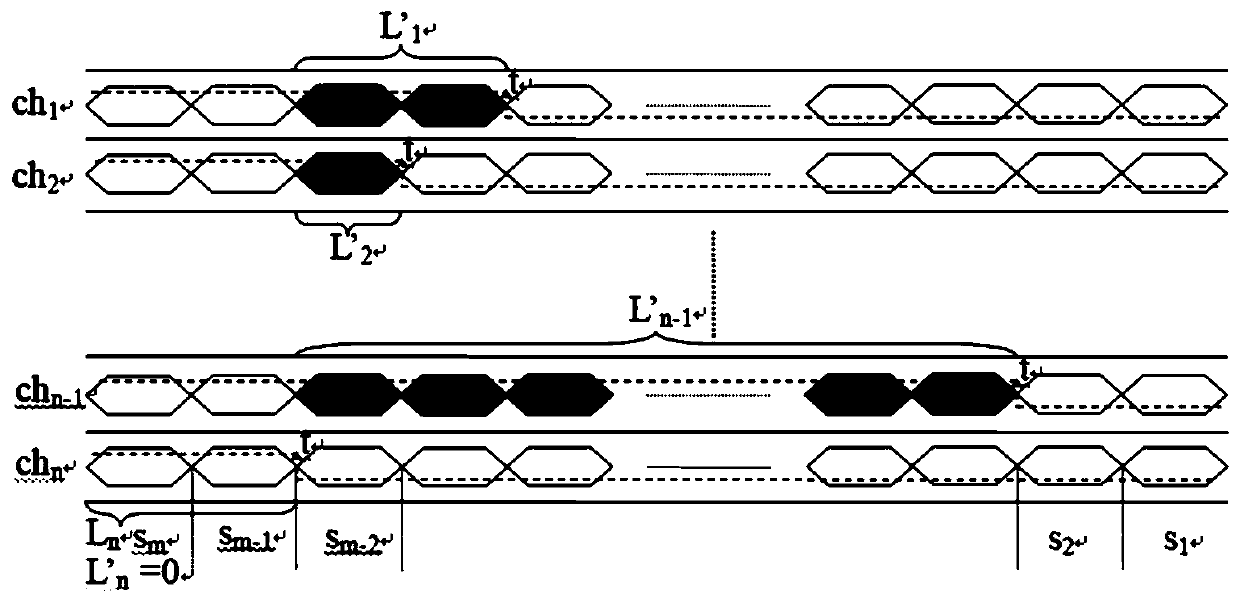

[0048] The present invention is a multi-channel high-speed sampling data synchronous calibration method based on FPGA, which is specially designed for the inter-channel data synchronization problem of multi-channel high-speed acquisition. Because FPGA is currently used as an ADC data processing device, most of the data collected by high-speed ADC needs to The processing, analysis or storage transmission is directly performed in the FPGA, so realizing synchronous calibration of multi-channel sampling data in the FPGA, so that the sampling data between channels is completely synchronized will bring great benefits to the subsequent signal processing in the FPGA. The method unit of the present invention directly receives high-speed ADC sampling input to the high-speed data of the FPGA interface, and then establishes a channel FIFO buffer in the FPGA,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More