Double-T-shaped nano gate and preparation method thereof

A nanometer and gate cap technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of high parasitic capacitance of dielectric-assisted T-type nanometer gates, reduce gate parasitic capacitance, avoid inverted gates, reduce Effects of Parasitic Capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049]In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0050] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

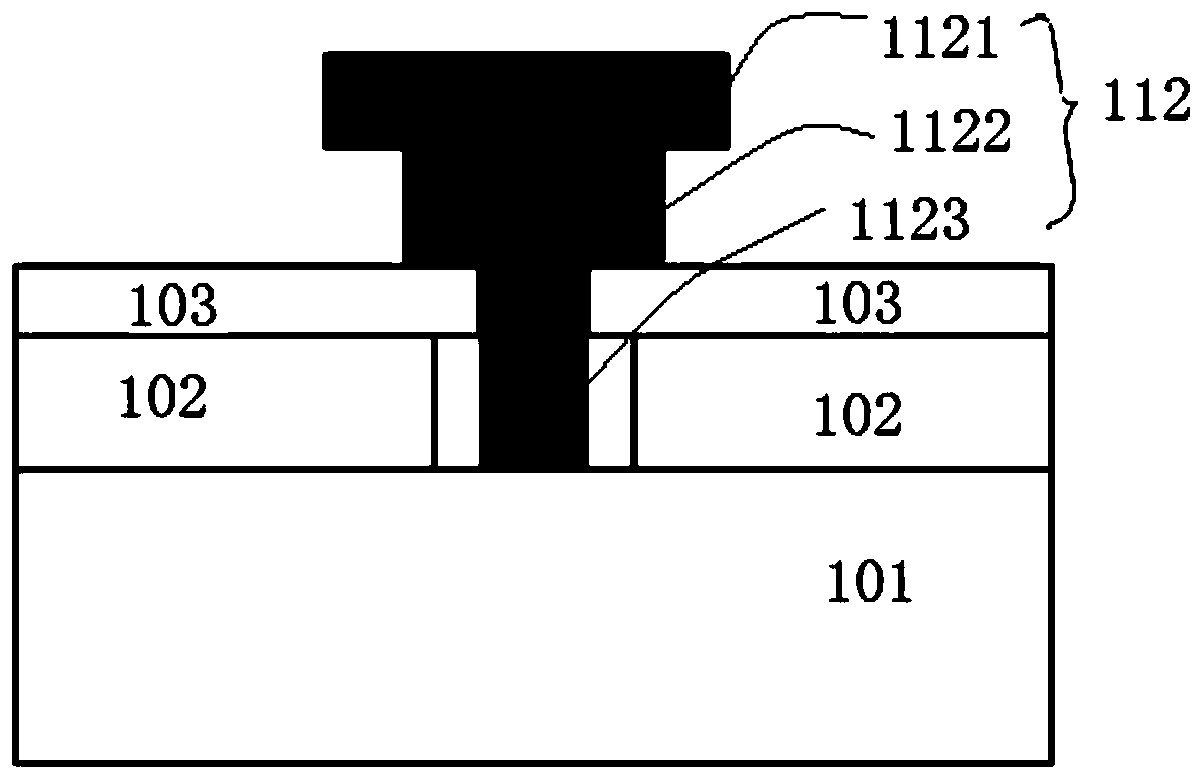

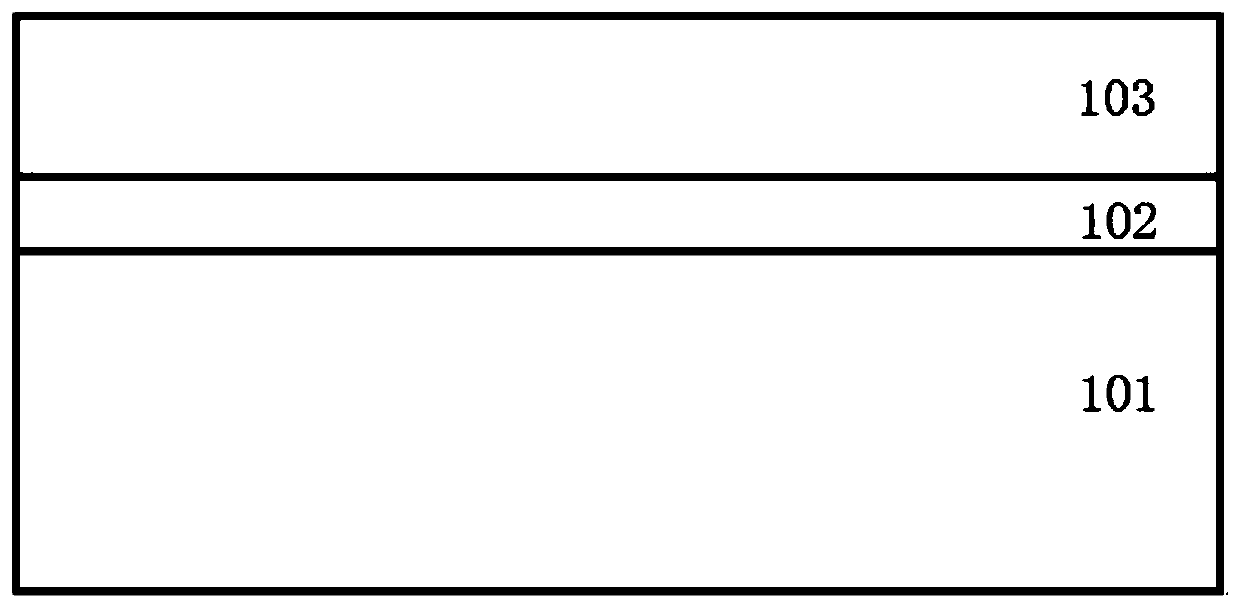

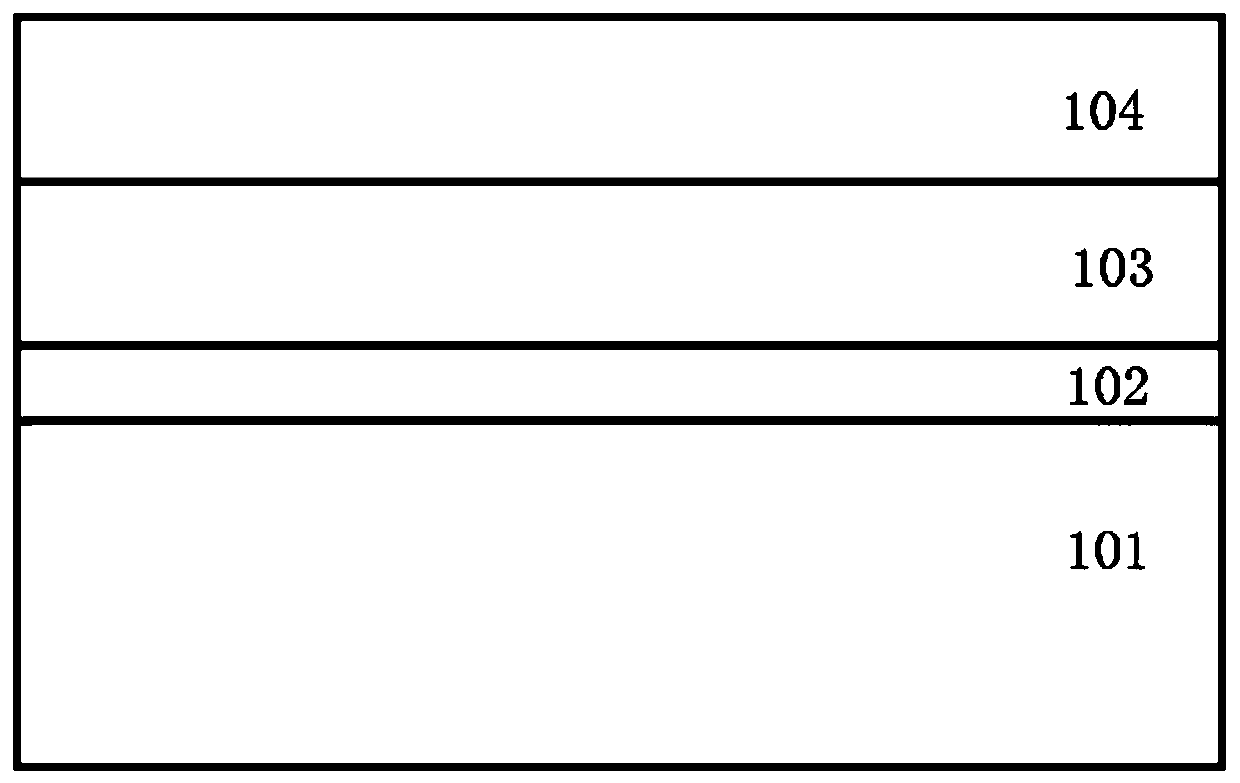

[0051] For an example, see figure 1 , the embodiment of the present invention provides a double T-shaped nano-gate 112, including a grid cap 1121, a grid waist 1122 and a grid root 1123, the width of the grid cap 1121 is greater than the width of the grid waist 1122, and the width of the grid waist 1122 is greater than The width of the grid root 1123 . The double T-shaped nano-gate 112 is grown on the substrate 101, and the bottom dielectric passivation layer 102 and the top diele...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More