Patents

Literature

43 results about "Nano grid" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

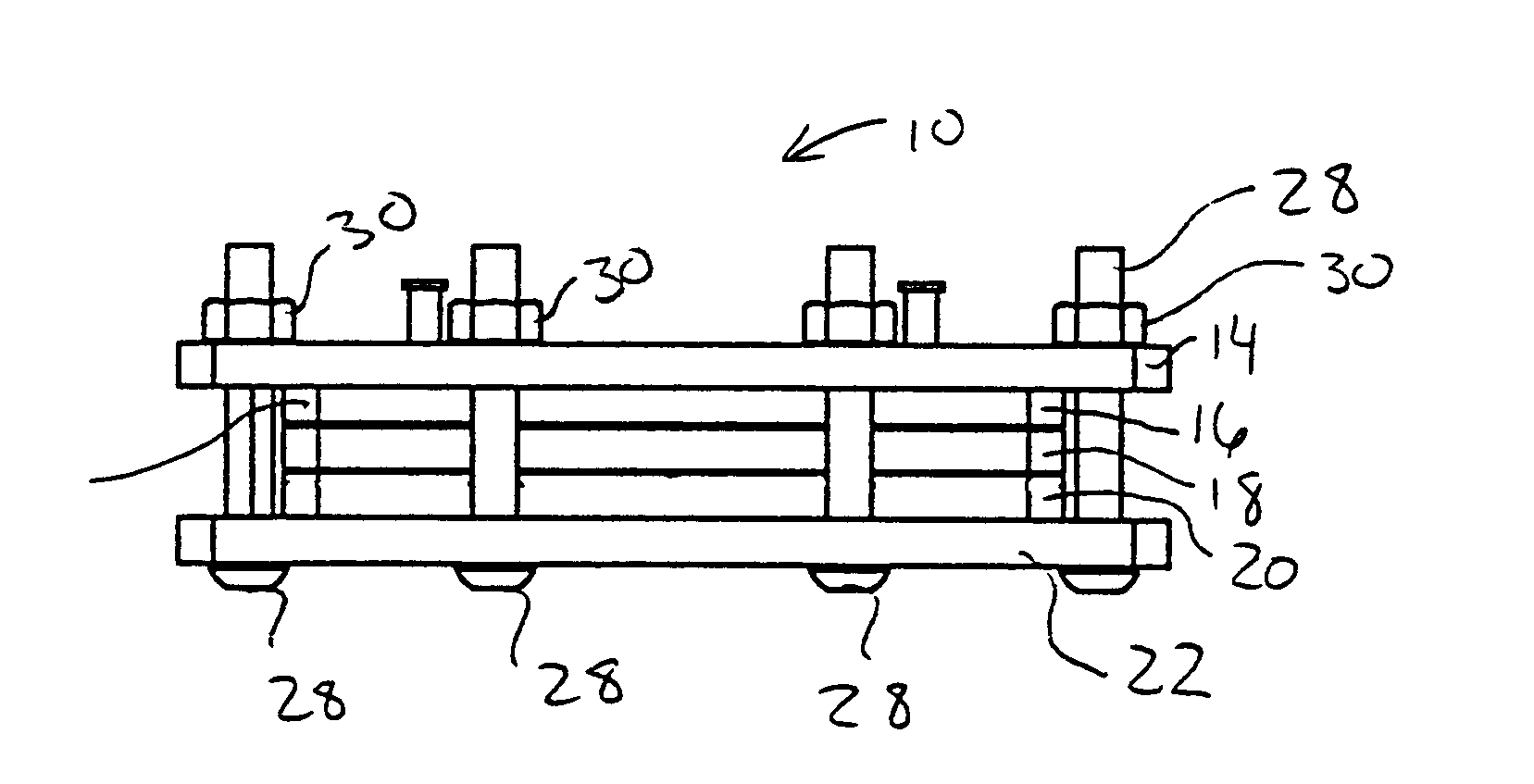

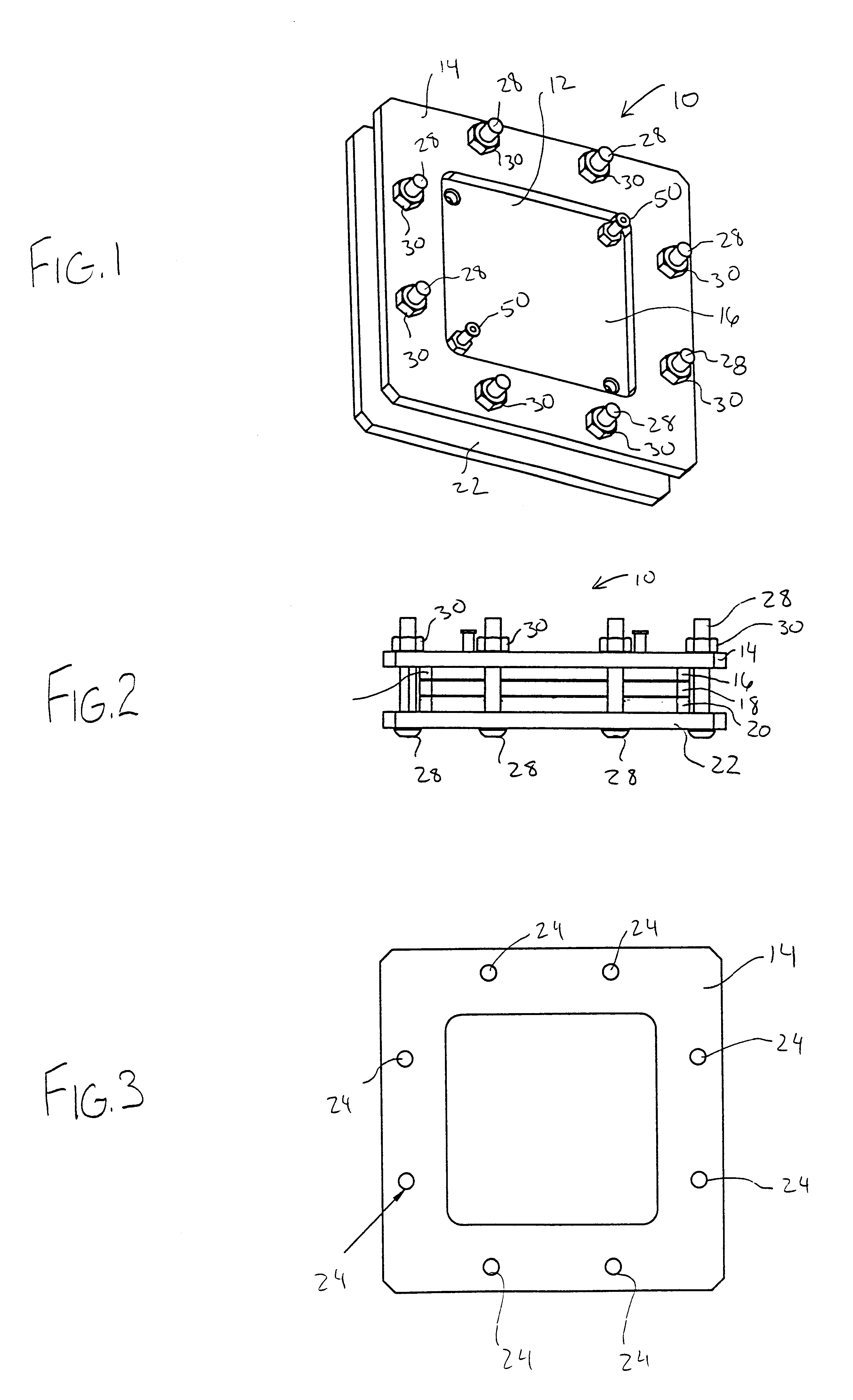

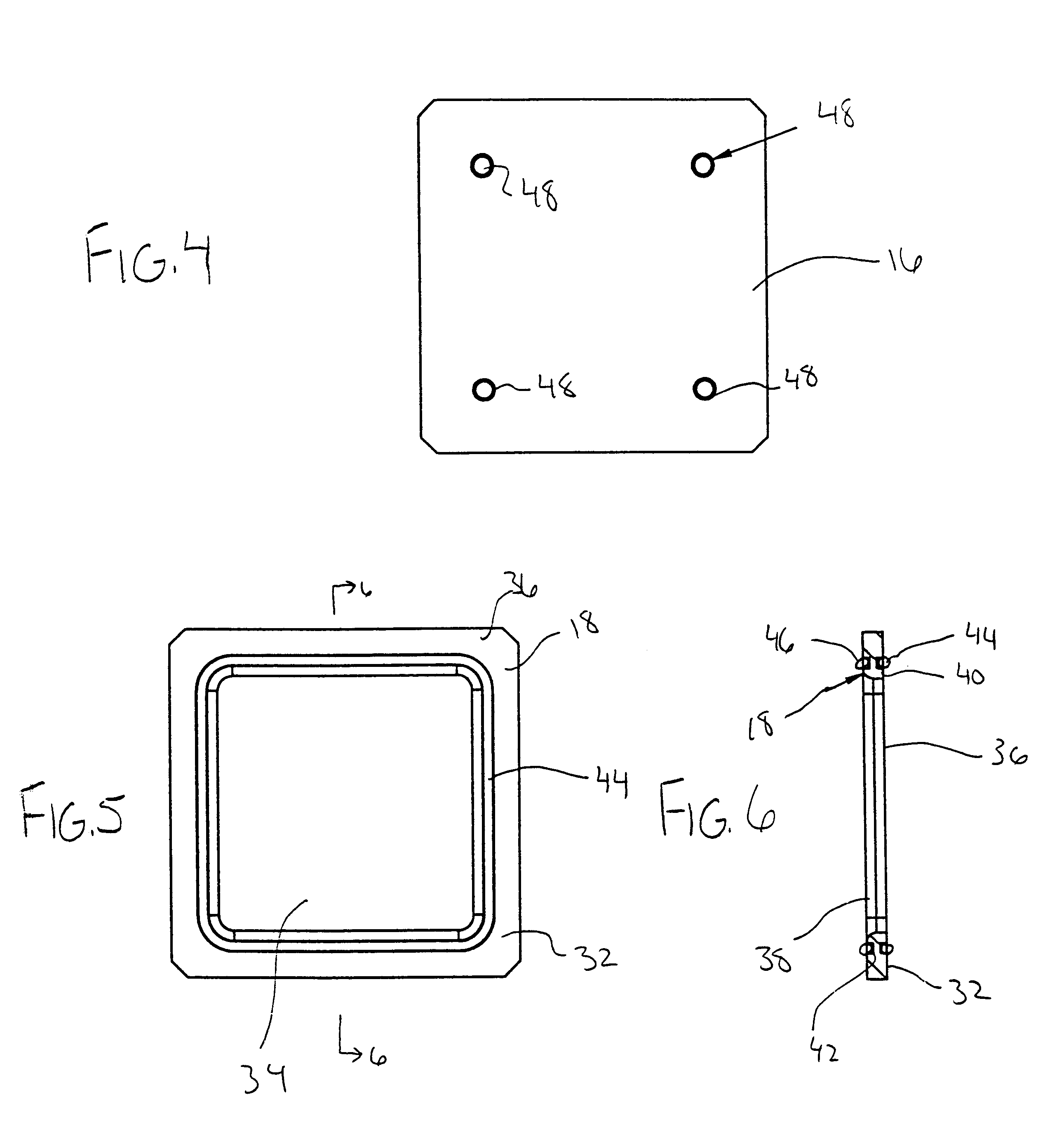

Nano-grid micro reactor and methods

InactiveUS6309889B1Prevent and reduce chanceBioreactor/fermenter combinationsSequential/parallel process reactionsPressure systemPositive pressure

The invention provides exemplary devices and methods to facilitate the performance of assays. In one embodiment, one such device comprises a holding member having a top surface, a bottom surface, and a plurality of holding locations that are adapted to hold at least one article, such as a solid support and / or a cell. When within the holding locations, the articles are preferably disposed below the top surface. A membrane is positioned above the top surface of the holding member, and a pressure system is provided to apply positive pressure to the membrane to force the membrane against the top surface of the holding member. In this way, a seal may be provided between the holding locations.

Owner:GLAXO GROUP LTD +1

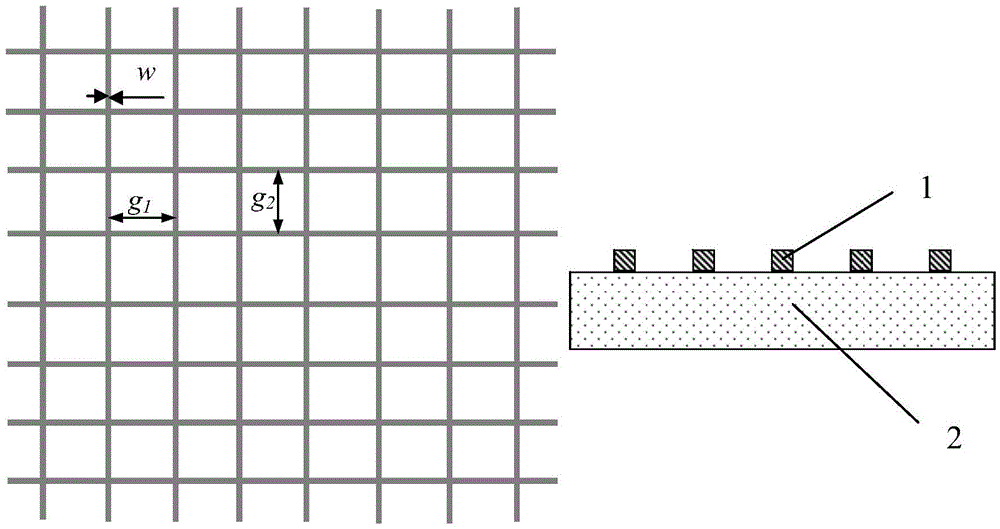

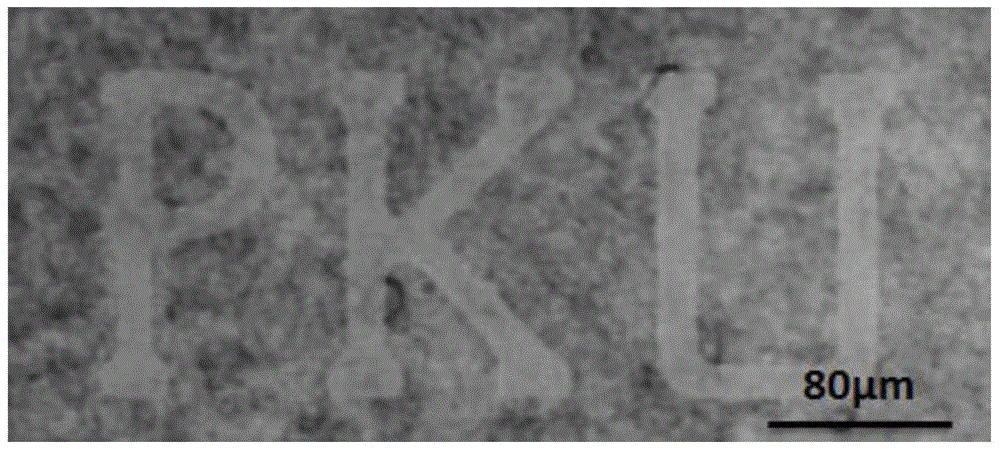

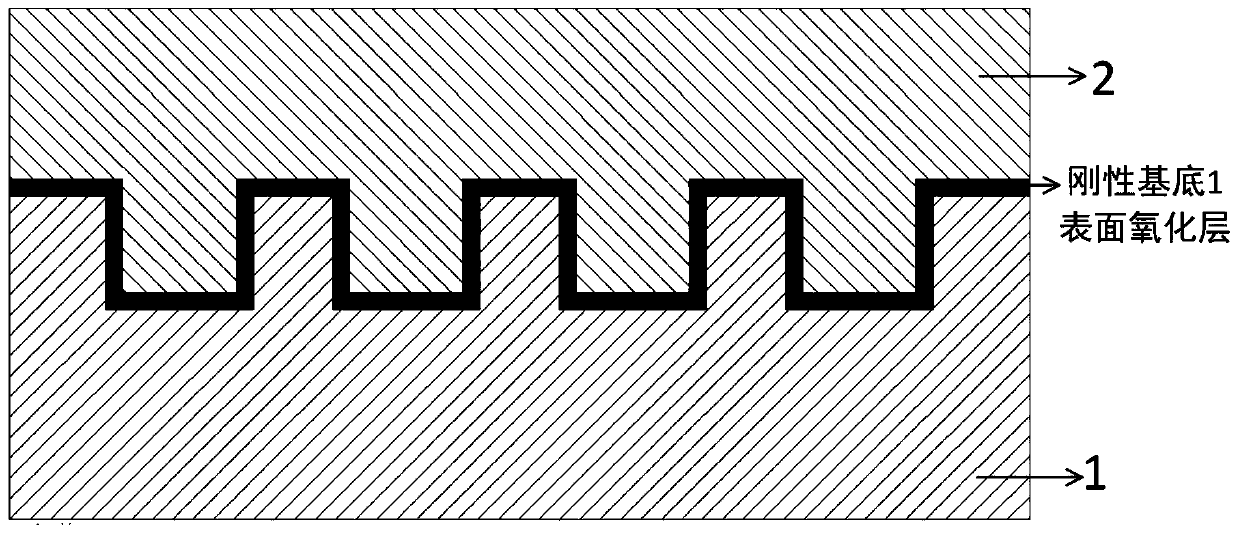

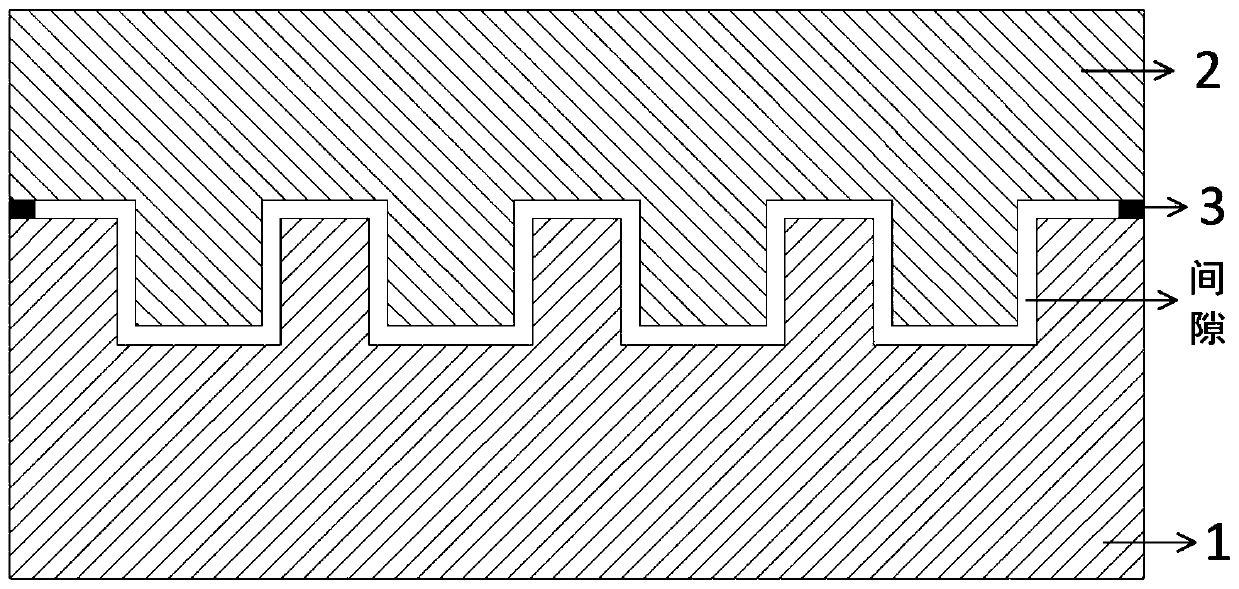

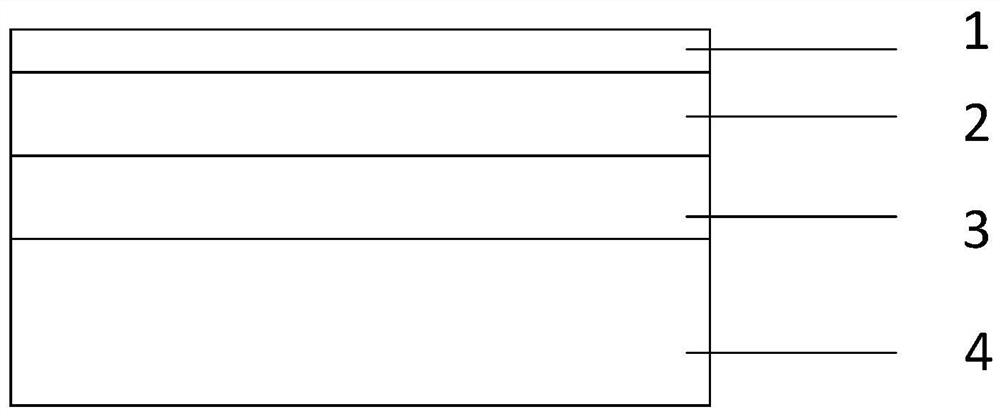

Transparent electrode based on metal nanometer grid and preparing method of transparent electrode

InactiveCN104485279ASimple methodMature technologySemiconductor/solid-state device manufacturingSemiconductor devicesGrid patternOptical transmittance

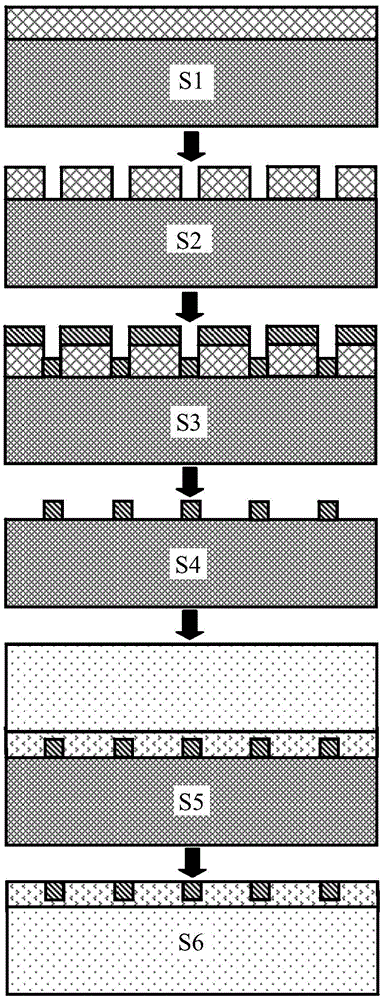

The invention relates to a preparing method of a transparent electrode based on a metal nanometer grid. The method comprises the following steps that (1) photoresist coats a silicon substrate in a spin-coating way and is baked; (2) exposure and development are carried out, and the photoresist is etched into a nanometer grid pattern on the silicon substrate; (3) a metal layer is deposited on the photoresist of the nanometer grid pattern; (4) the photoresist is removed through stripping, and a metal nanometer grid formed on the silicon substrate is obtained; (5) bonding agents coat the metal nanometer grid in a spin-coating way, and in addition, a transparent substrate is adhered and cured; (6) the silicon substrate is removed through corrosion, and the transparent electrode based on the metal nanometer grid arranged on the transparent substrate is obtained. The method is simple, the implementation is easy, the integration and the large-scale production are easily realized, and the electrical conductivity and the light transmittance of the prepared transparent electrode are controllable.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

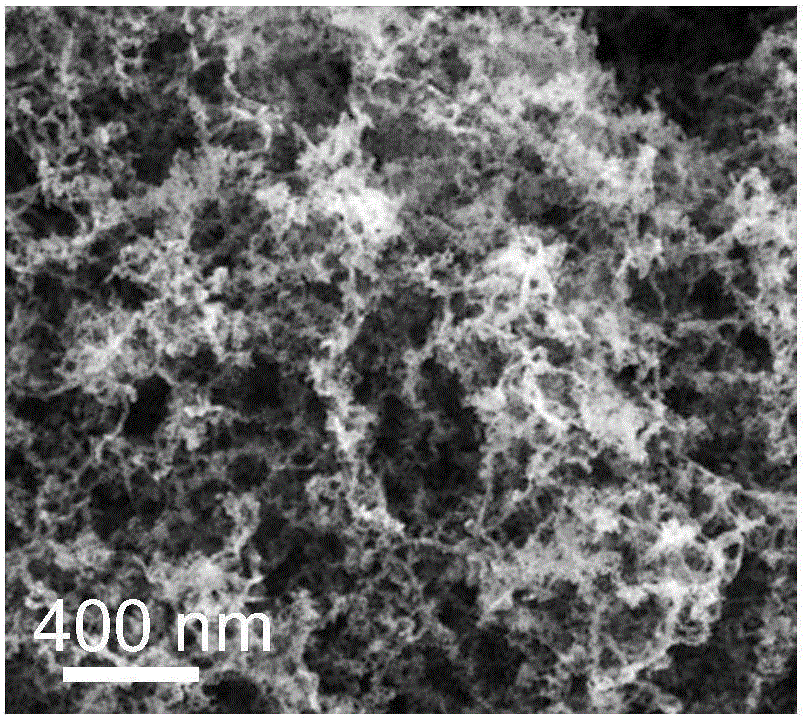

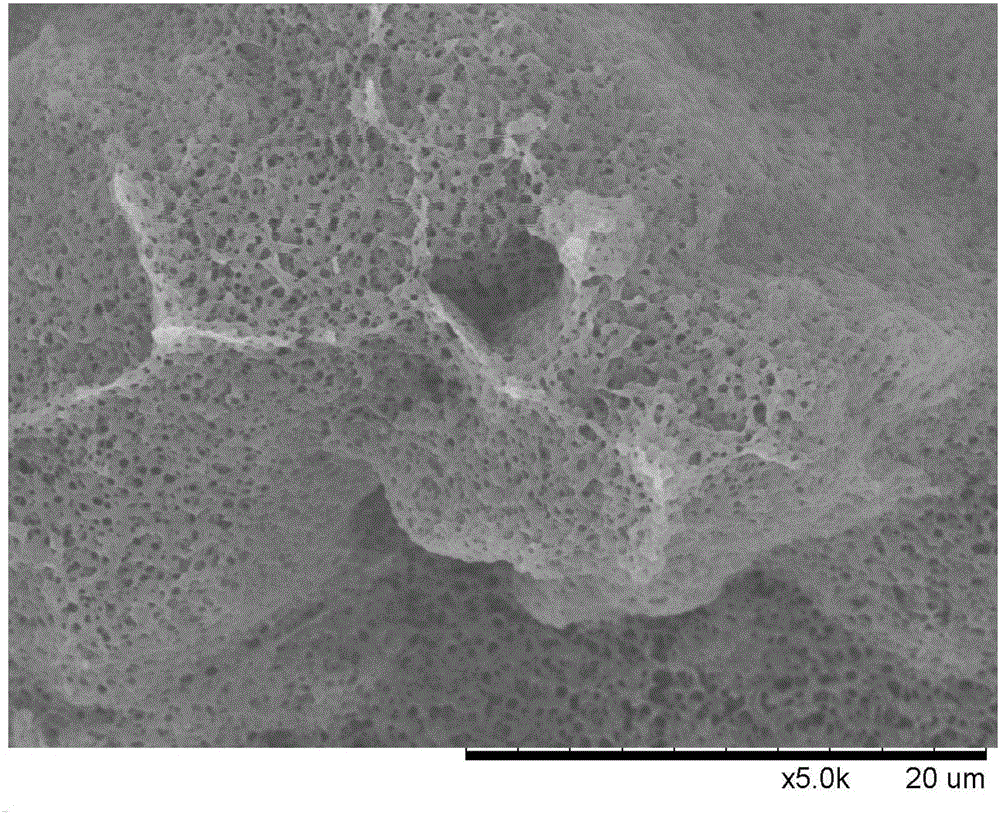

Phenolic resin/silicon dioxide composite aerogel materialand preparation method thereof

ActiveCN106189066ANo sheddingNo separabilityBulk chemical productionThermal insulationNanoscopic scale

The invention provides a phenolic resin / silicon dioxide compositeaerogel material and a preparation method thereof. The phenolic resin / silicon dioxide composite aerogel material has a nano-grid structure in which a silicon dioxide phase and a resin phase are mutually tangled. The phenolic resin / silicon dioxide composite aerogel material is prepared from a material containing an organic silicon precursor, a phenolic compound, an aldehyde compound and chitosan by virtue of a sol-gel method and supercritical carbon dioxide. According to the composite aerogel material, an organic phase and an inorganic phase are respectively continuous nano-scale tangle structures and are integrated with the mechanical property of organic aerogel and the thermal insulation property and fire resistance of silicon dioxide aerogel; and after the composite gel material with a thickness of 1cm is impacted by the 1300-DEG C flame of a blast burner for over 30 minutes, the falling and the separation of the inorganic phase are not caused, and meanwhile, the temperature of a protected side does not exceed 300 DEG C. The preparation method has the beneficial effects that the operation is simple, the reaction is safe and reliable, and the thermal insulation property and the fire resistance of the material can be regulated and controlled by simply changing the material proportion.

Owner:UNIV OF SCI & TECH OF CHINA

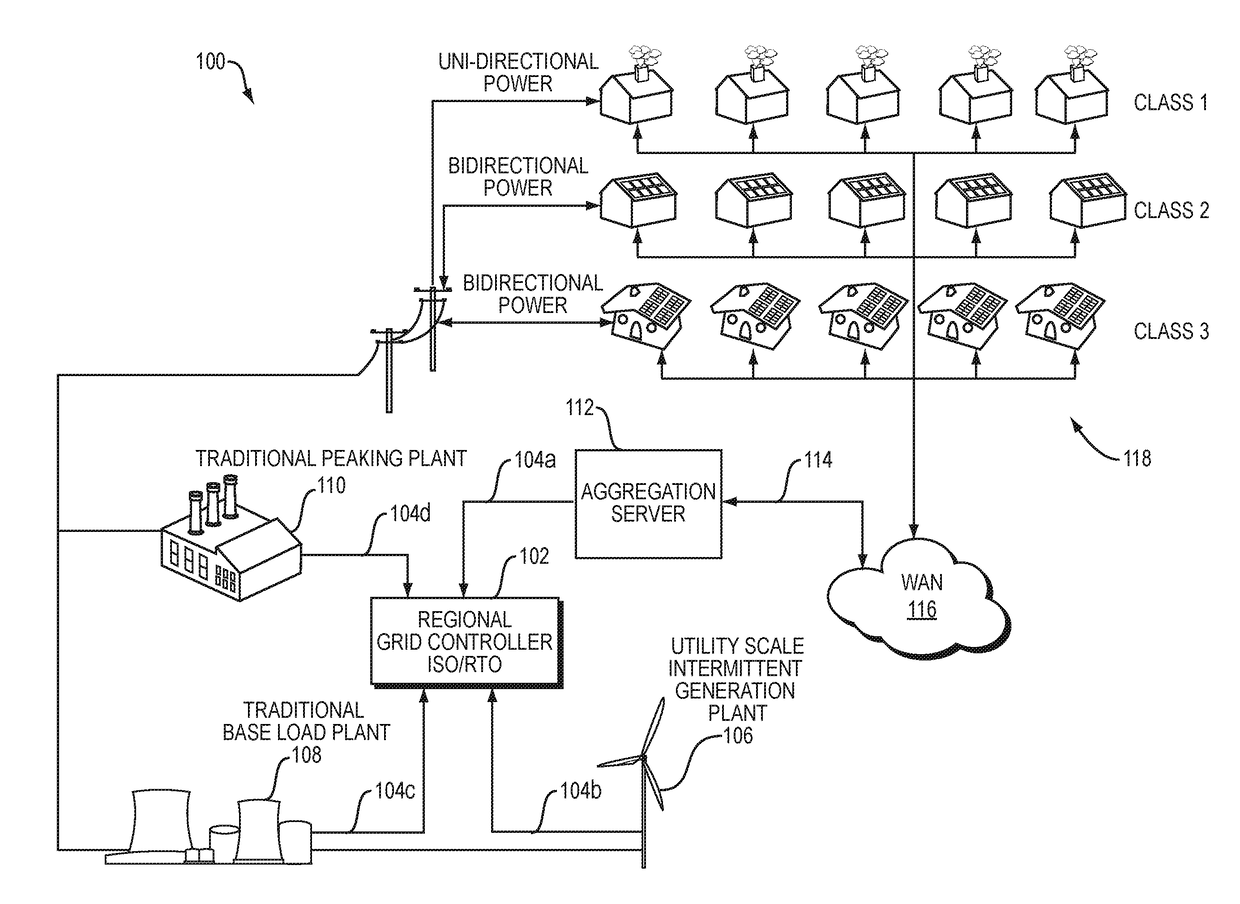

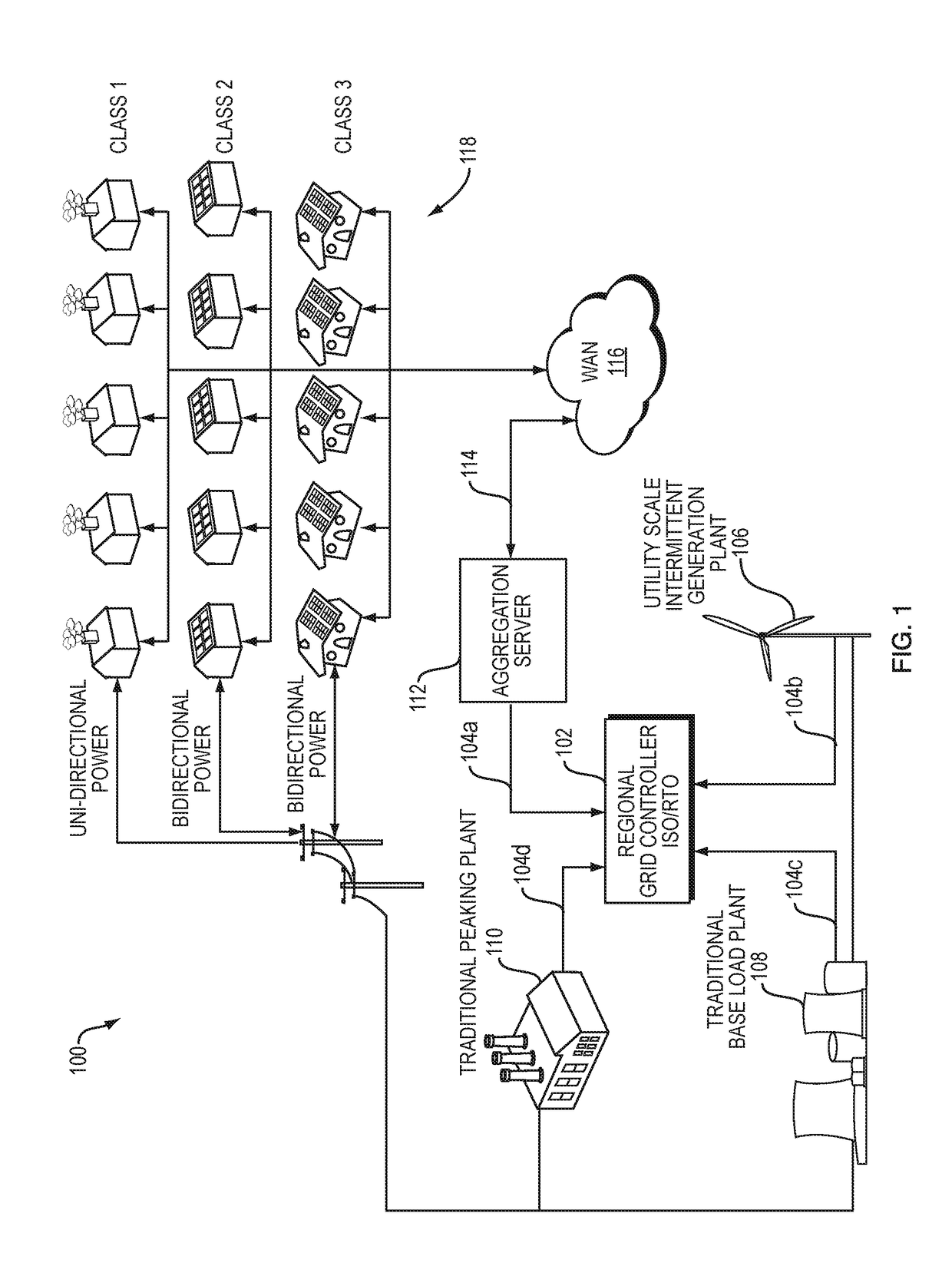

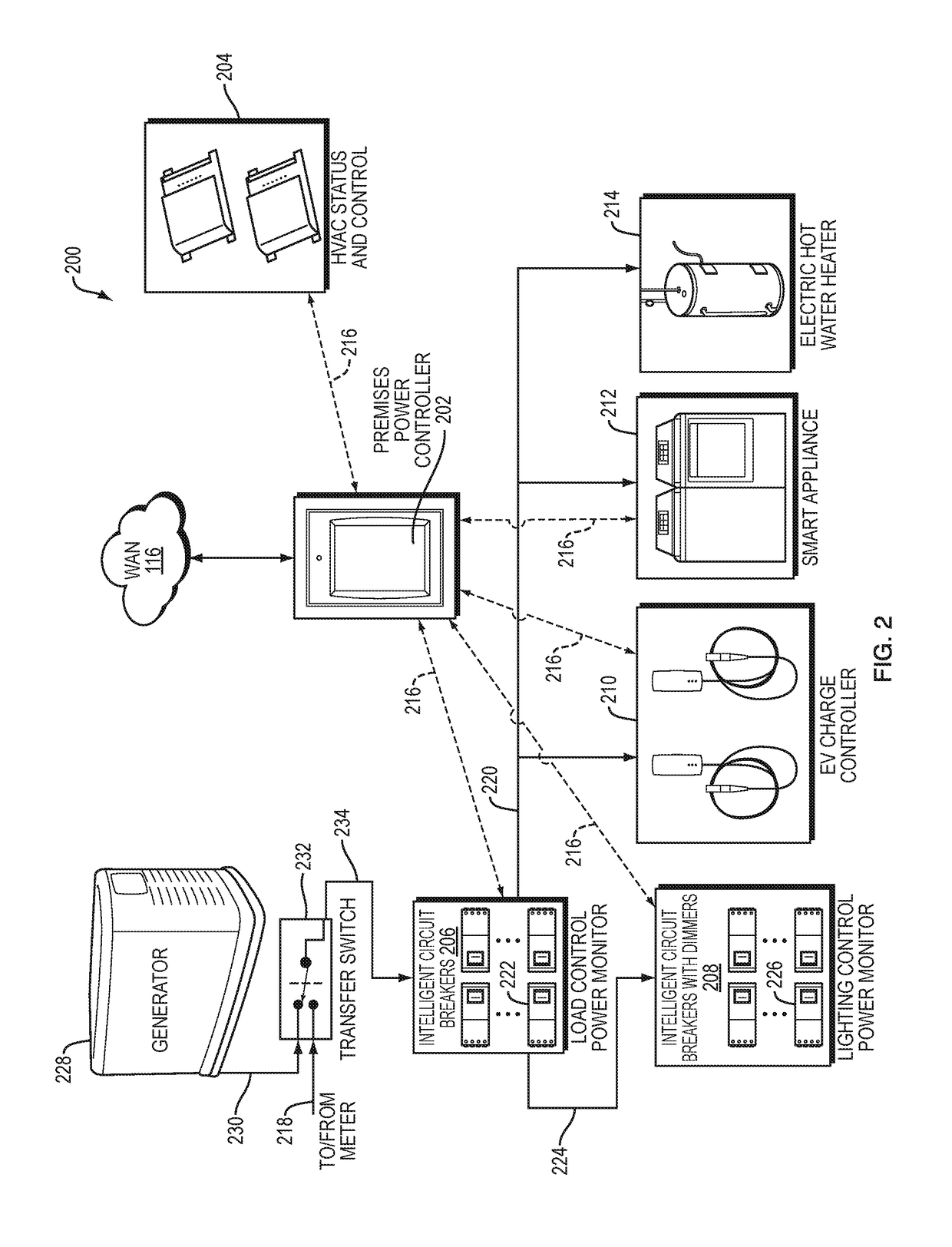

System and methods for creating dynamic NANO grids and for aggregating electric power consumers to participate in energy markets

ActiveUS20180075548A1Reduce loadReduce power consumptionPower network operation systems integrationElectric ignition installationPower controllerPeaking power plant

A group of homes, businesses, or other electric power consuming premises are aggregated and commonly controlled to dynamically reduce loads in sufficient quantities, and with sufficient rapidity and duration, to participate as a market participant in the energy markets including participating as a peaking power plant. While the amount of reduced power consumption for a single premises is typically quite small, the total reduced consumption of an aggregation of just a few thousand homes or businesses may be on the order of hundreds of kilowatts. A premises power controller in conjunction with intelligent circuit breakers, which may include dimmers, enable dynamic management of individual loads in each premises.

Owner:SAVANT SYST INC

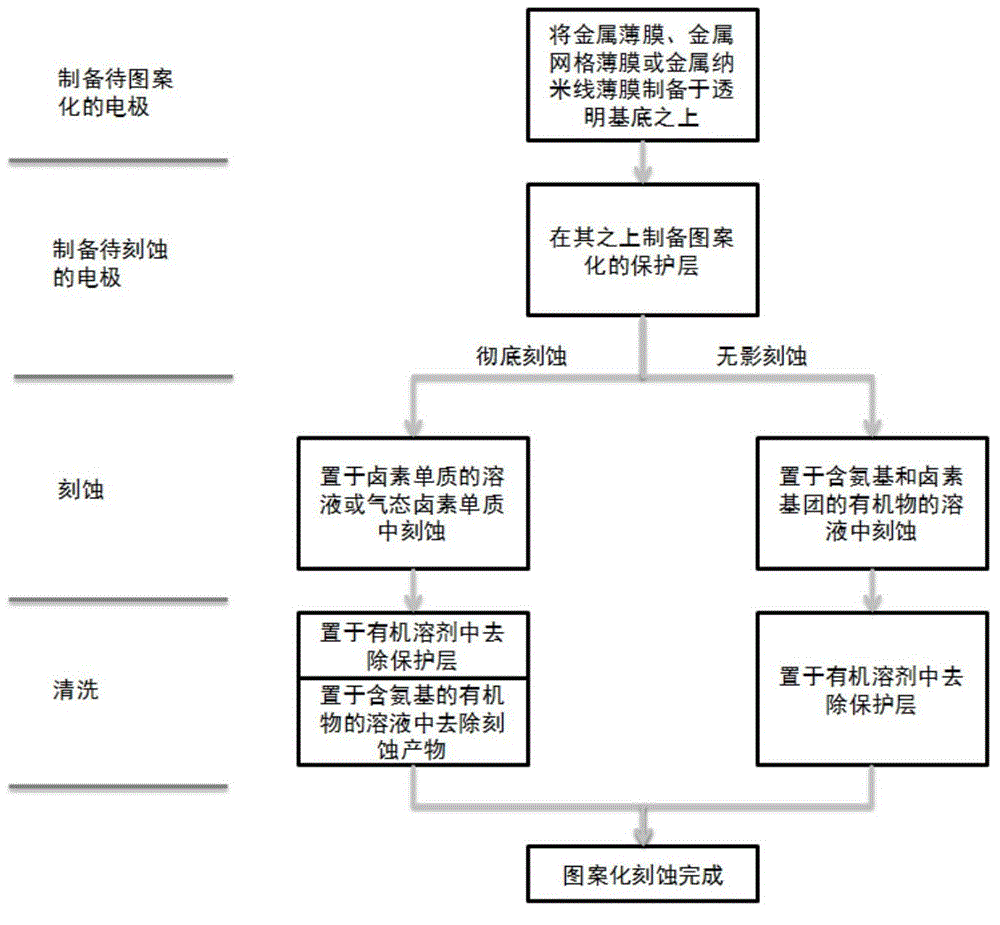

Patterning etching method of transparent conducting electrode and patterning transparent conducting electrode

ActiveCN104575869ALow costEtching speed is fastMaterial nanotechnologyConductive layers on insulating-supportsEtchingMetal nanowires

The invention discloses patterning etching method of a transparent conducting electrode and a patterning transparent conducting electrode. The method comprises the steps that an electrode to be patterned is manufactured; a patterning protecting layer is prepared on the electrode; the electrode is placed in etching liquid or gas for etching; and the electrode is placed in washing liquid, and etching products and the protecting layer are washed off. The method is used for carrying out latticed patterning on metal nanowires, and the latticed patterning transparent conducting electrode is manufactured. Metal or a metal nanowire film is subjected to quick, low-cost, safe and low-toxic chemical etching through gas or low-concentration etching liquid, complete etching can be achieved, shadowless etching can be achieved, safety and low-toxic performance are achieved, etching speed is high, and effect is obvious in practical application. A prepared latticed patterning transparent conducting electrode comprehensive nanowire and a nanometer lattice transparent electrode have the advantages that under the premise that conductivity loss is very small, transparency is greatly improved, and performance is good.

Owner:PEKING UNIV

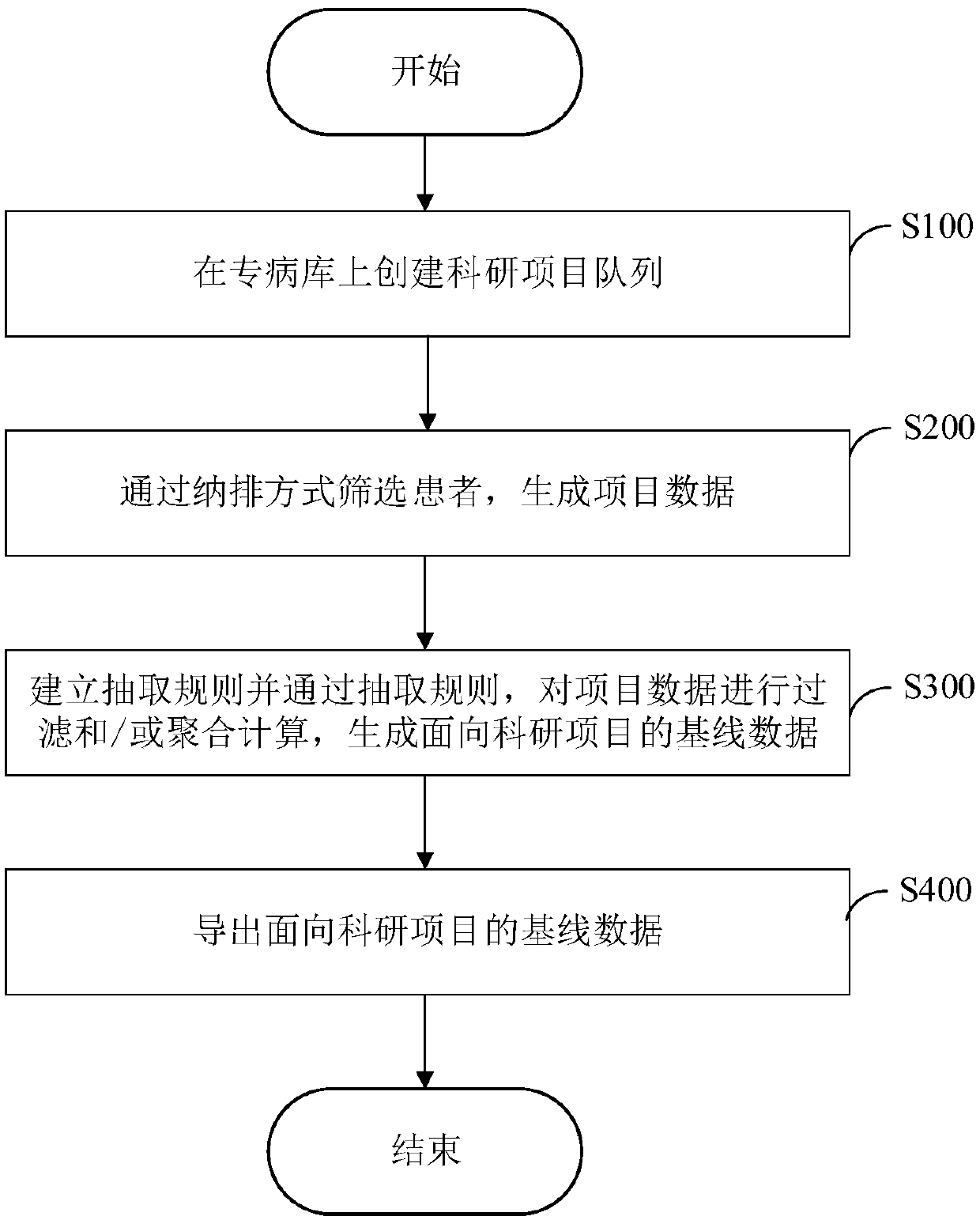

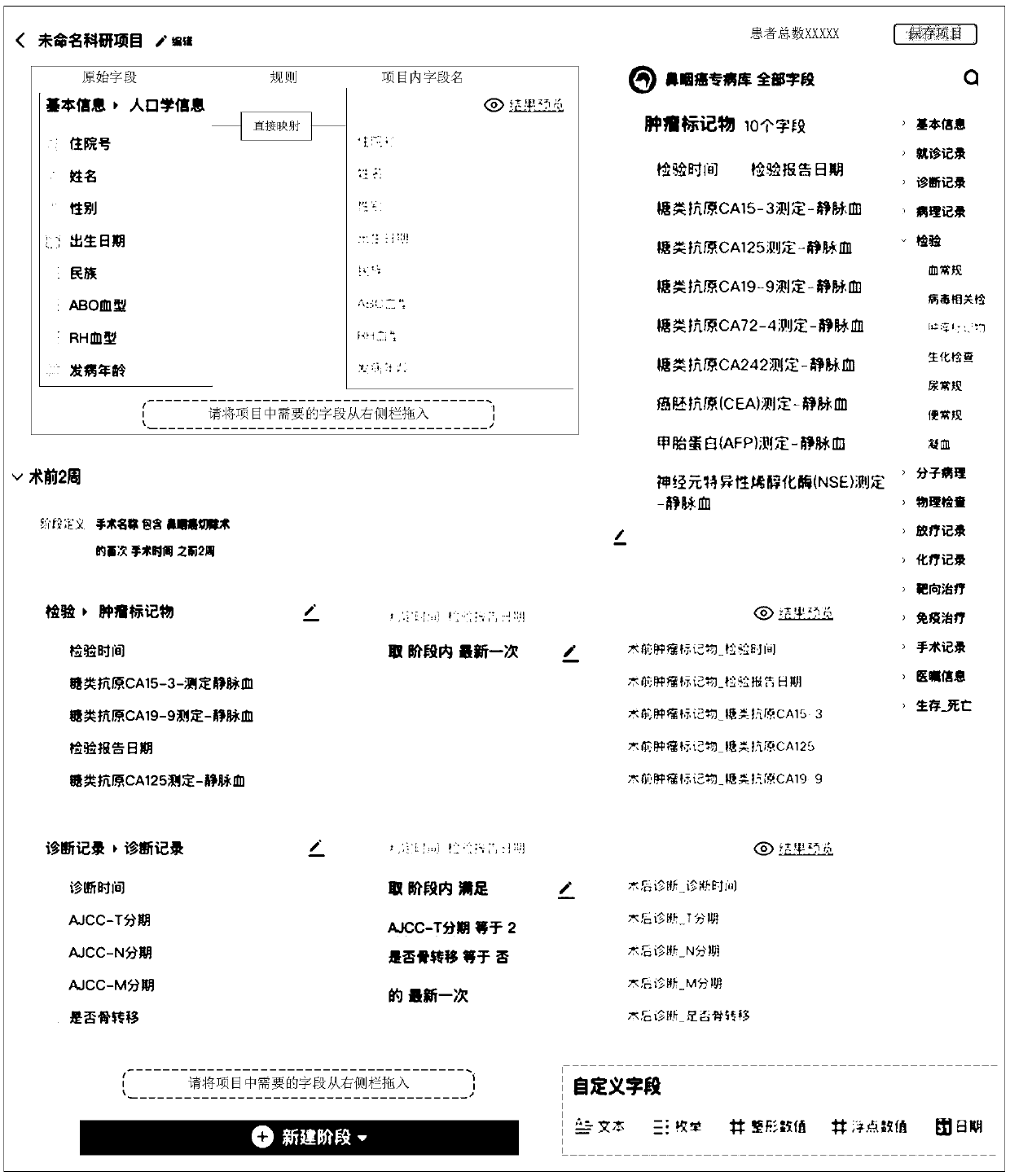

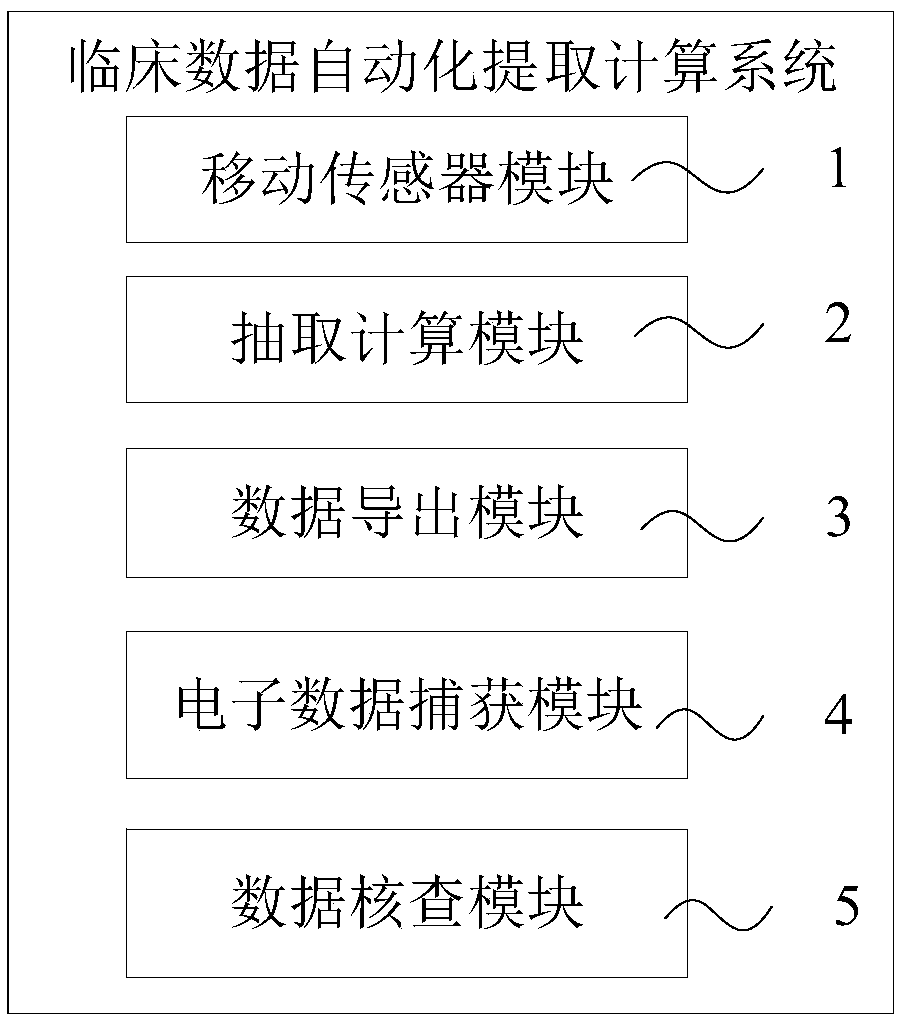

Clinical data automatic extracting and calculating method, system and device and storage medium

ActiveCN109524120AImprove collection efficiencyImprove accuracyMedical data miningBaseline dataData set

The invention provides a clinical data automatic extracting and calculating method, system and device and a storage medium. The method comprises the following steps of: establishing a scientific research project queue on a special disease database, wherein clinical data of a special patient is stored in the special disease database; screening patients by adopting a nano-grid mode to generate scientific research project data, wherein the scientific research project data comprises screened clinical data of the patients; establishing an extraction rule and performing filtering and / or aggregationcalculation on the scientific research project data through the extraction rule to generate baseline data for the scientific research project, wherein the baseline data for the scientific research project comprises scientific research target fields required by a plurality of scientific research projects, and finally deriving the baseline data for the scientific research project. Under a conditionof an existing objective clinical full data set, according to the technical scheme, by the adoption of the clinical data automatic extracting and calculating method, system and device and the storagemedium, automatic extraction and calculation of the specific data required by CRF for clinical test or research are achieved, and the efficiency and accuracy of specific clinical data acquisition areimproved.

Owner:YIDU CLOUD (BEIJING) TECH CO LTD

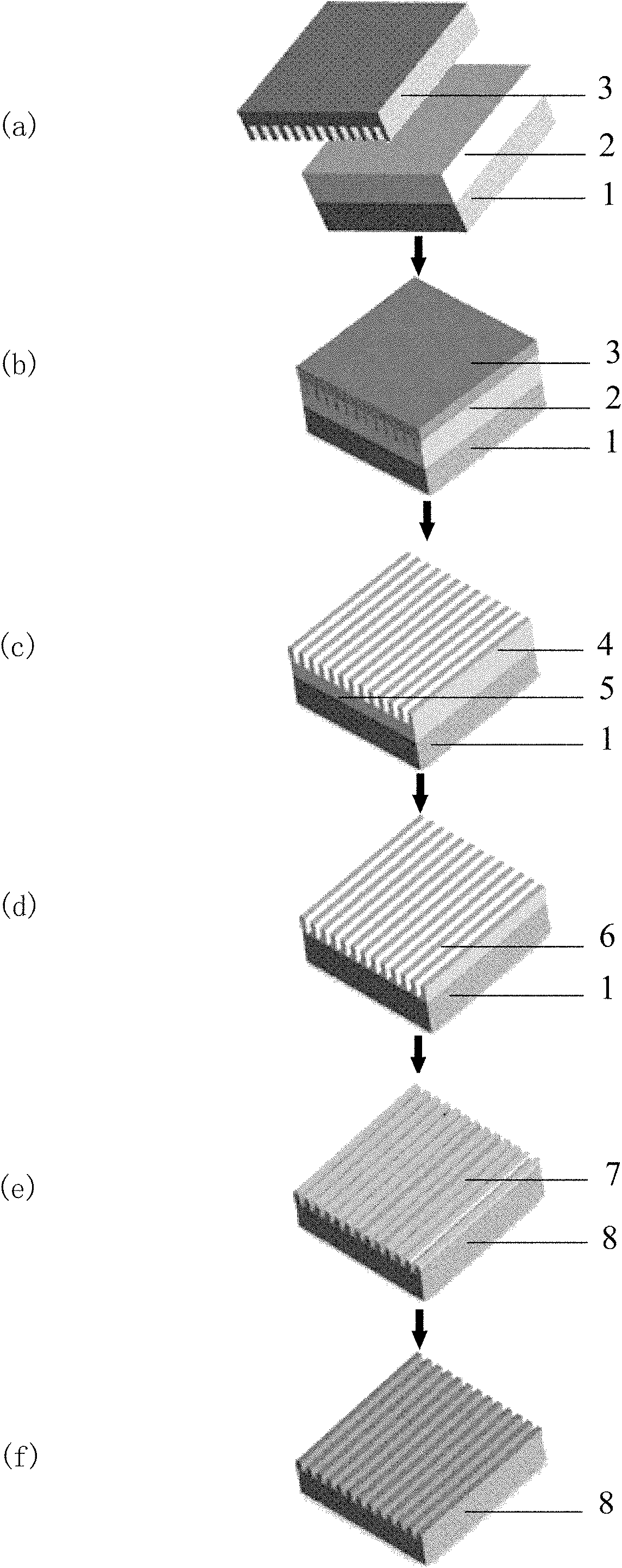

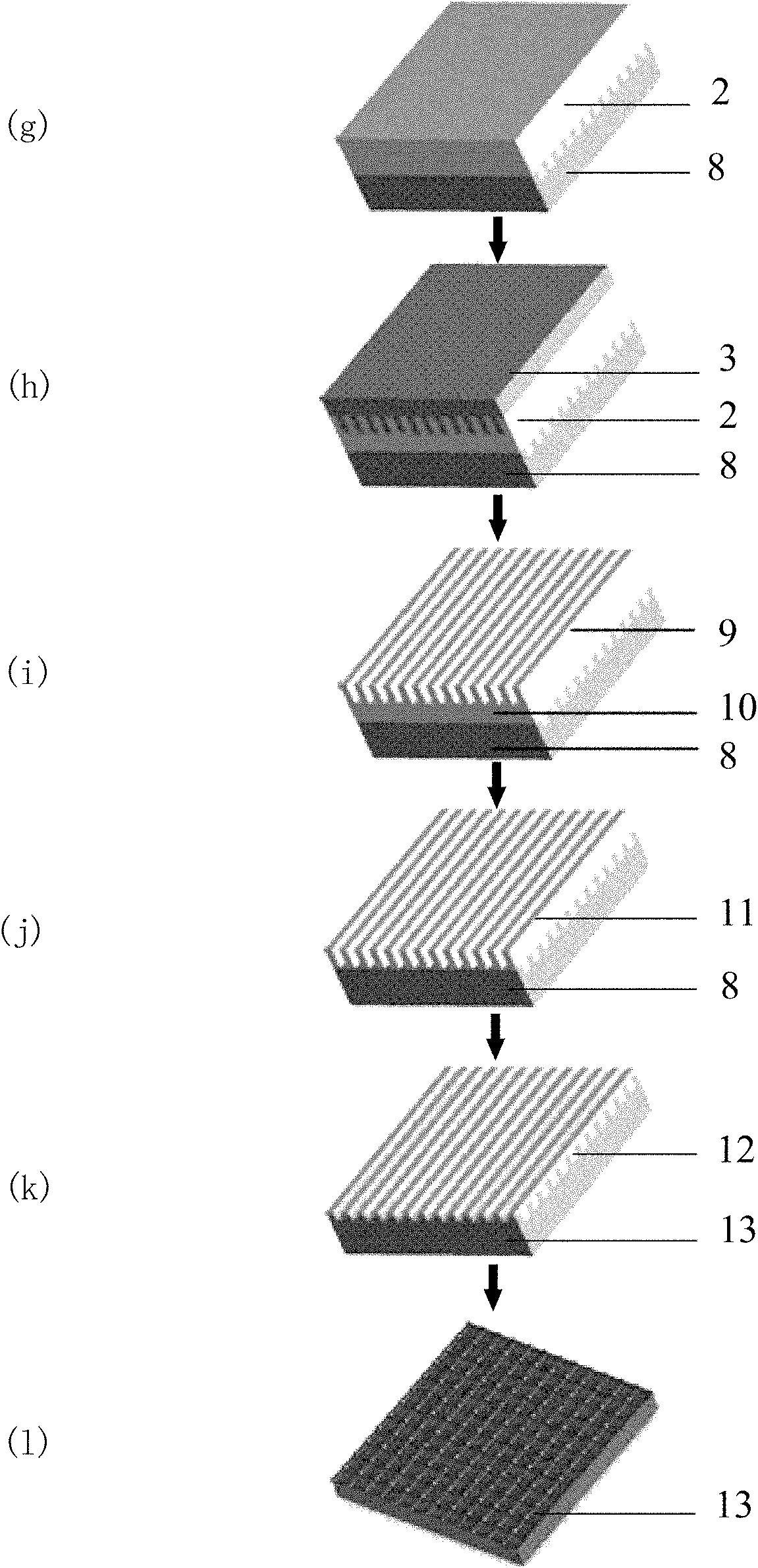

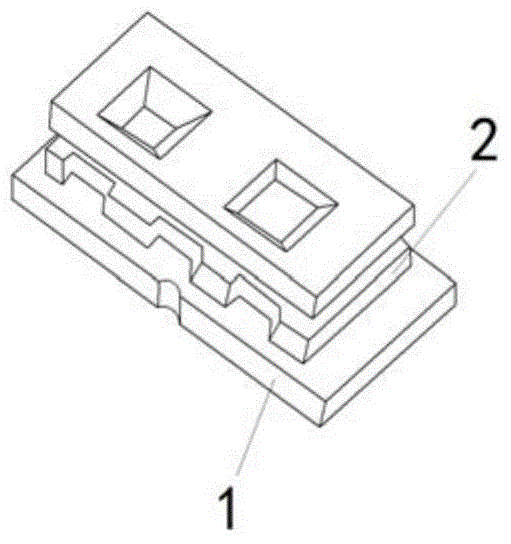

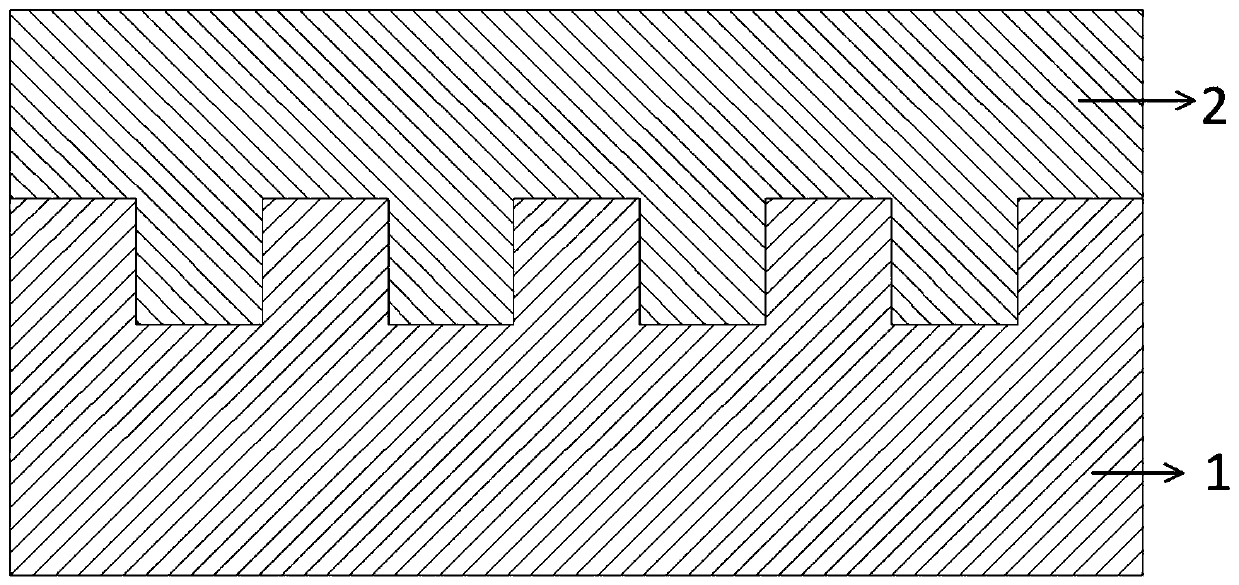

Method for manufacturing three-dimensional nano grid structure based on one-dimensional soft template nanoimprinting

InactiveCN102135728AAvoid permanent damageExtended service lifePhotomechanical apparatusNano gridIon

The invention belongs to the technical field of micro-nano manufacturing, and in particular relates to a method for manufacturing a large-area three-dimensional nano grid structure based on a one-dimensional soft template nanoimprinting technology. The method comprises the following steps of: performing first-time nanoimprinting by using a soft template; removing a imprinting glue residual layer by oxygen reactive ion etching (RIE); degumming by using a manufactured imprinting glue pattern as a masking film etching substrate material to obtain a one-dimensional nano grating structure; performing a second-time imprinting and etching process by using parameters the same as those of the previous imprinting and etching process; and adjusting the included angle formed between the direction of the template during the second-time imprinting and the direction of the template during the first-time imprinting to be between 0 and 90 degrees so as to obtain the three-dimensional nano grid structure with a 25nm nano-point. Due to the adoption of the soft template, permanent damages caused by contacting a hard template with a hard substrate can be effectively avoided, and the usage of a three-dimensional template is avoided simultaneously. The size and the shape of the manufactured nano structure are controllable. The method is low in cost and high in efficiency, controllability and resolution.

Owner:DALIAN UNIV OF TECH

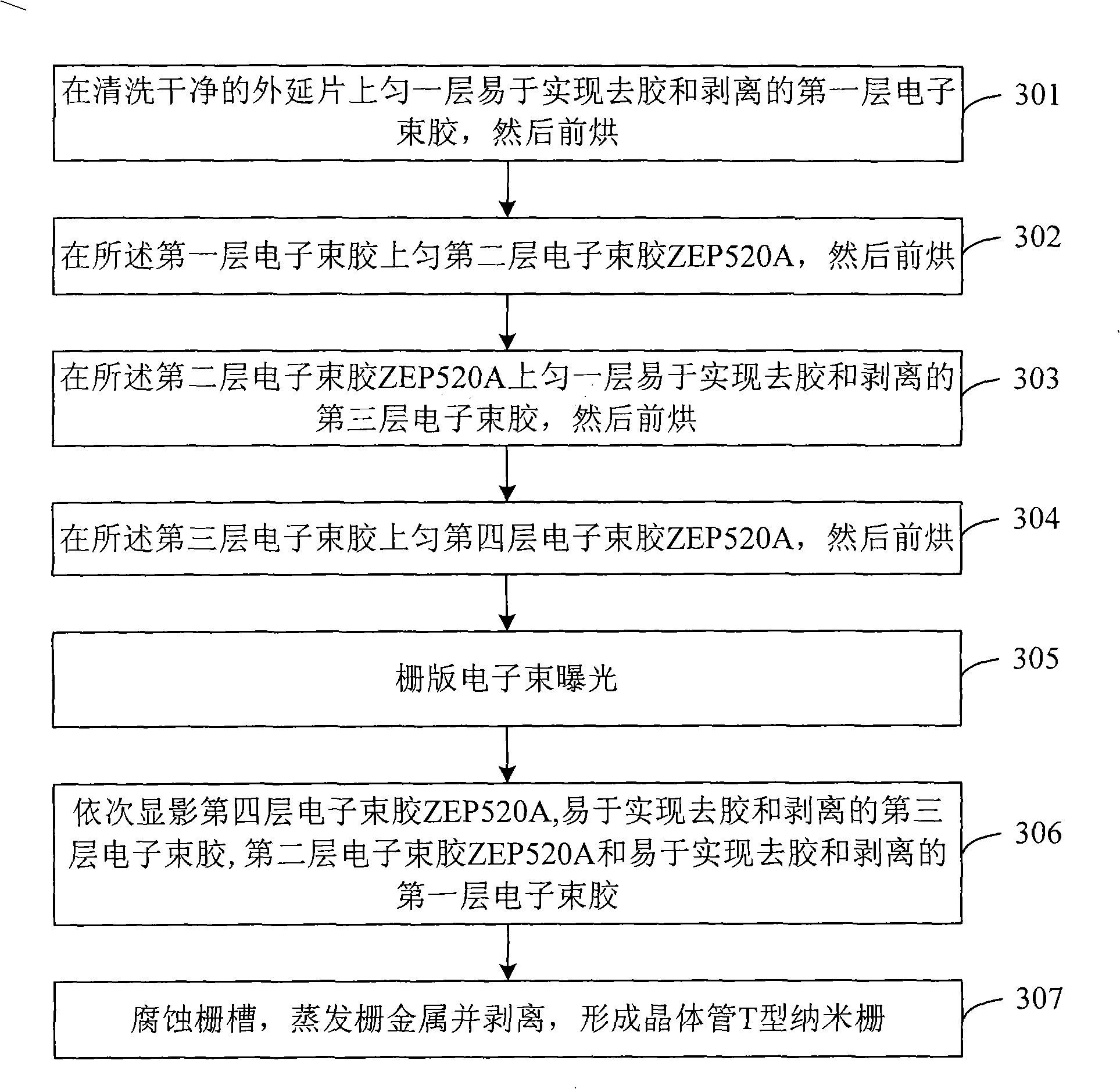

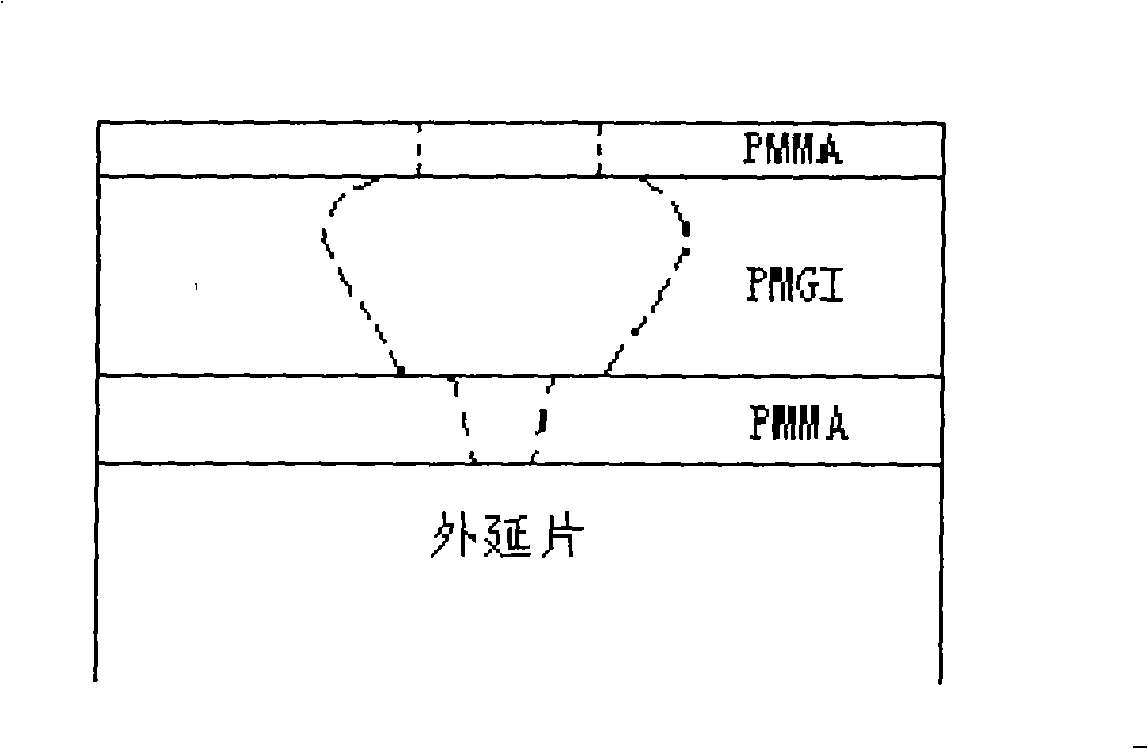

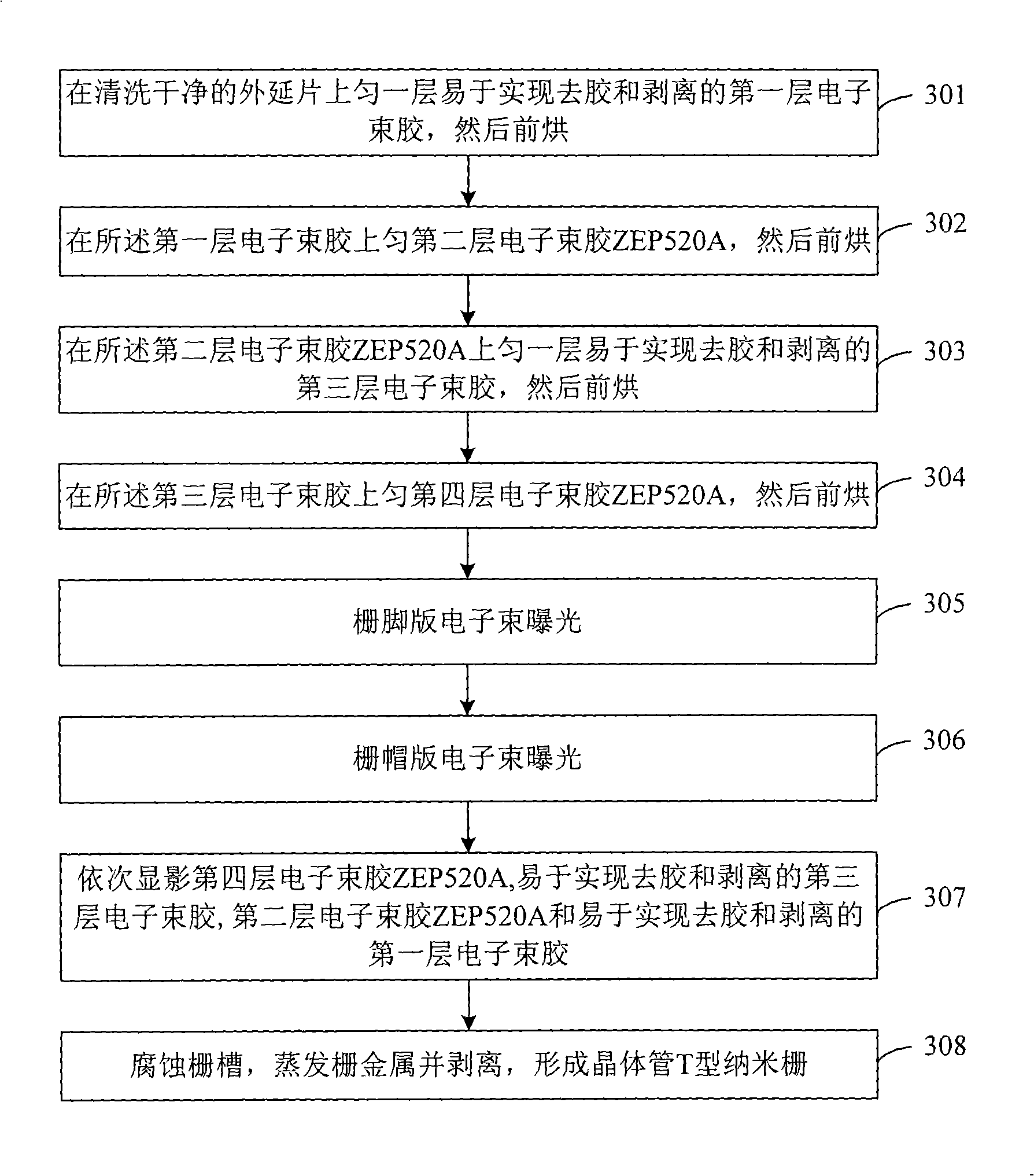

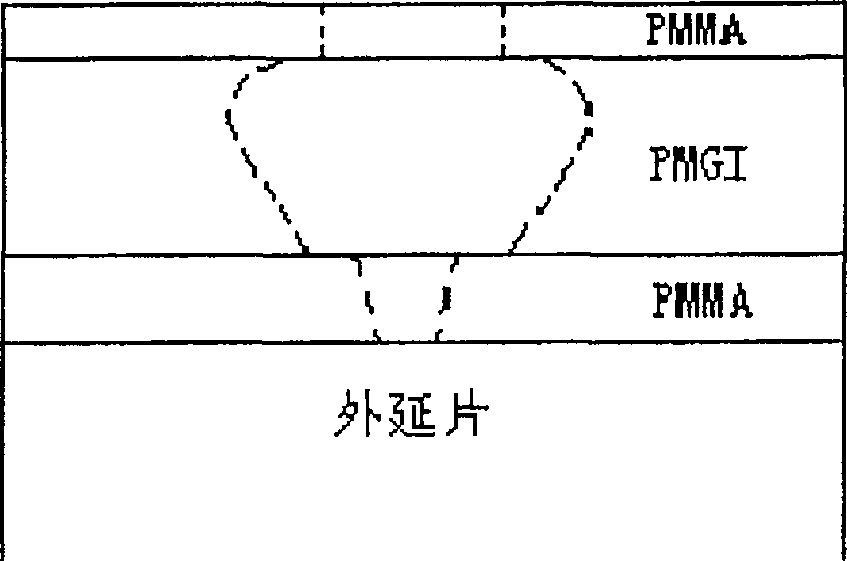

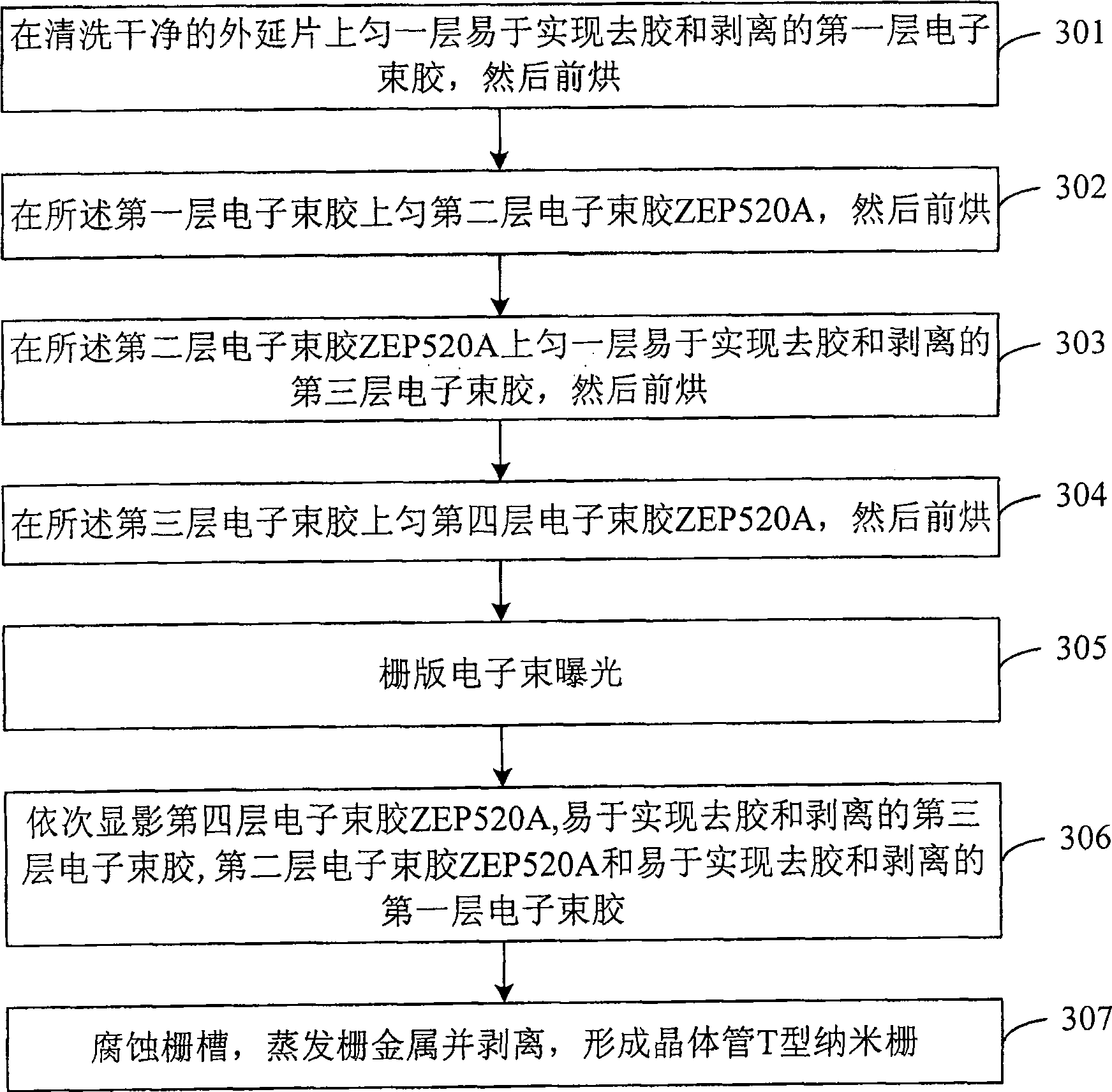

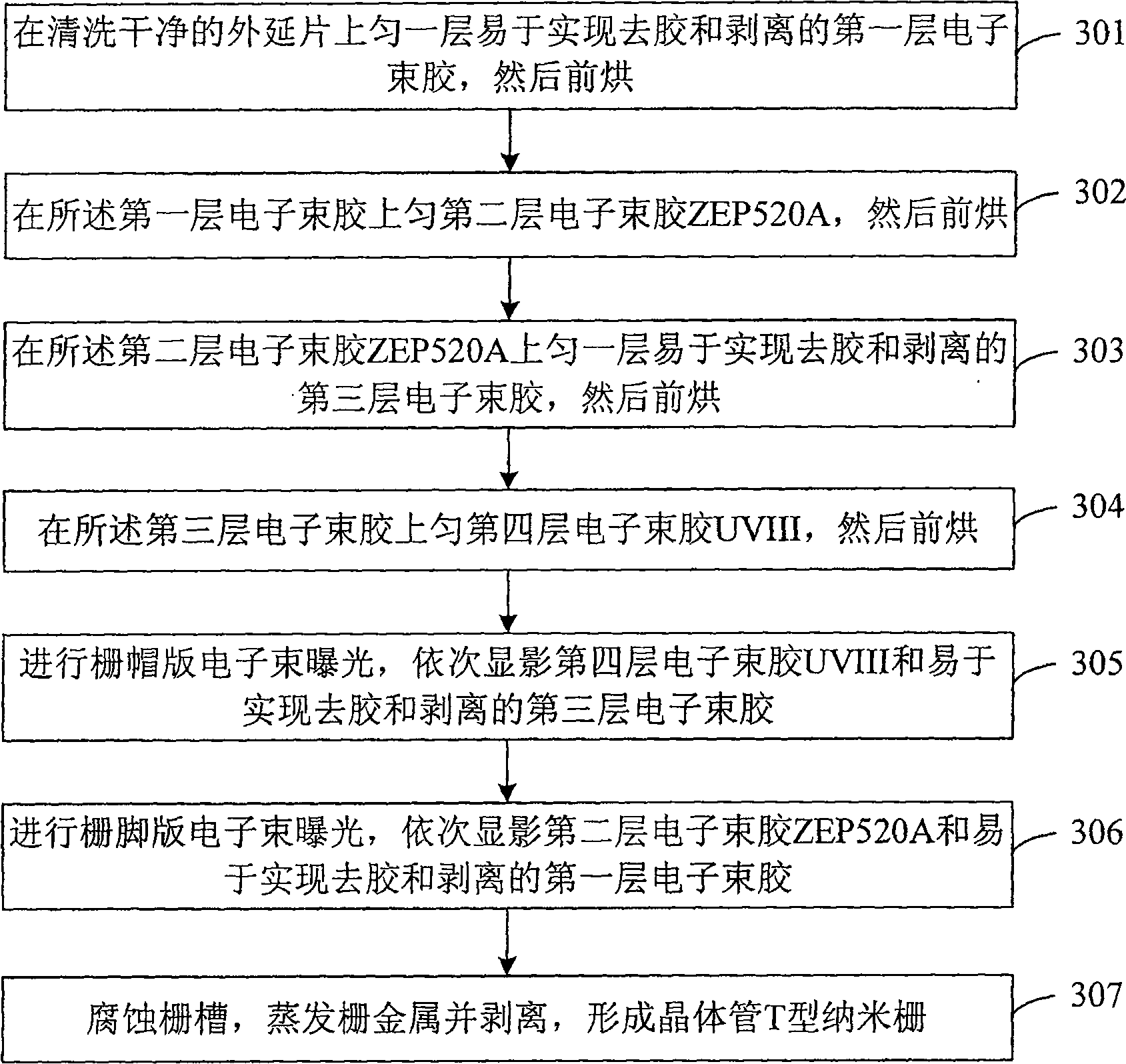

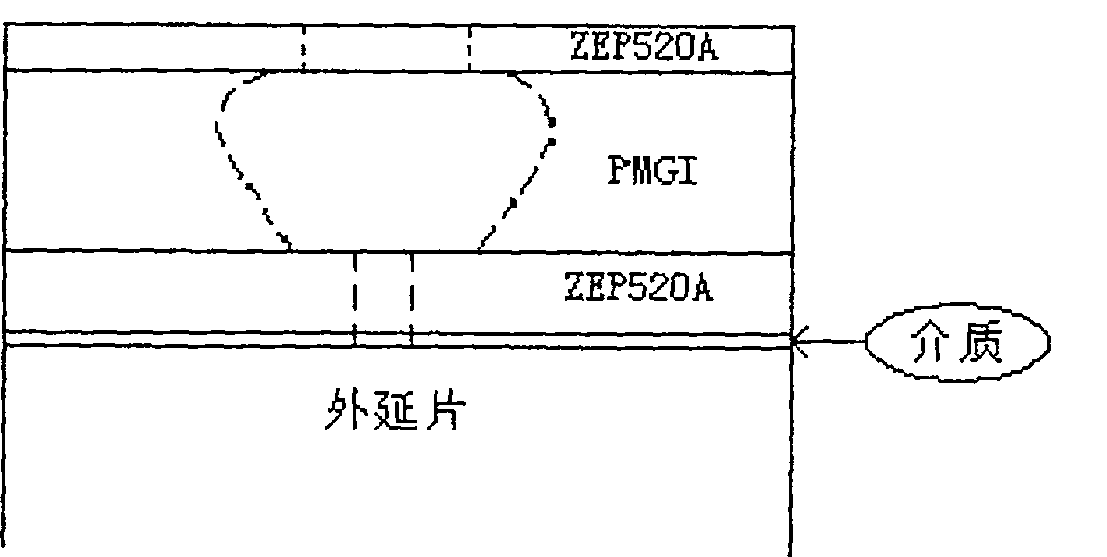

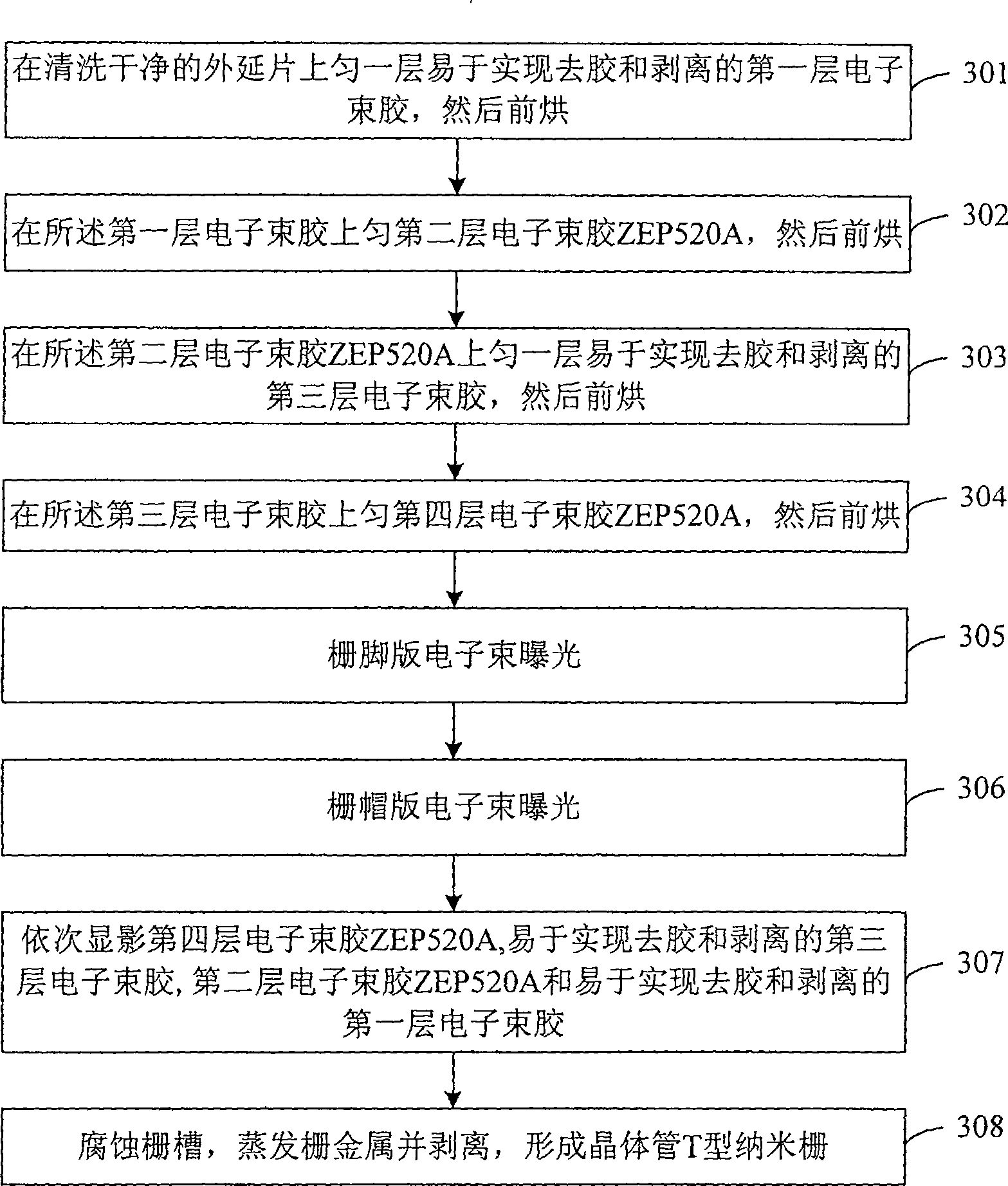

Method for producing transistor T type nano grid using once electron beam exposure

InactiveCN101276749AEasy to manufactureNo sleeve alignment issuesPhotomechanical apparatusSemiconductor/solid-state device manufacturingCooking & bakingElectron-beam lithography

The invention discloses a method for using once electric beam exposure to manufacture transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue ZEP520A on the third layer electric beam glue, and then soft-baking; E, carrying out gate electric beam exposure; F, sequentially developing the four layer electric beam glue ZEP520A, the third layer electric beam glue which is liable to realize glue-stripping and peeling, the second layer electric beam glue ZEP520A and the first layer electric beam glue which is liable to realize glue-stripping and peeling; G, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. The invention has strong reliability, simple processes and is easy to peel off and strip the glue.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

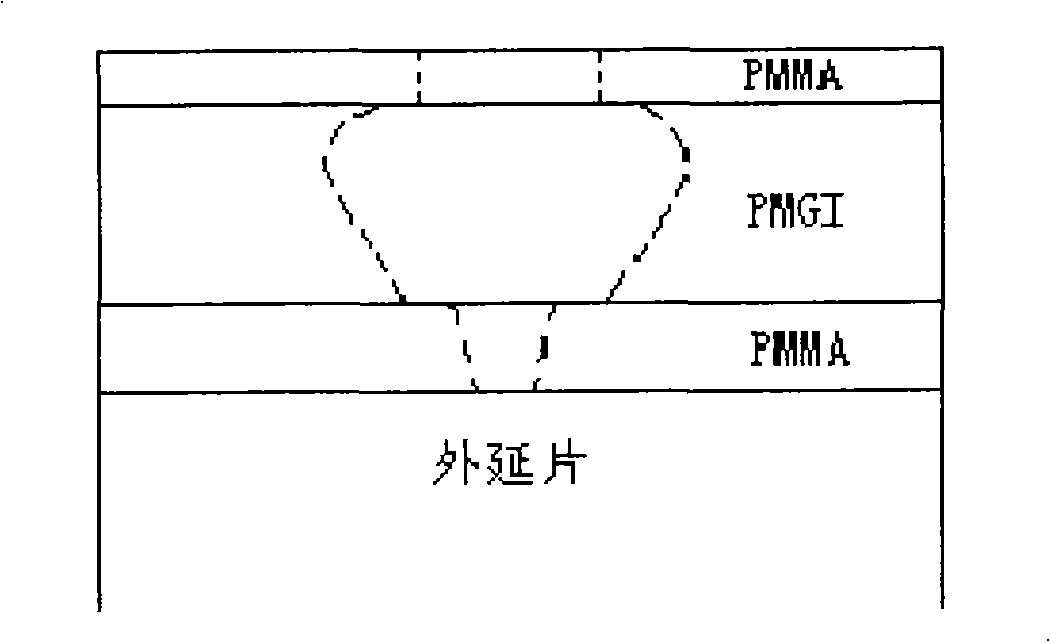

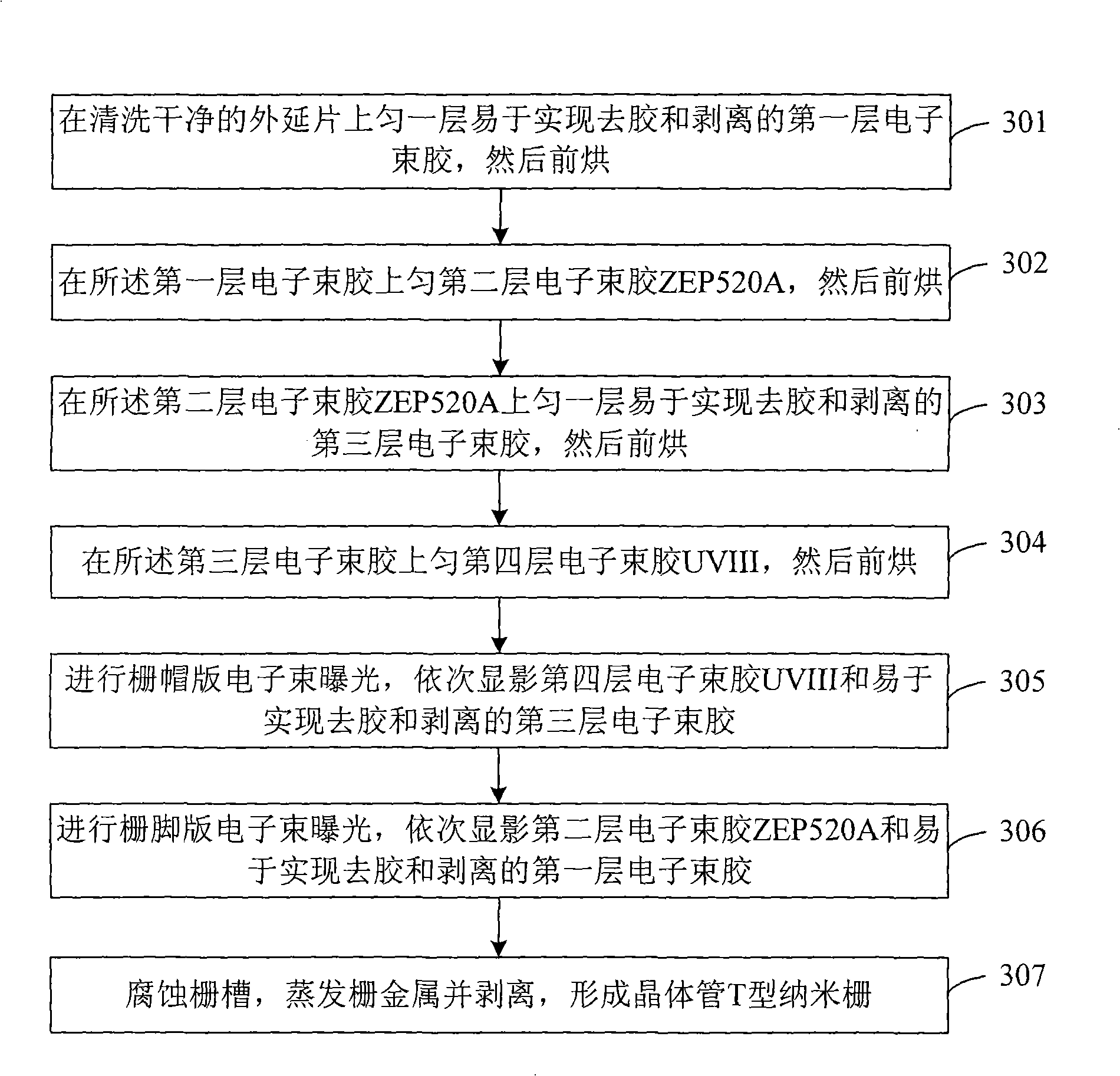

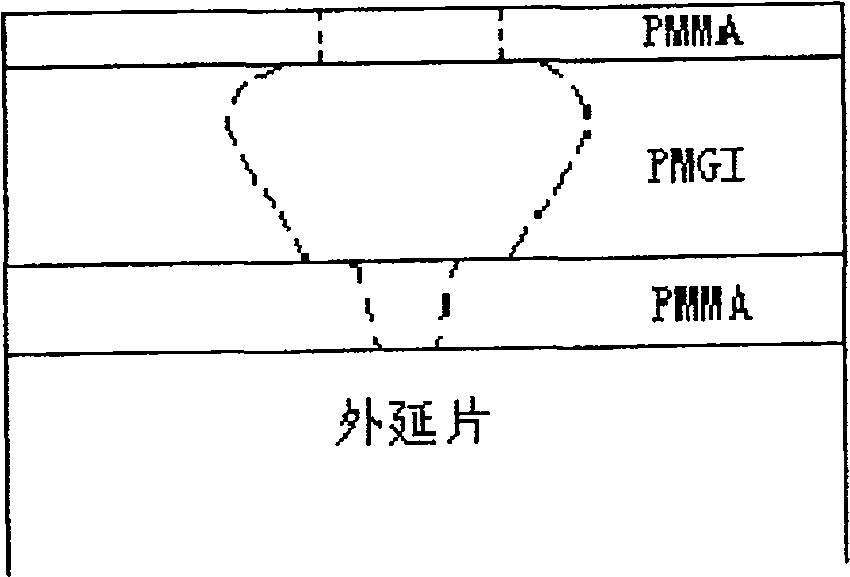

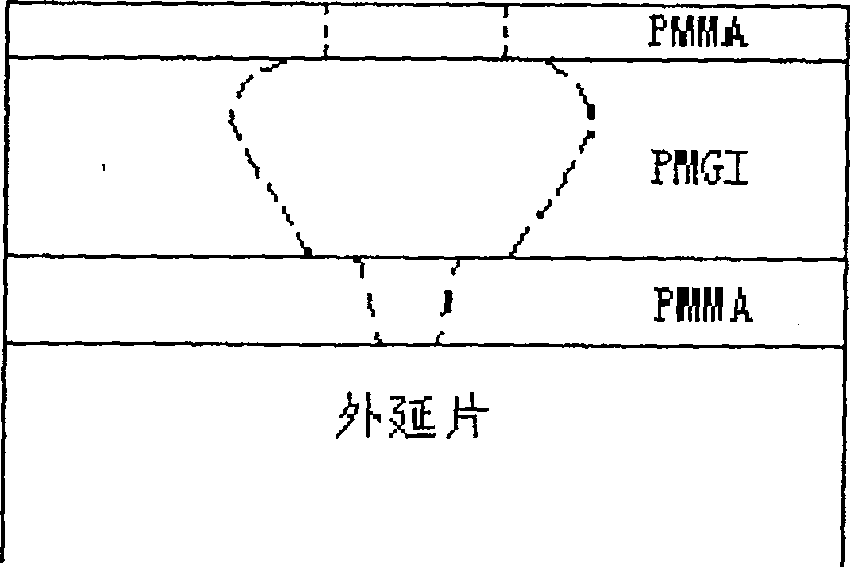

Method for preparing transistor T type nano grid

ActiveCN101276751AEasy to manufactureLoose conditionsSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingElectron-beam lithography

The invention discloses a method for manufacturing transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue UVIII on the third layer electric beam glue, and then soft-baking; E, carrying out gate cap electric beam exposure, and sequentially developing the four layer electric beam glue UVIII, the third layer electric beam glue which is liable to realize glue-stripping and peeling; F, carrying out the gate feet electric beam exposure, and sequentially developing the second layer electric beam glue ZEP520A and the first layer electric beam glue which is liable to realize glue-stripping and peeling; G, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. Usage of the invention can easily manufacture the gate lines having small size, greatly reducing the process difficulty.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

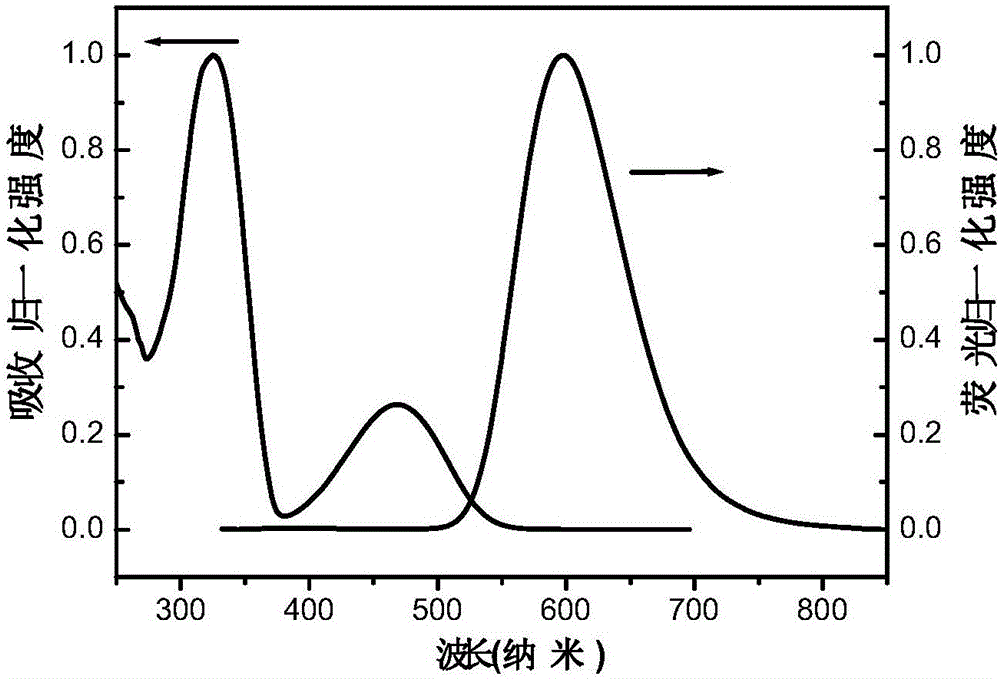

Fluorenyl donor/receptor type nano polymer as well as preparation method and application thereof

InactiveCN106496527AImprove scalabilityHigh selectivitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic solar cellElectron donor

The invention discloses a fluorenyl donor / receptor type nano polymer as well as a preparation method and application thereof. In a nano grid polymer, a fluorenyl derivative is used as electron donor units in nano grid fragments, and the electron donor units and electron receptor units are arranged alternatively to form a square annular rigid structure. The preparation method comprises the following step: performing a polymerization reaction on a nano grid fragment (II) and a polymerization fragment (III) with preserved halogen end groups, thereby obtaining the polymer. The polymer material disclosed by the invention has the advantages that a synthesis mode is modularized, high extensibility and high thermal, electrochemical and optical stability can be achieved, film solvent dependency can be alleviated, large-scale soluble processing can be achieved, aperture sizes can be precisely adjusted and controlled, precise regulation and control on band gap and energy level arrangement can be achieved, and the like; and the polymer material has potential application prospects in fields of photoelectric functional materials for organic solar batteries, memories and memory resistors, sensors, detectors and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

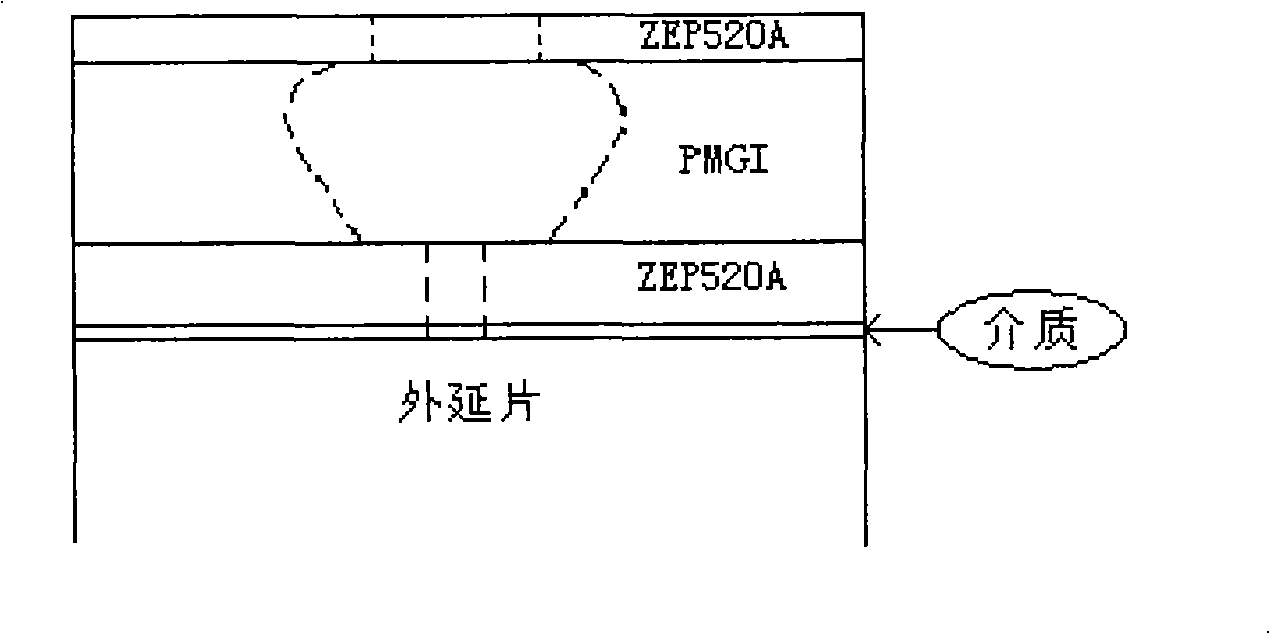

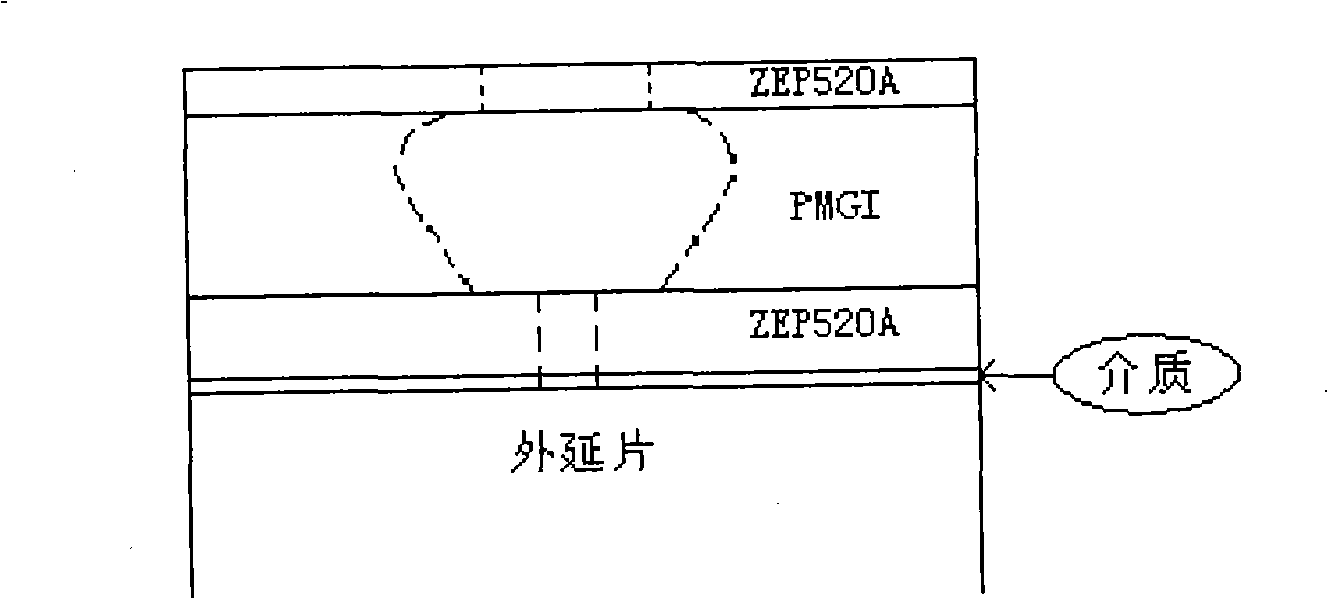

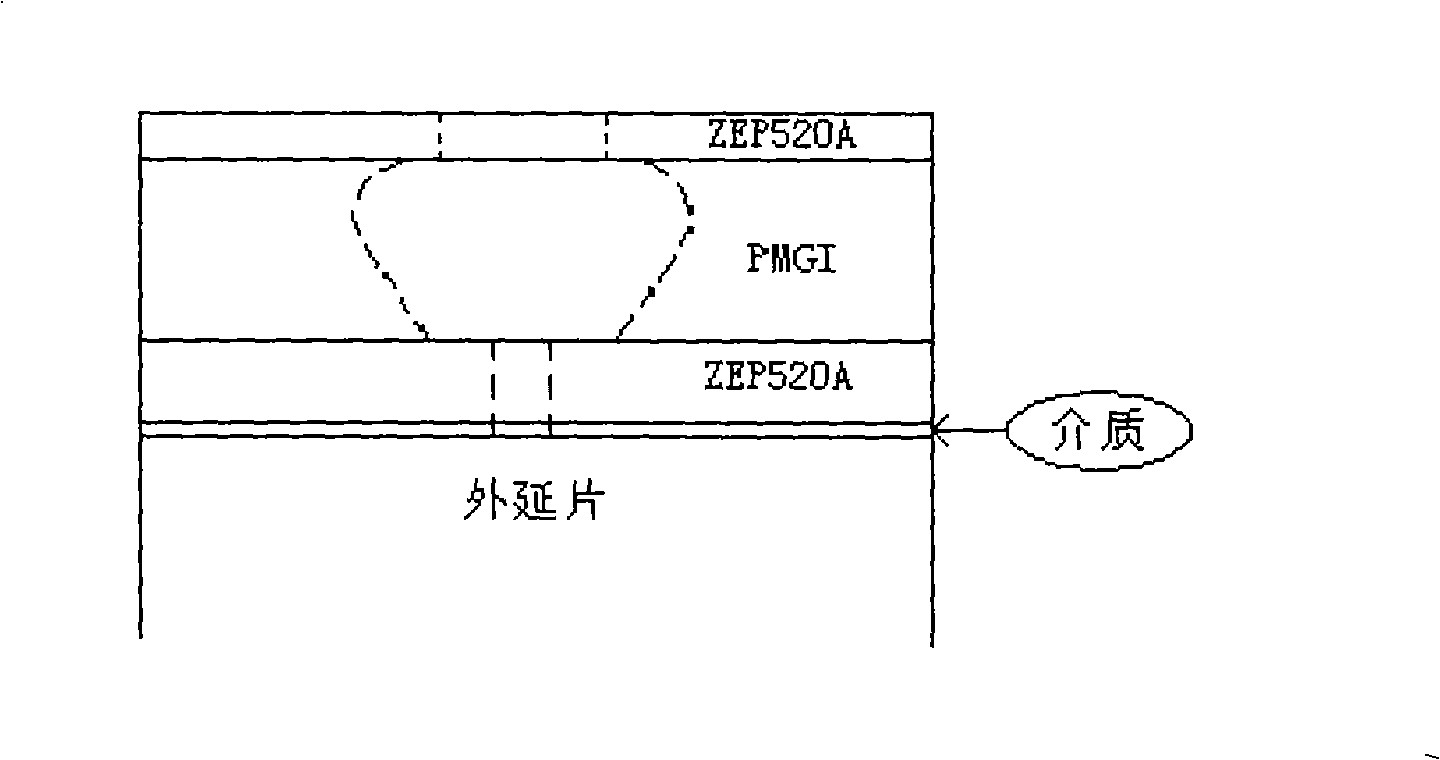

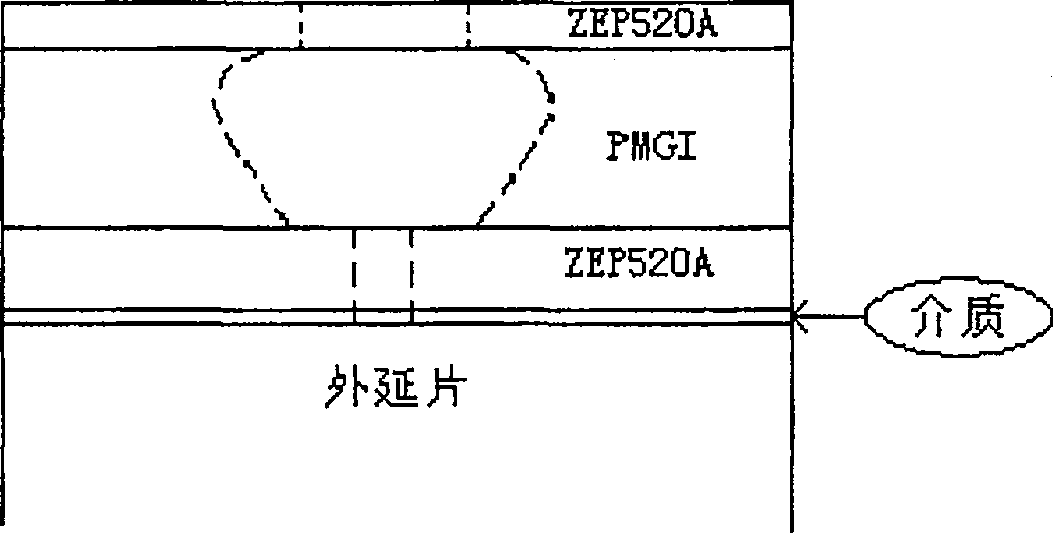

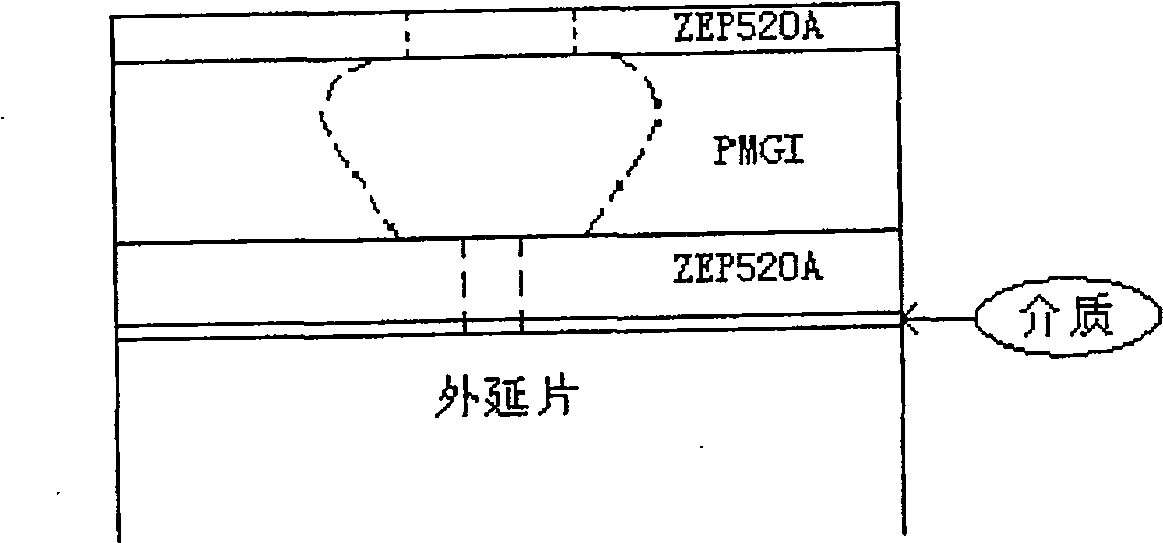

Method for preparing transistor T type nano grid

InactiveCN101276750AEasy to manufactureNo overlay alignment issuesSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingElectron-beam lithography

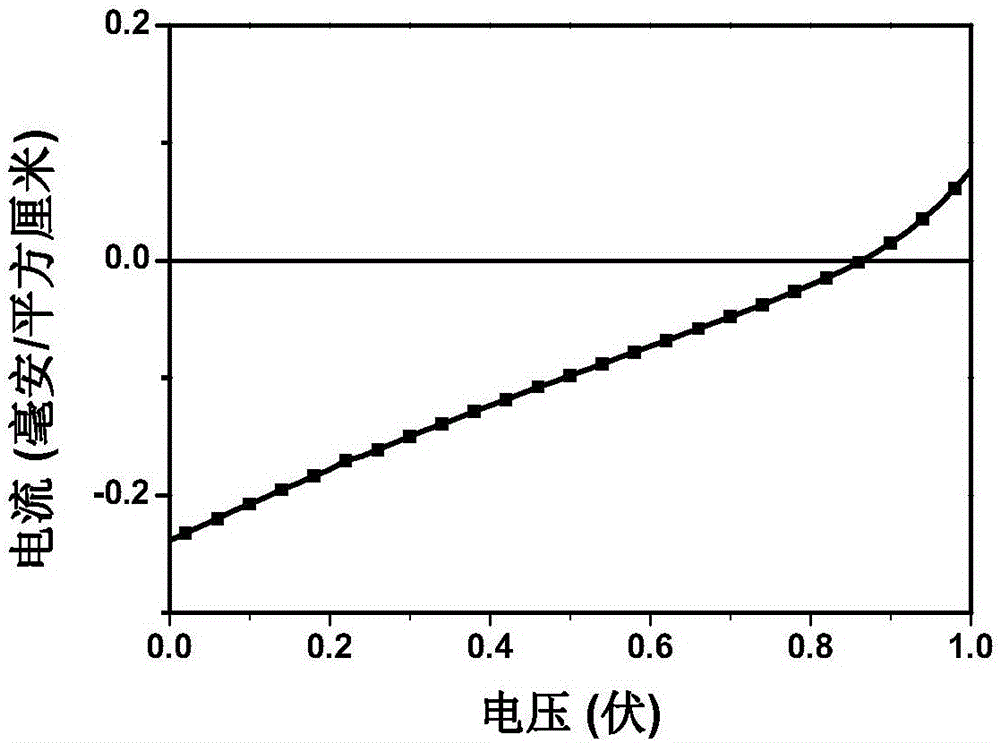

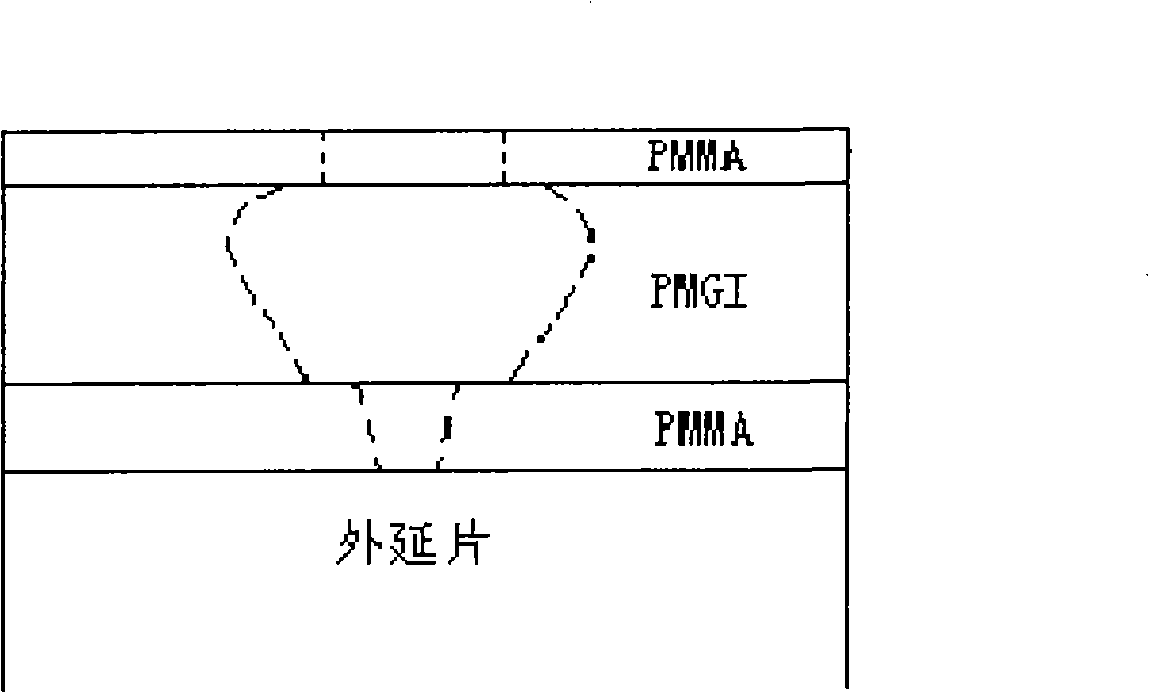

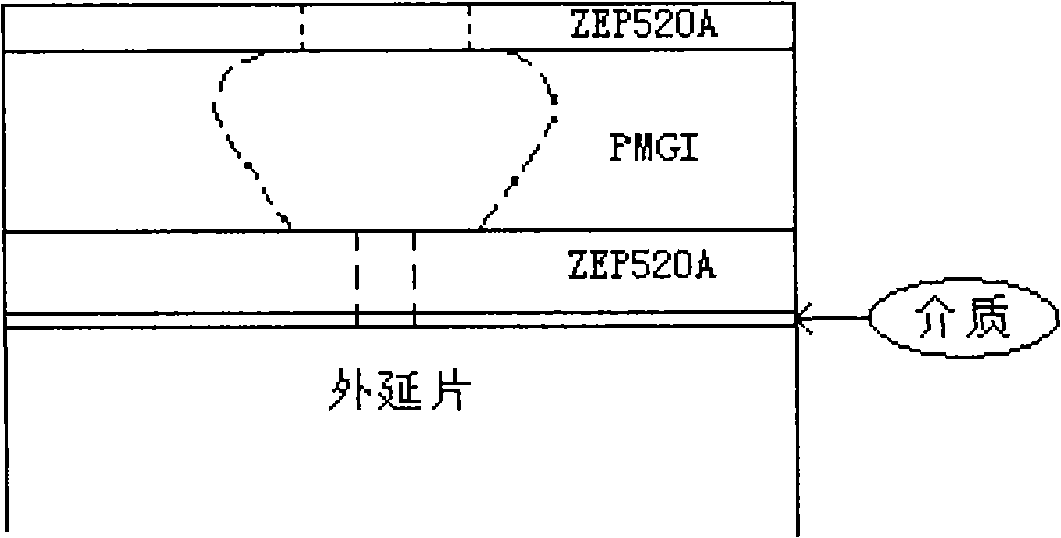

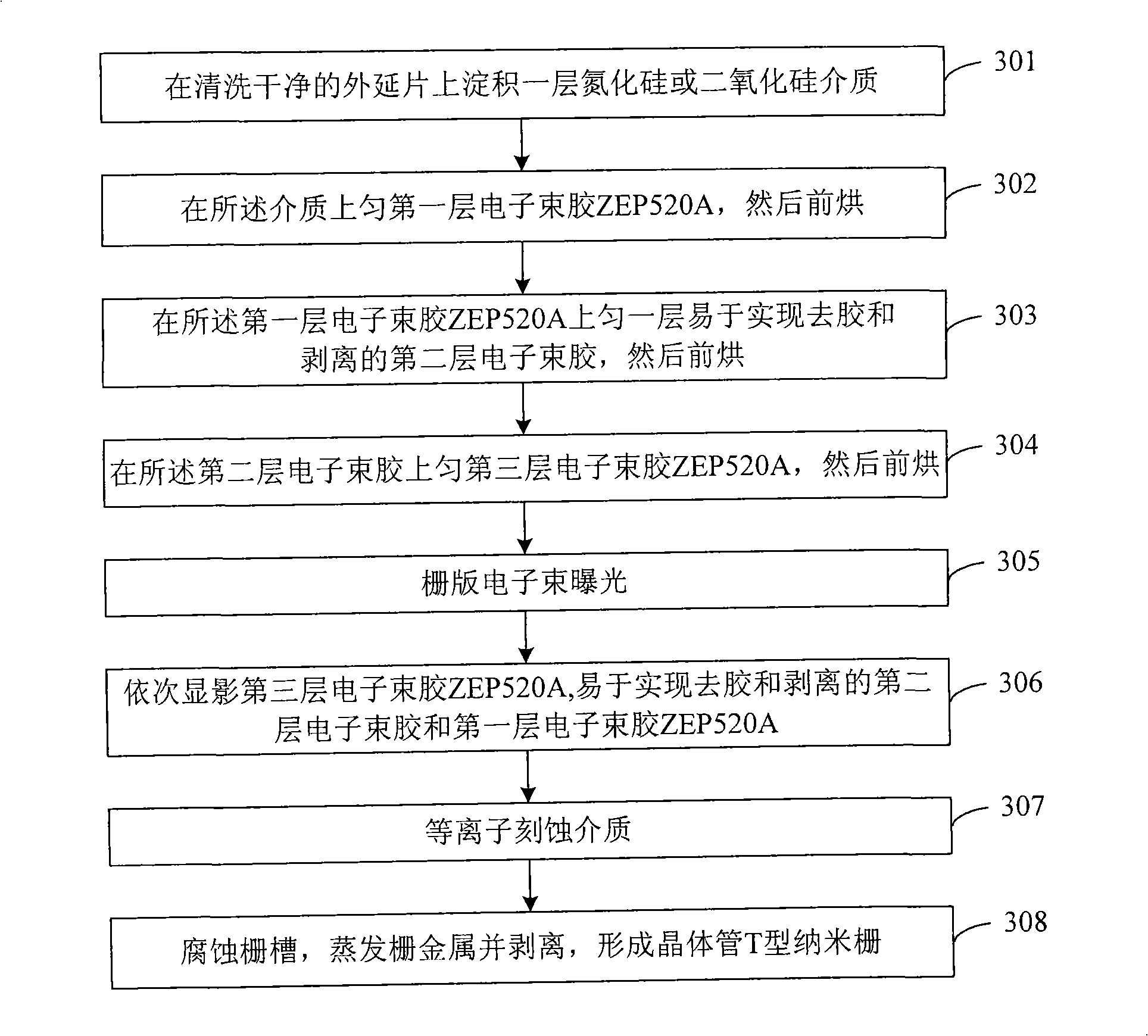

The invention discloses a method for manufacturing transistor T-shaped nanometer gate, comprising the steps of: A, depositing a layer of silicon nitride medium or silicon dioxide medium on a cleaned epitaxial wafer; B, coating a first layer electric beam glue ZEP520A on the silicon nitride medium or silicon dioxide medium, and then soft-baking; C, coating a second layer electric beam glue which is liable to realize glue-stripping and peeling on the first layer electric beam glue ZEP520A, and then soft-baking; D, coating a third layer electric beam glue ZEP520A on the second layer electric beam glue, and then soft-baking; E, carrying out gate electric beam exposure; F, sequentially developing the third layer electric beam glue ZEP520A, the second layer electric beam glue which is liable to realize glue-stripping and peeling and the first layer electric beam glue ZEP520A; G, plasma-etching the silicon nitride medium or silicon dioxide medium; H, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. In free of the problem about overlaying alignment, the invention is simple in processes, easy to manufacture the gate lines having small size and strong in reliability.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

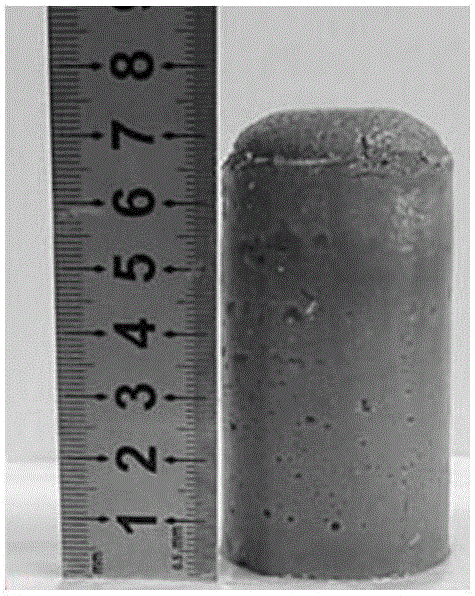

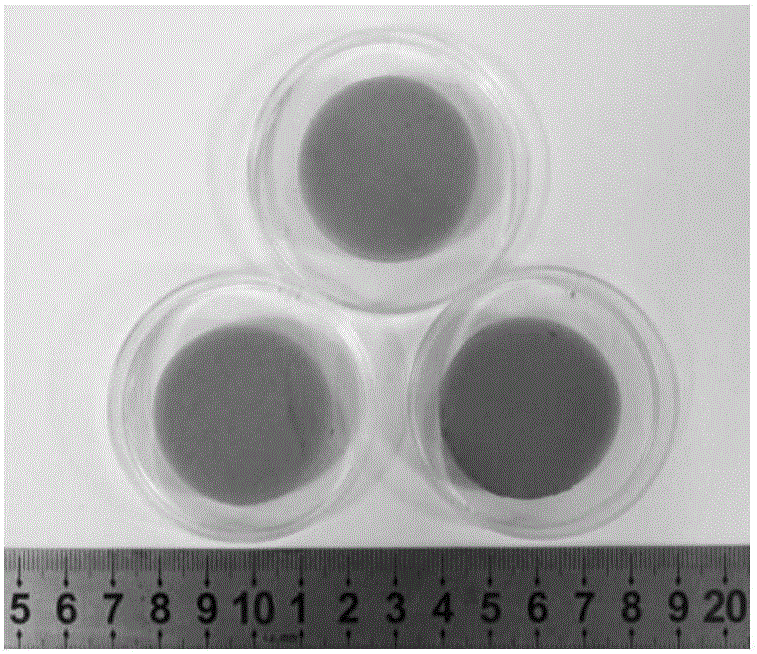

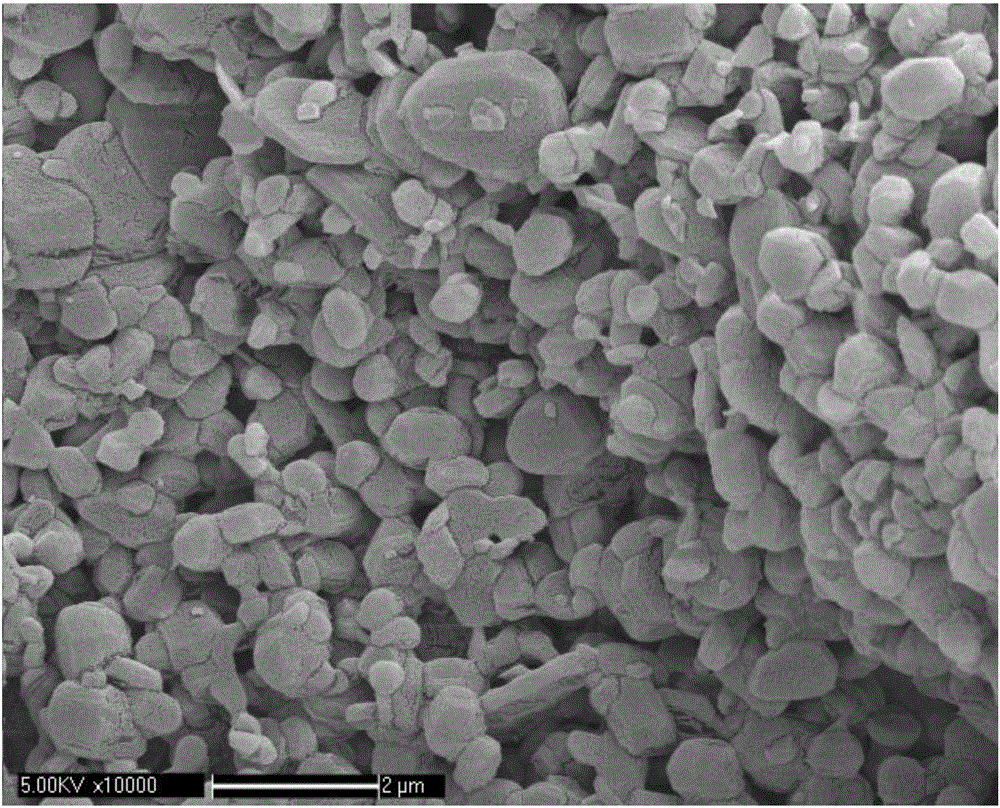

Preparation method of nano grid octogen

ActiveCN103626711AMild reaction conditionsReduce manufacturing costOrganic chemistryNanotechnologyMicro structureGram

The invention discloses a preparation method of nano grid octogen, which comprises the steps of adding a HMX / DMSO complex into pure water or a surfactant solution, stirring for certain time, filtering, washing and drying to obtain nano grid octogen powder with different micro structures. The method is used for quickly preparing nano grid octogen based on the HMX / DMSO complex, and can realize preparation from gram level to kilogram level; expensive large equipment is not required; the method is performed under room temperature conditions, and reaction conditions are mild; the preparation cost is low.

Owner:INST OF CHEM MATERIAL CHINA ACADEMY OF ENG PHYSICS

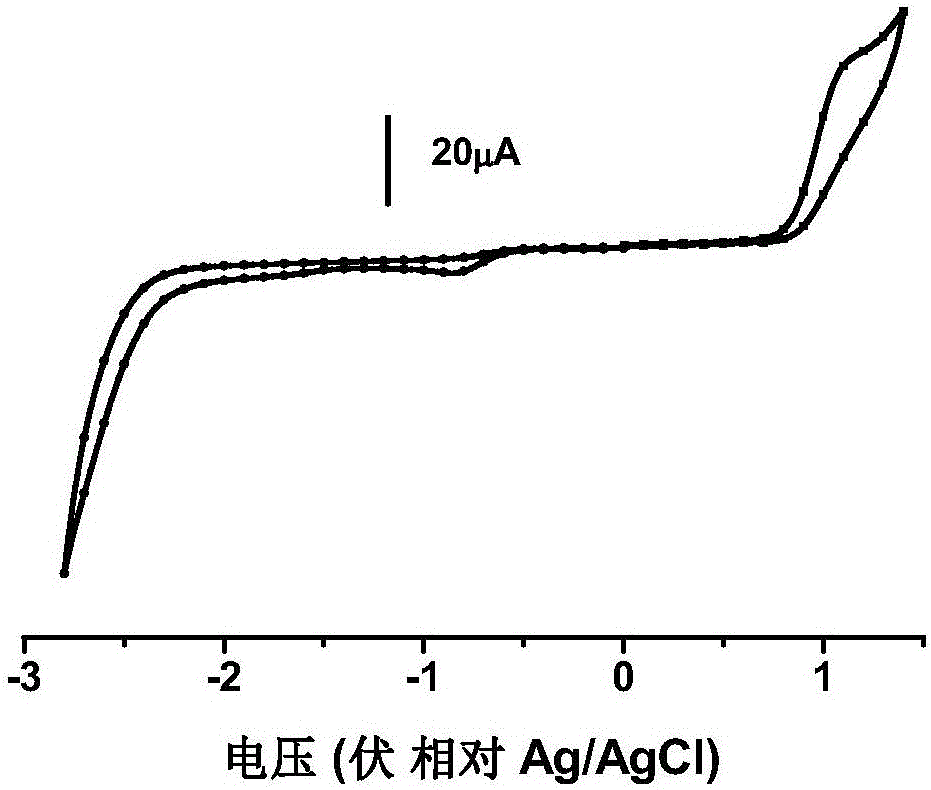

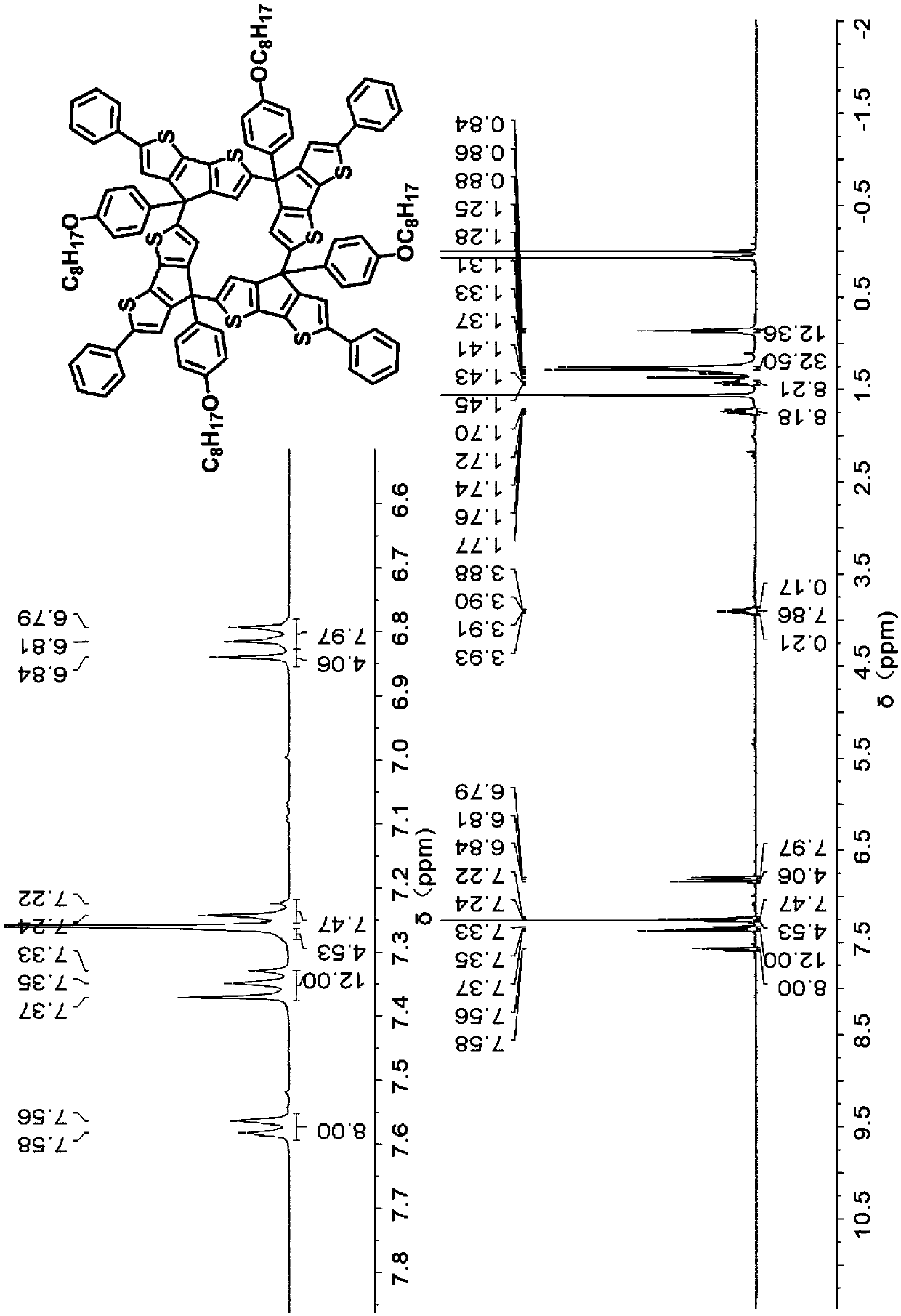

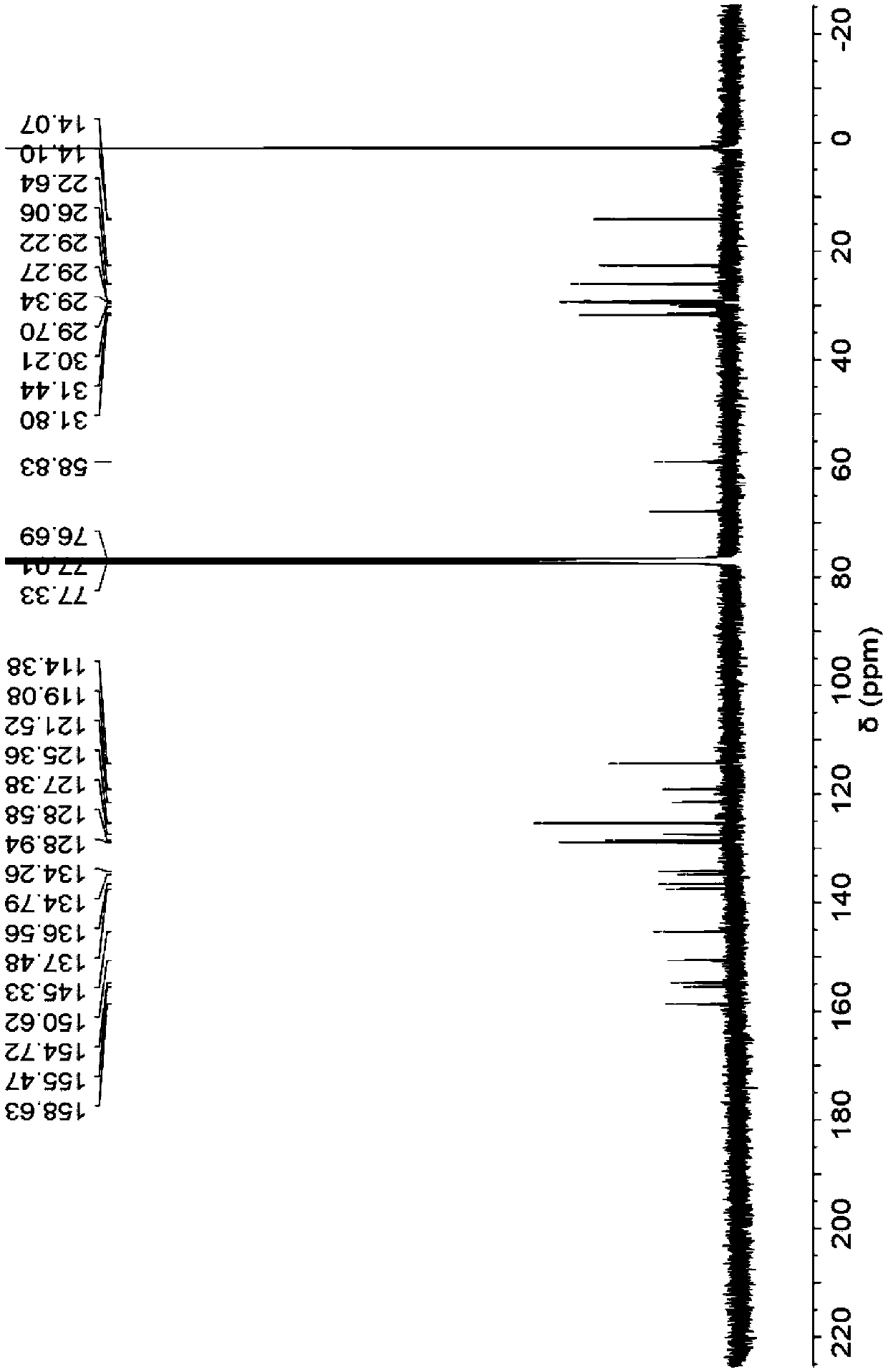

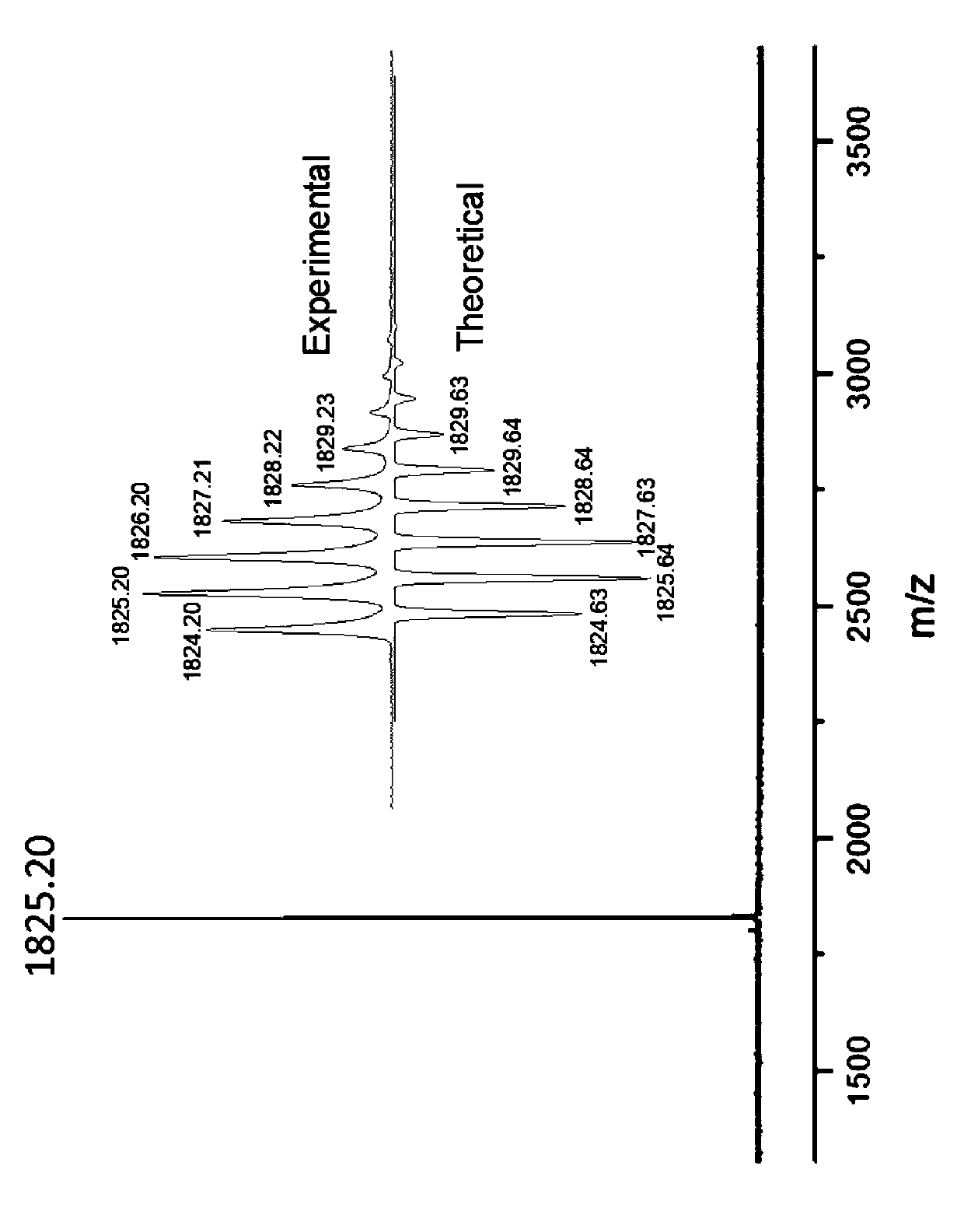

Fluorenyl-similar windmill-shaped nano-grid as well as preparation method and application thereof

ActiveCN109516997AEasy to makeMild reaction conditionsOrganic chemistrySolid-state devicesSolubilityOrganic solar cell

The invention discloses a fluorenyl-similar windmill-shaped nano-grid as well as a preparation method and application thereof, belonging to the field of nano-techniques and organic electrons. The fluorenyl-similar windmill-shaped nano-grid is of a closed loop structure with a fluorenyl-similar micromolecule derivative as a monomer, and the structural general formula of the nano-grid is as follows:formula (shown in the description). The fluorenyl-similar windmill-shaped nano-grid is prepared through loop closing through Friedel-Crafts reaction and has the characteristics of simplicity in preparation, mild reaction condition, high productivity, yield and selectivity, simplicity and convenience in after-treatment, environmental friendliness, no toxin, regular structure, relatively good rigidity, good structural expansion property and solubility and the like; and a ring skeleton of the nano-grid contains multiple thiophene ring electron donors, and the whole structure is non-planar, so that the nano-grid has very good application prospects in the organic solar cell field after being linked with receptor groups.

Owner:NANJING UNIV OF POSTS & TELECOMM

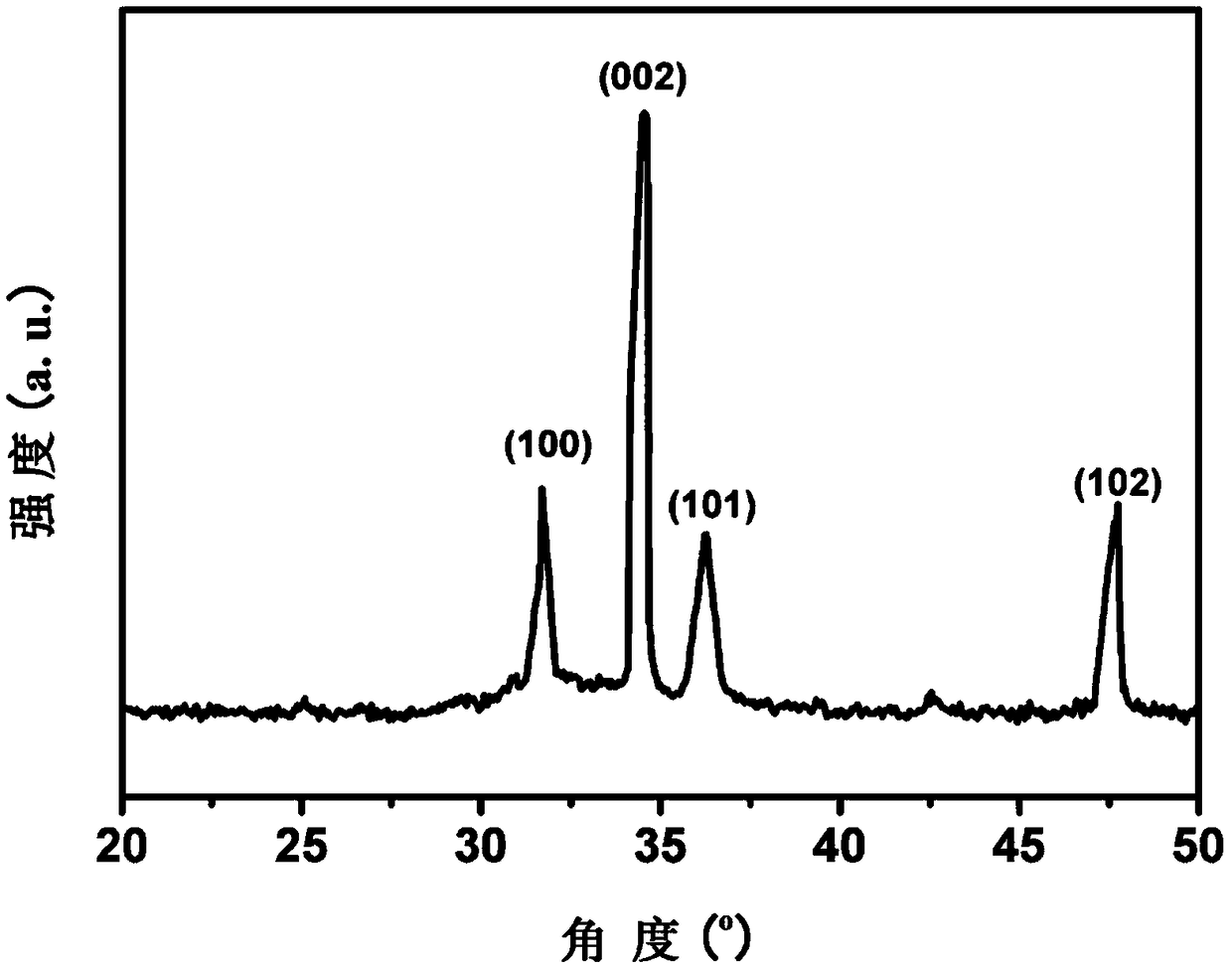

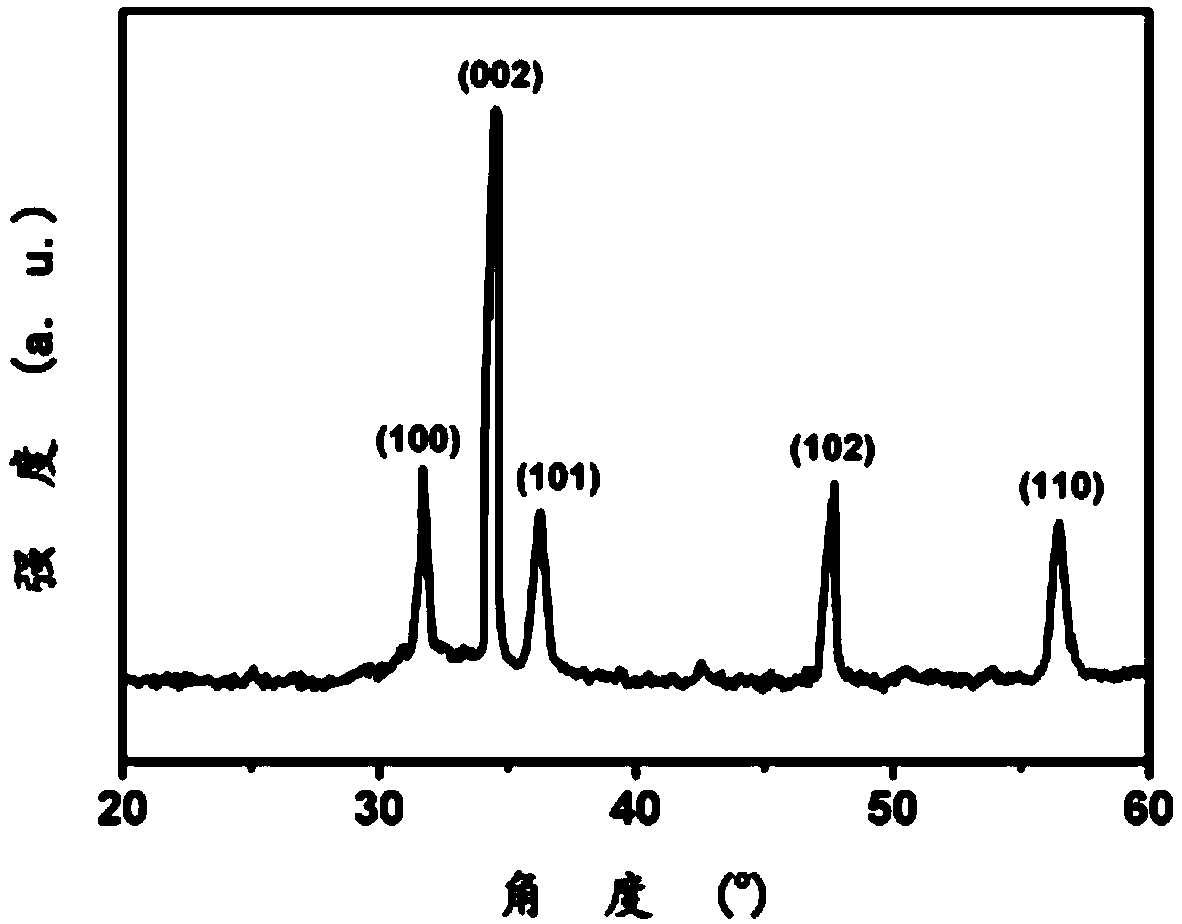

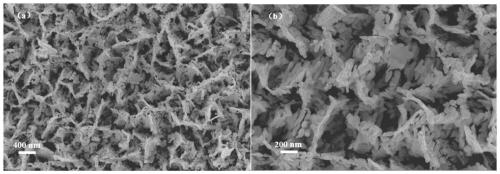

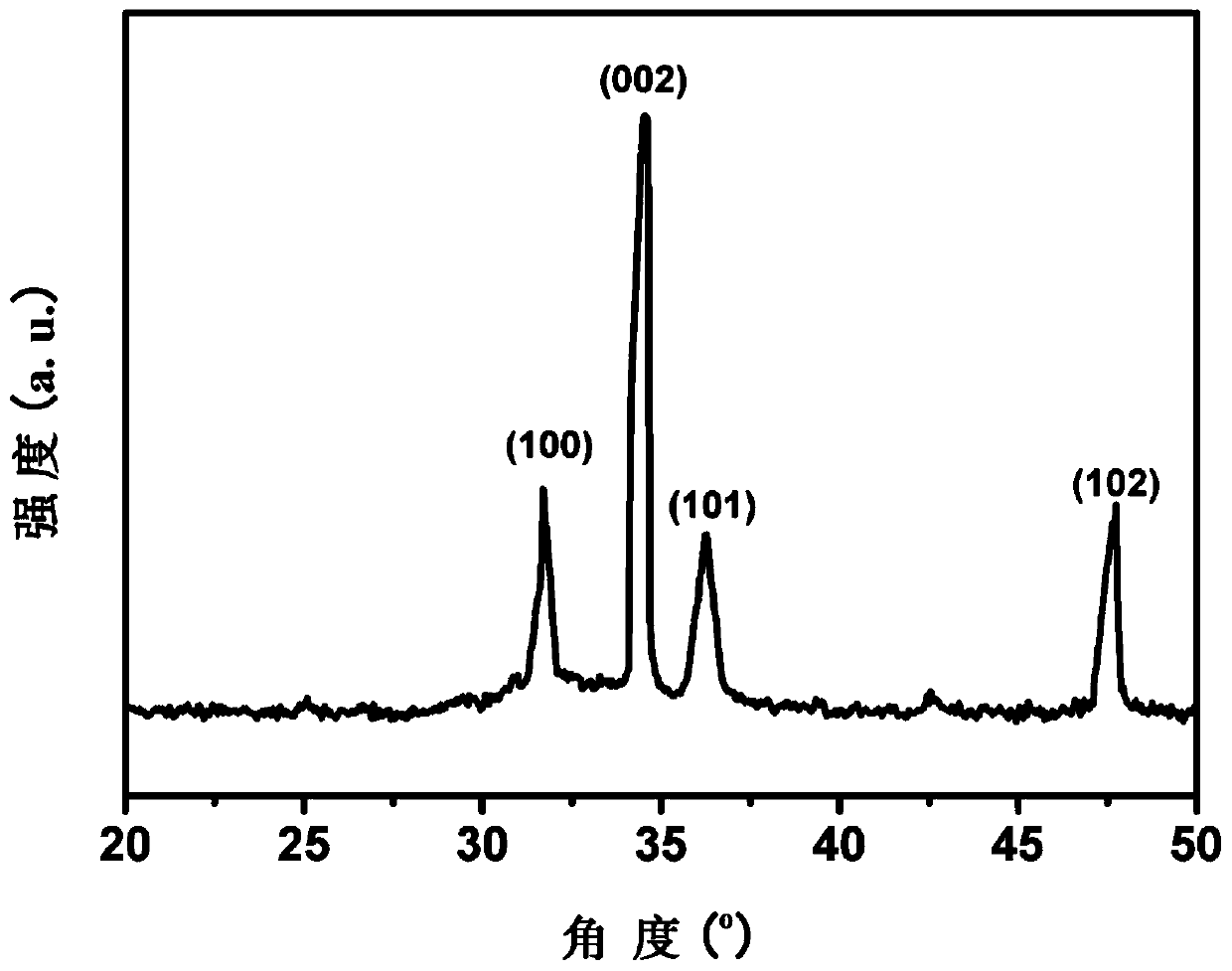

Novel ZnO nano material and preparation method thereof

ActiveCN108821326AThe preparation equipment is matureSimple processMaterial nanotechnologyZinc oxides/hydroxidesDopantMicrosphere

The invention provides a novel ZnO nano material and a preparation method thereof. The novel ZnO nano material comprises a substrate layer, nano walls and a nano-grid, wherein the nano wall is arranged on the substrate layer and is formed by stacking ZnO nanowires, and the nano-grid is composed of the nano-walls. The method specifically comprises the following steps that 1) a precursor mixed solution is prepared by using zinc acetate, a pore-forming agent and a dopant; 2) a precursor film is prepared by utilizing the precursor mixed solution; and 3) high-temperature sintering is carried out soas to obtain the ZnO nano-material. According to the novel ZnO nano material and the preparation method thereof, preparation equipment is mature, the process is simple, and large-scale production isfacilitated; the sintering temperature is accurately controlled, zinc acetate and the pore-forming agent are decomposed into water and carbon dioxide and the water and carbon dioxide are separated from microspheres so as to help to form pore channels and nanowires; a precursor can be completely decomposed at the temperature of 500 DEG C, crystallization of the ZnO nanowires is promoted, so that the novel ZnO nano material with good crystallization state is obtained, the size of the prepared microspheres is controllable, and the pore channels are uniformly distributed; and the ZnO nano materialprepared through the preparation method provided by the invention is wide in application range.

Owner:WUYI UNIV

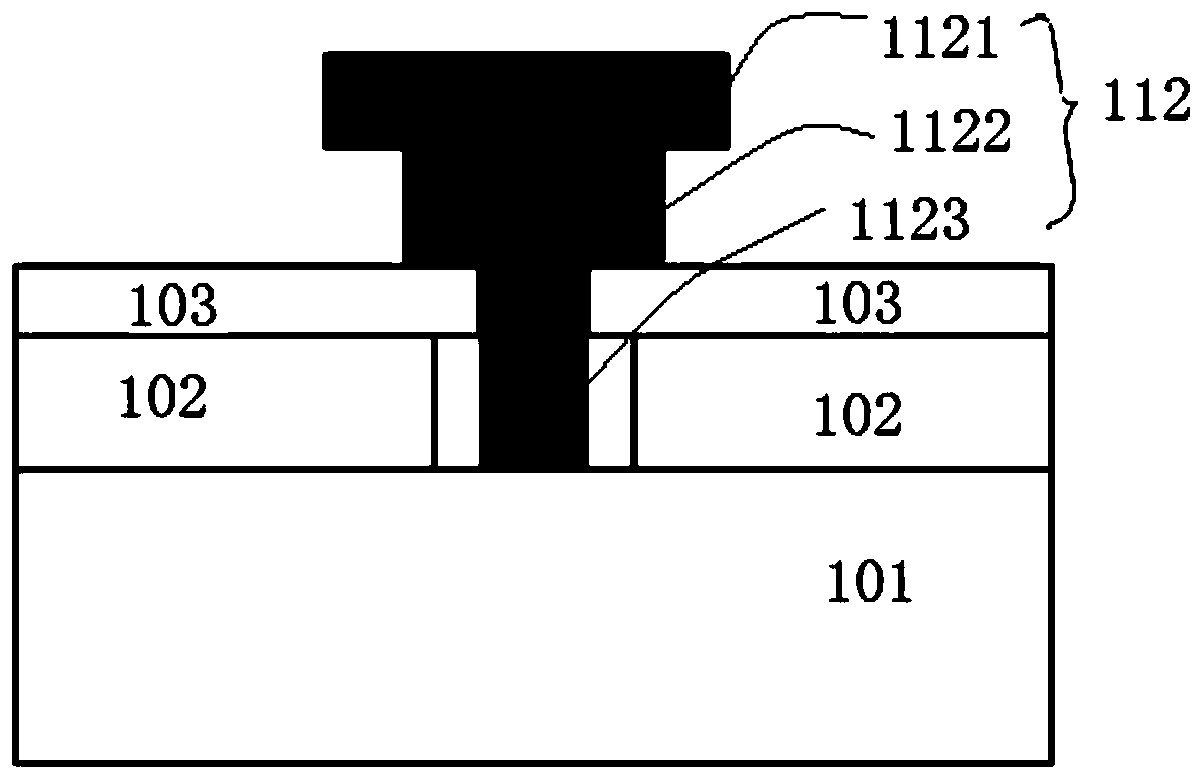

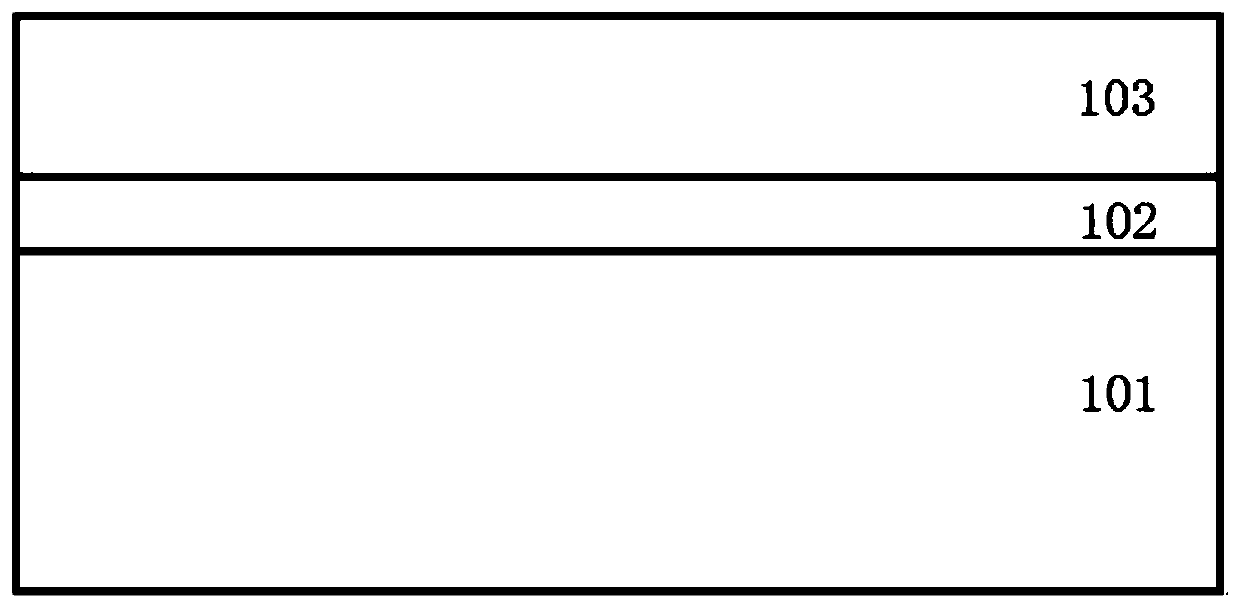

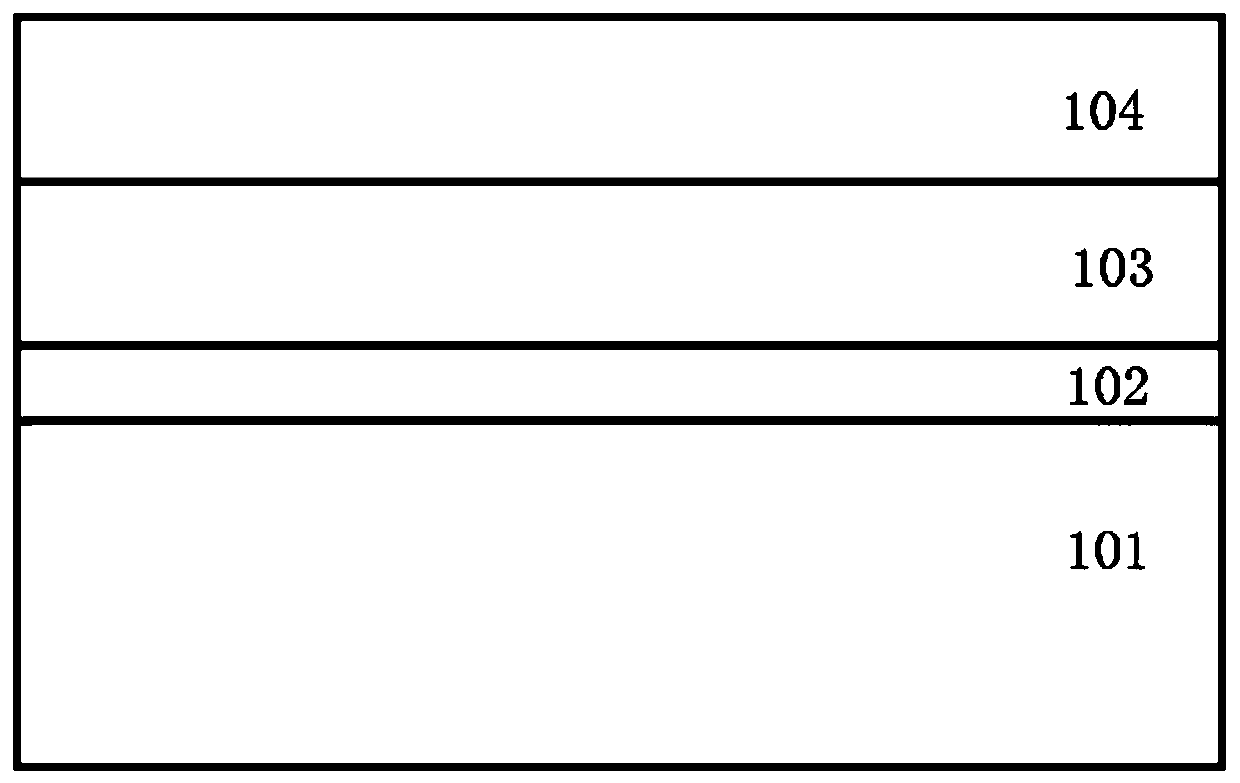

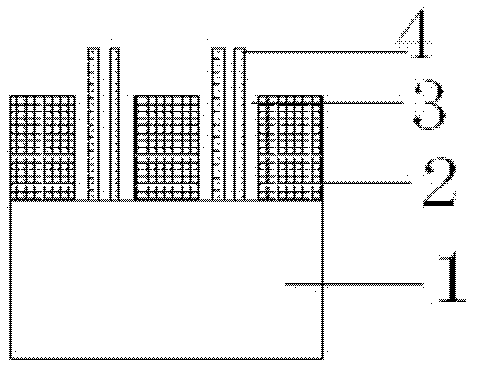

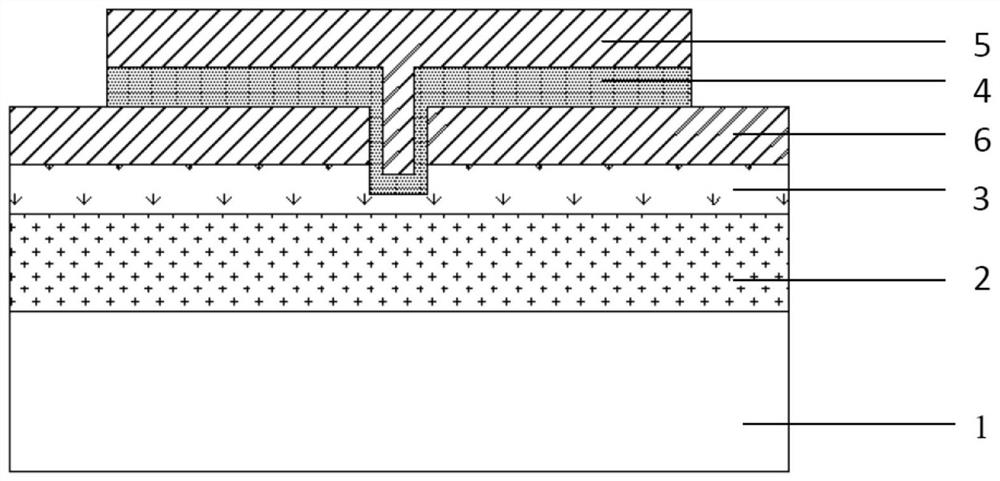

Double-T-shaped nano gate and preparation method thereof

ActiveCN110707150AImprove stabilityIncrease distanceFinal product manufactureSemiconductor/solid-state device manufacturingParasitic capacitorEngineering

The invention relates to the technical field of microelectronic devices, and particularly discloses a double-T-shaped nano gate and a preparation method thereof. The double-T-shaped nano gate grows ona substrate with a dielectric passivation layer, and the dielectric passivation layer comprises a bottom dielectric passivation layer and a top dielectric passivation layer; the double-T-shaped nanogate sequentially comprises a gate root, a gate waist and a gate cap from bottom to top. The gate root penetrates through the dielectric passivation layer and grows on the substrate, the gate root isnot in contact with the bottom dielectric passivation layer, and the lower surface of the gate waist is in contact with the upper surface of the top dielectric passivation layer. The grid root and thegrid cap of the double-T-shaped nano grid provided by the invention are suspended; the contact with the dielectric passivation layer is avoided; the top dielectric passivation layer is covered with the gate waist, the stability of the double-T-shaped gate is improved, the distance between the gate cap and the dielectric passivation layer is increased through the double-T-shaped structure, parasitic capacitance can be further reduced, gate inversion caused by the fact that no dielectric support exists during gate stripping is avoided, and the purpose of improving the frequency characteristic of the device is achieved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

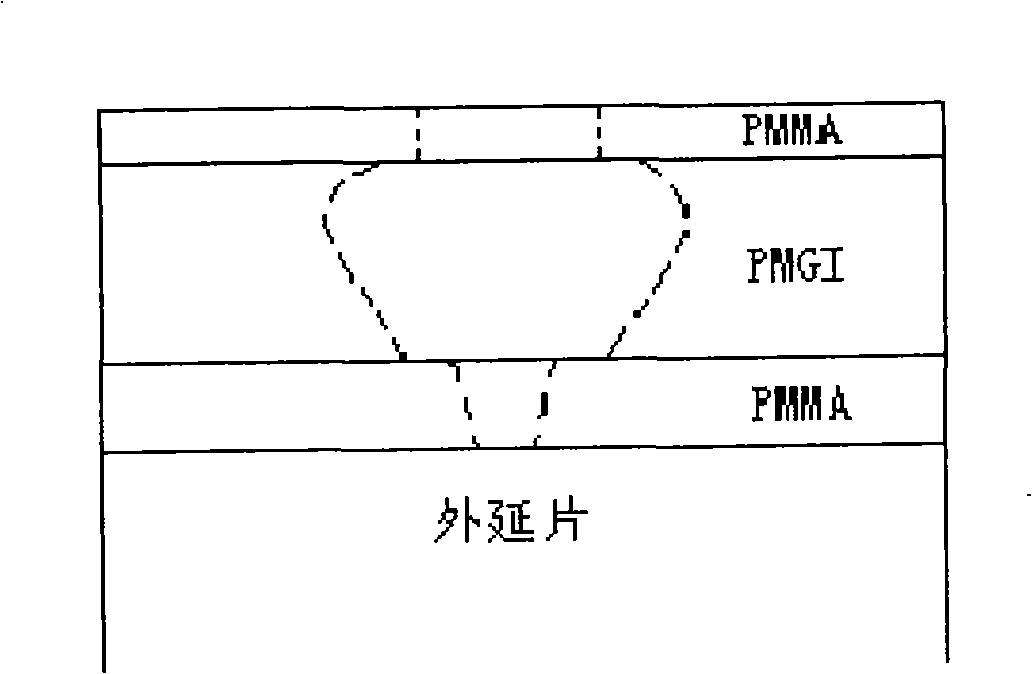

Method for preparing transistor T type nano grid

ActiveCN101276752AEasy to manufactureEasy to glueSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingElectron-beam lithography

The invention discloses a method for manufacturing transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue ZEP520A on the third layer electric beam glue, and then soft-baking; E, carrying out gate feet electric beam exposure; F, carrying out gate cap electric beam exposure; G, sequentially developing the four layer electric beam glue ZEP520A, the third layer electric beam glue, the second layer electric beam glue ZEP520A and the first layer electric beam glue; H, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. Usage of the invention can easily manufacture the gate lines having extremely small size, and the invention has high alignment precision and strong reliability without growth and etching mediums, thus largely reducing the process difficulty.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

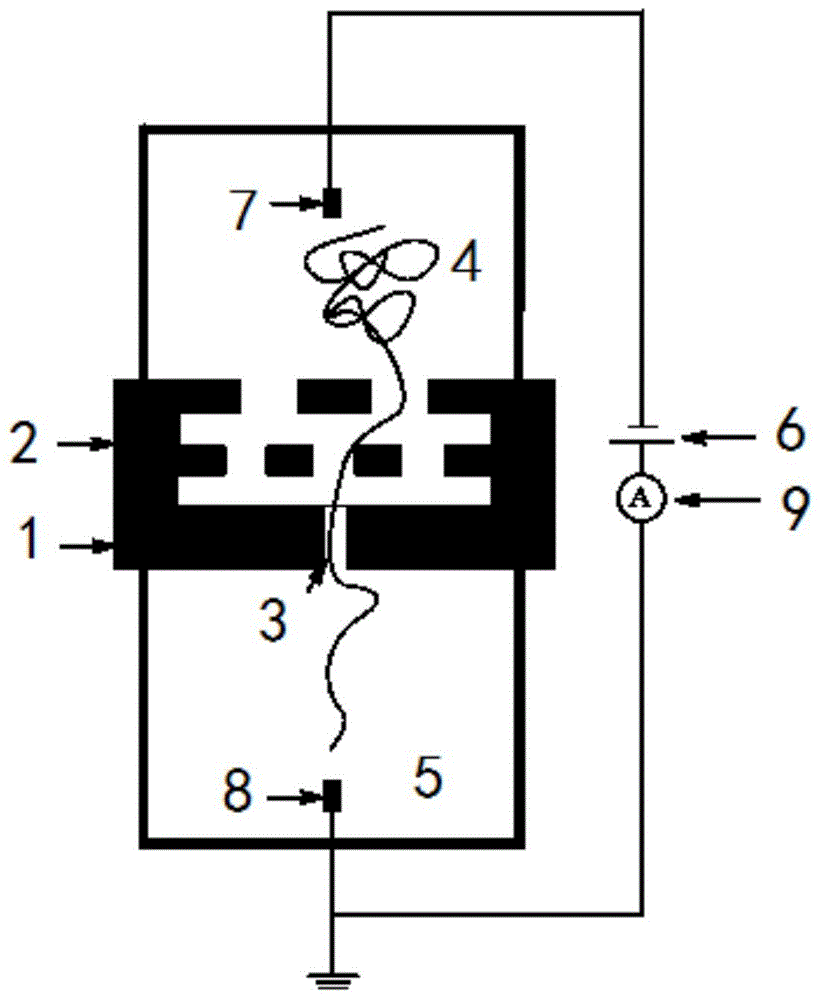

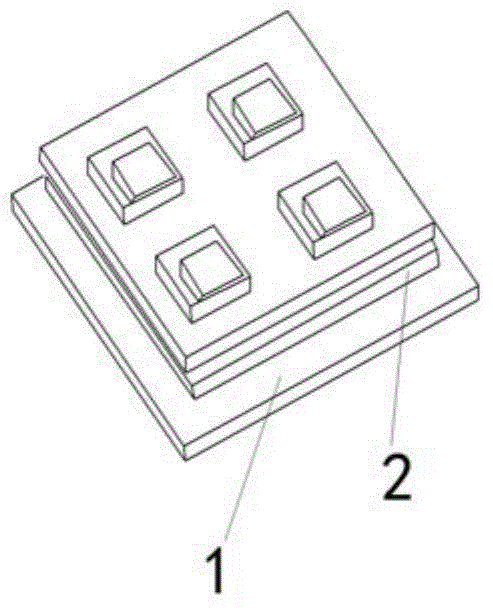

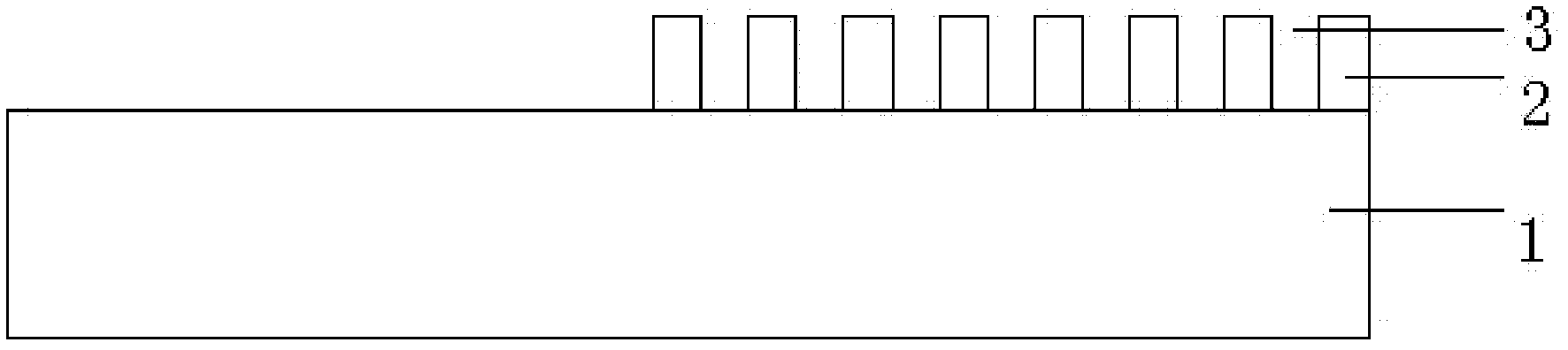

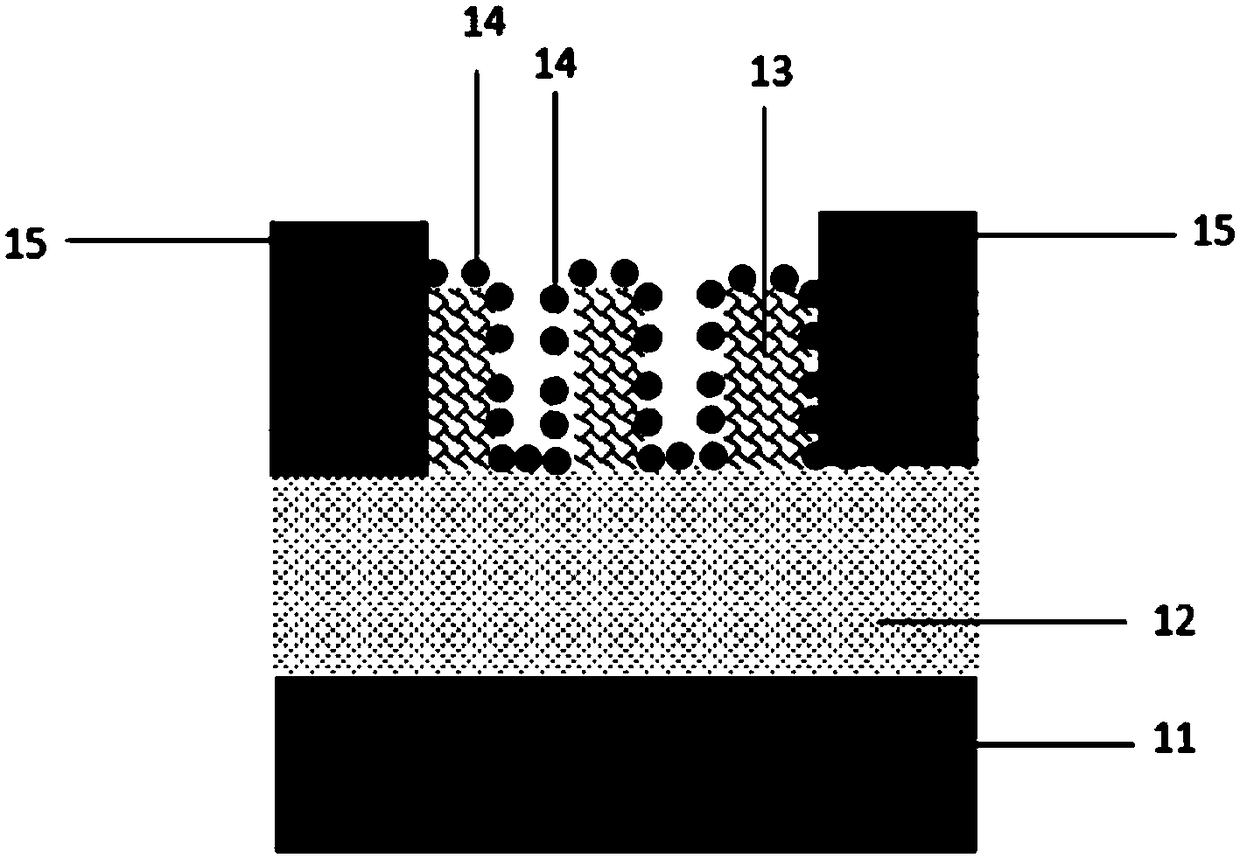

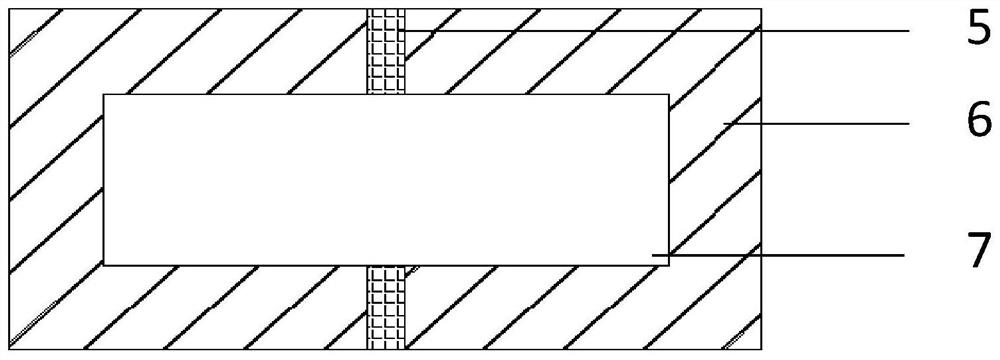

Nano hole detection system based on micro/nano hole net integrated structure and preparation method of nano hole detection system

ActiveCN104897728AImprove reliabilityReduced entropy barrierBioreactor/fermenter combinationsBiological substance pretreatmentsNano gridMicro nano

The invention discloses a nano hole detection system based on a micro / nano hole net integrated structure. The nano hole detection system comprises an electrolyte solution chamber, the micro / nano hole net integrated structure and current detection systems, wherein the micro / nano hole net integrated structure is arranged in the electrolyte solution chamber, and comprises a nano hole layer film with nano holes and a grid layer film with micro / nano grids; and the current detection systems are arranged in an upper chamber and a lower chamber of the electrolyte solution. According to the nano hole detection system disclosed by the invention, the micro / nano grid structures and the nano holes are connected and integrated together in a penetrating manner by fully utilizing the advantages of a semiconductor integration technology; the nano hole detection system conforms to the development tendencies of miniaturization and integration of a long-chain polymer sequencing technology; a long-chain polymer is linearized, so that the long-chain polymer can stretch as far as possible before entering the nano hole; the entangled state of the long-chain polymer is unlocked; the entropy barrier of the long-chain polymer when passing through the nano holes is reduced; the phenomenon that the nano holes are blocked is avoided; and the reliability of detecting the long-chain polymer by the nano holes can be effectively improved.

Owner:CHONGQING INST OF GREEN & INTELLIGENT TECH CHINESE ACADEMY OF SCI

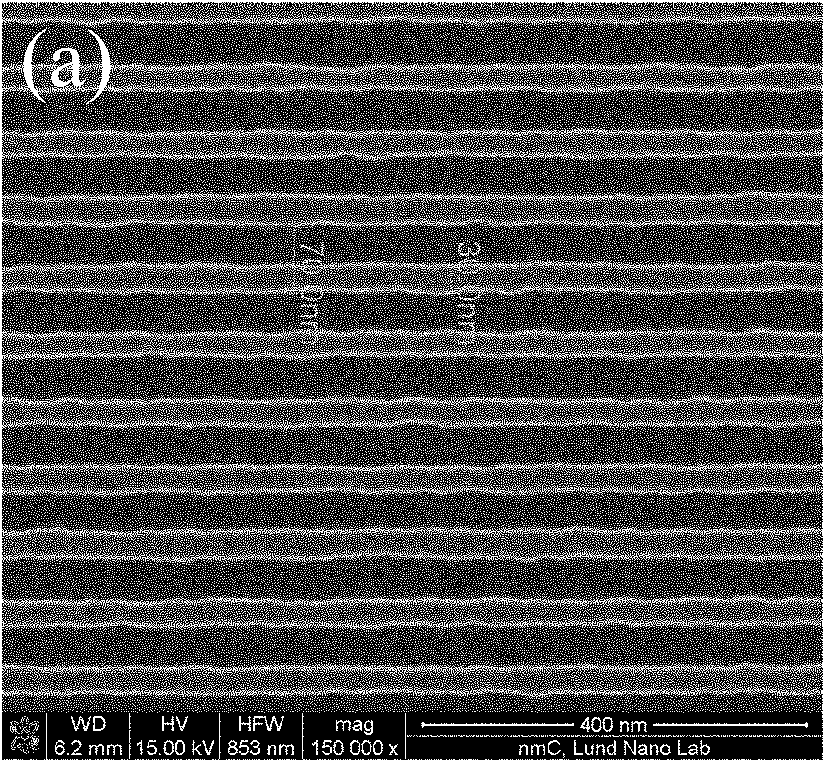

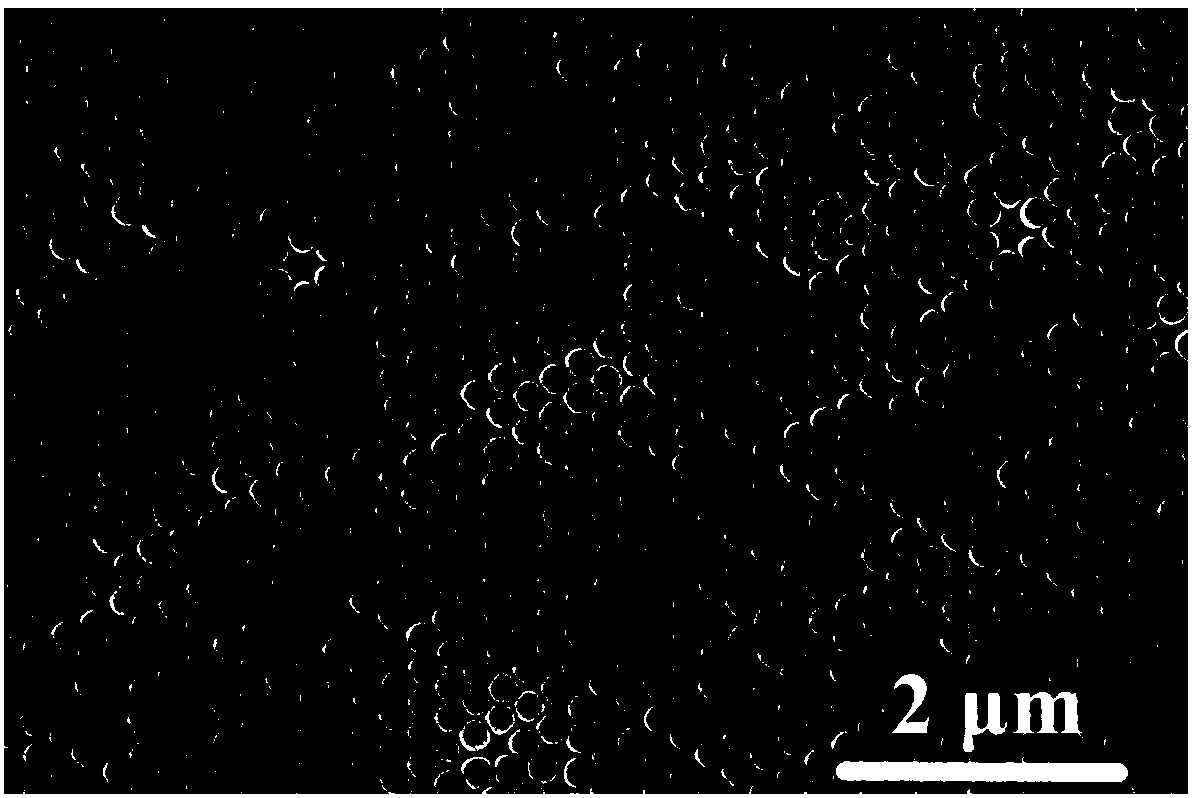

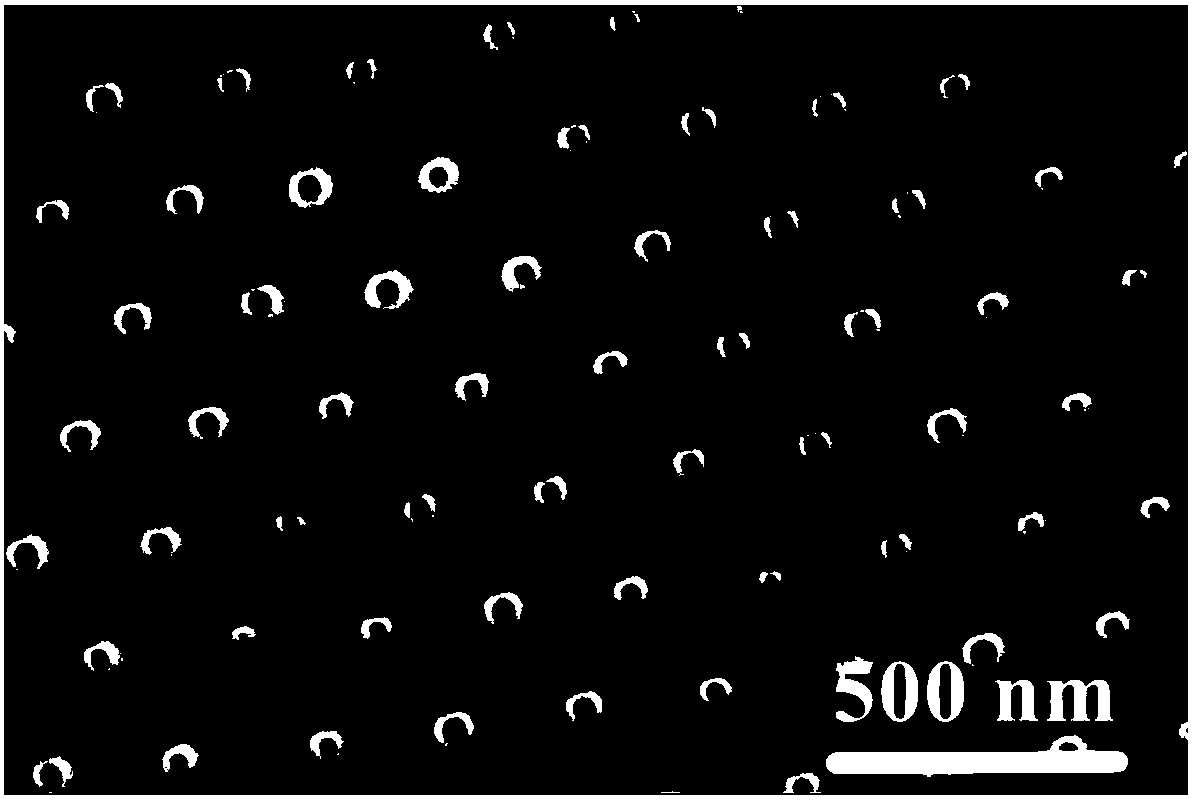

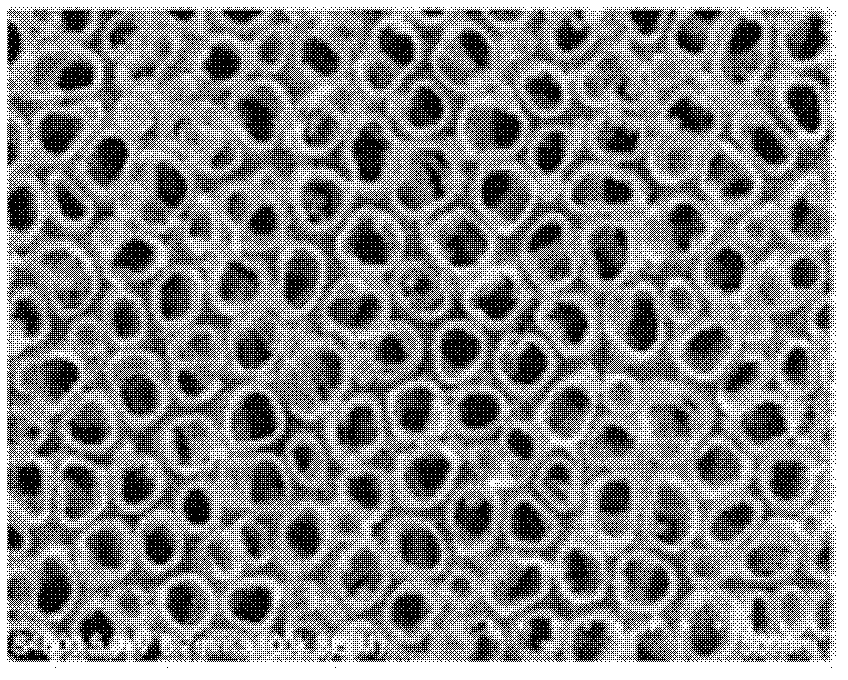

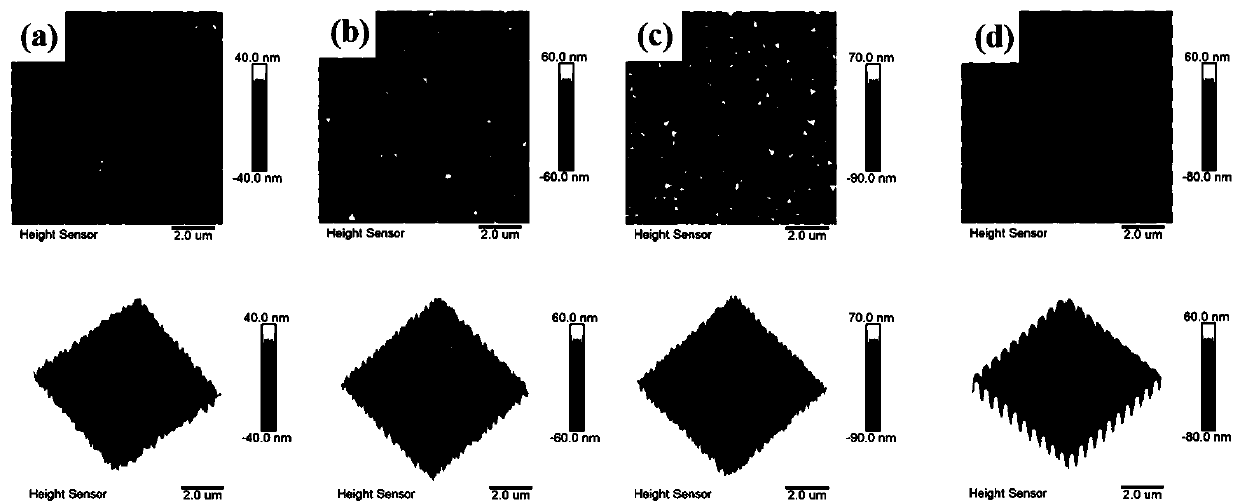

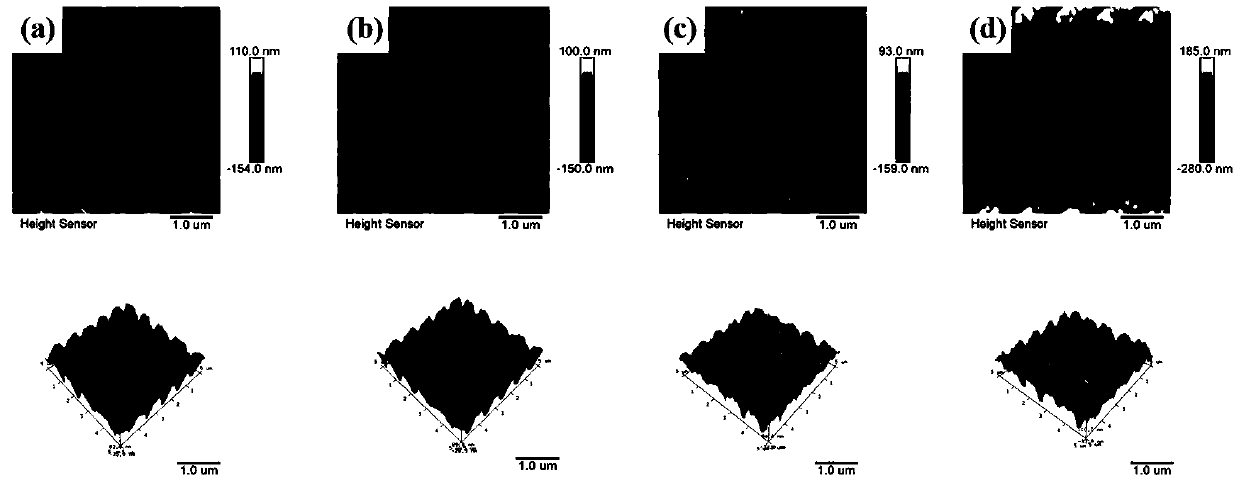

Preparation method of non-dense ordered polystyrene nanosphere template

InactiveCN108373136AEffective control of etching precisionImprove stabilityNanostructure manufactureNanowirePolystyrene

The invention relates to a preparation method of a non-dense ordered polystyrene nanosphere template, and belongs to the technical field of preparation of nanometer structures. The preparation methodspecifically comprises the following steps of after a silicon wafer is cleaned, passivating the surface of the silicon wafer by hydrogen; self-assembling a single-layer dense polystyrene nanosphere thin film on the silicon wafer, and utilizing normal incidence type Ar<+> ion beams to bombard the nanosphere thin films of different diameters, wherein the density of beam flow is 0.85 to 3.0mA / cm<2>,the energy of Ar<+> is 0.5 to 1.0keV, and the bombarding time is 5 to 28min; after bombarding by the ion beams, the diameter of each nanosphere is reduced, and the location of each nanosphere is not changed, so as to obtain the non-dense ordered polystyrene nanosphere template. The preparation method of the non-dense ordered polystyrene nanosphere template has the advantages that the size and cycle of the nanoparticle in the template are adjusted by the initial diameter and bombarding condition of the polystyrene nanosphere; the etching rate of the nanosphere is adjustable within the range of6.19 to 17.32nm / min; compared with the ion beam etching technique, the etching rate is low, and the quality of the small-size polystyrene nanosphere template is favorably controlled; the cost is low,the technology is simple, and the stability is high; the non-dense ordered polystyrene nanosphere template can be applied to the study and development fields of ordered nanowires, nanorods, nanoporesand nanomesh arrays.

Owner:YUNNAN UNIV

Dye sensitized solar cell photoanode, cell and manufacturing method of photoanode

InactiveCN102568850ALarge specific surface areaImprove adsorption capacityLight-sensitive devicesSolid-state devicesTio2 nanotubeOptoelectronics

The invention relates to a dye sensitized solar cell photoanode, a cell and a manufacturing method of the photoanode. The dye sensitized solar cell photoanode comprises a Ti substrate, a TiO2 nano grid layer and a TiO2 nanotube array, wherein the TiO2 nano grid layer is positioned on the Ti substrate; nanotubes of the TiO2 nanotube array respectively grow on the Ti substrate and pass through the TiO2 nano grid layer. According to the dye sensitized solar cell photoanode, the cell and the manufacturing method of the photoanode, the adsorption capability of TiO2 to dye is improved, and thus the performance of the dye sensitized solar cell photoanode is improved; in addition, electrons can be captured by the TiO2 nanotubes, and the electron transmission rate is increased.

Owner:上海联孚新能源科技集团有限公司

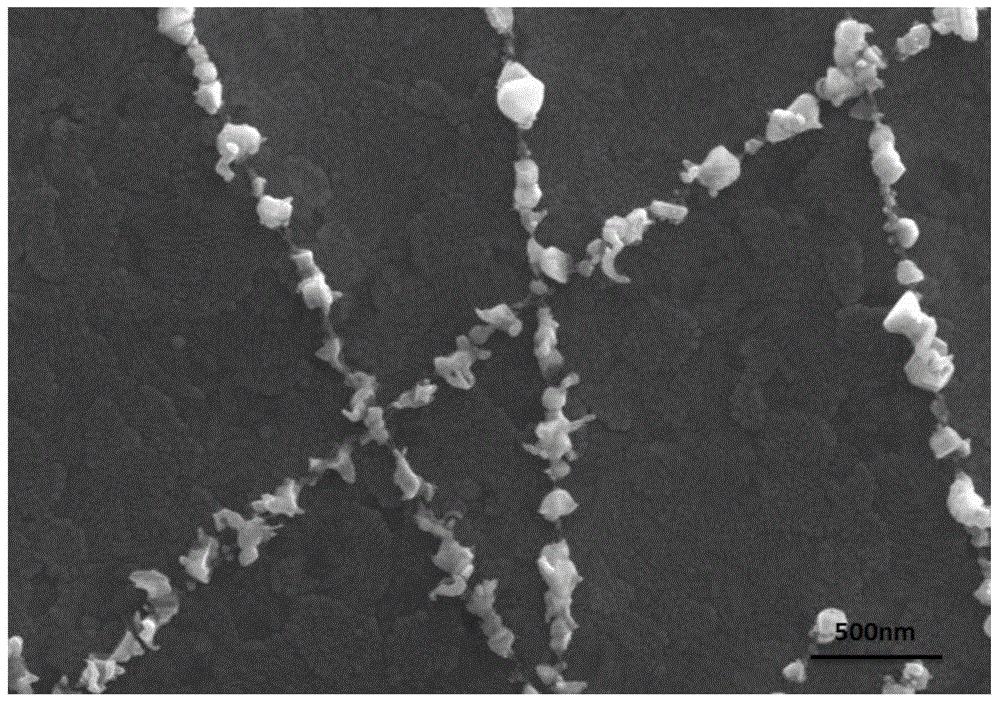

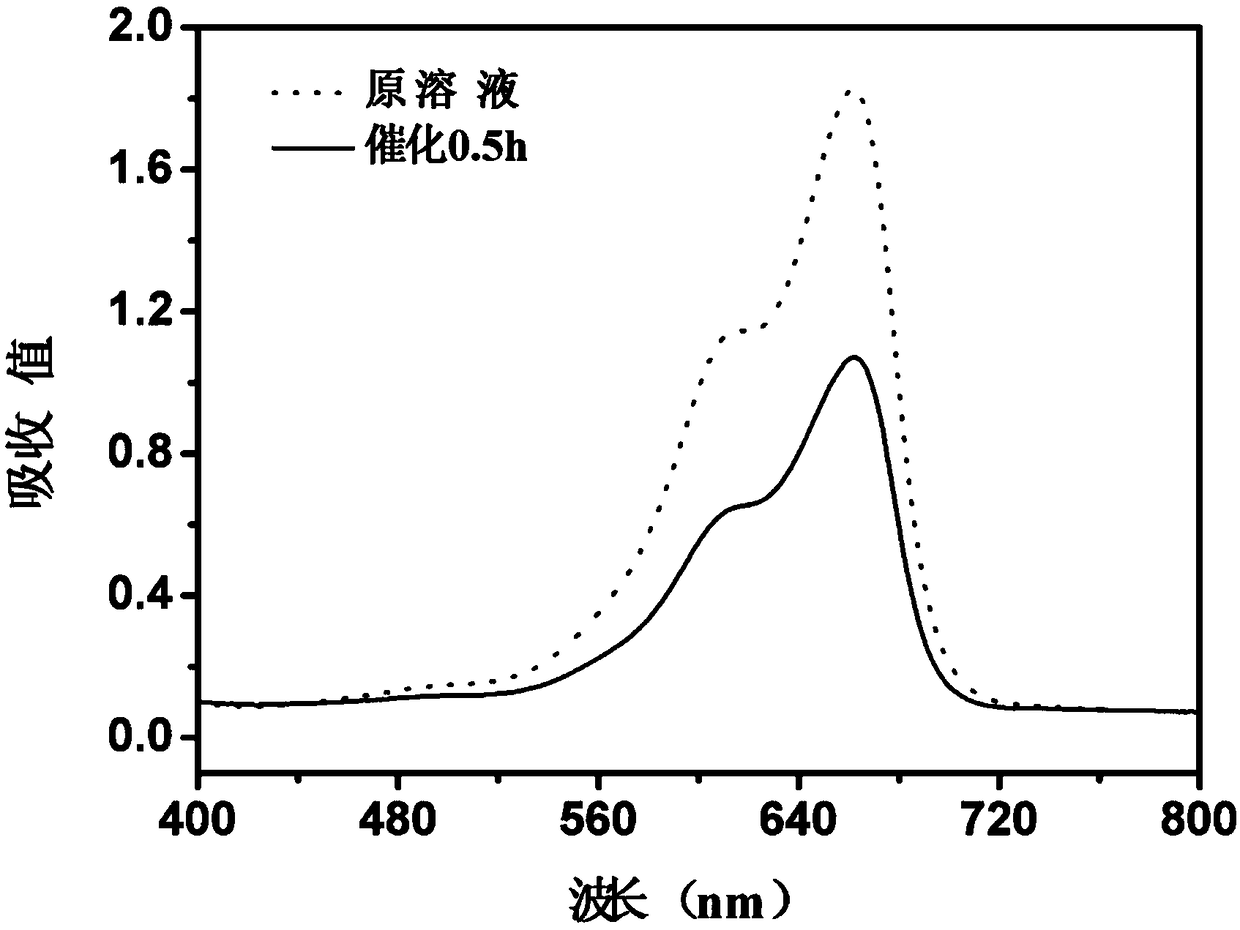

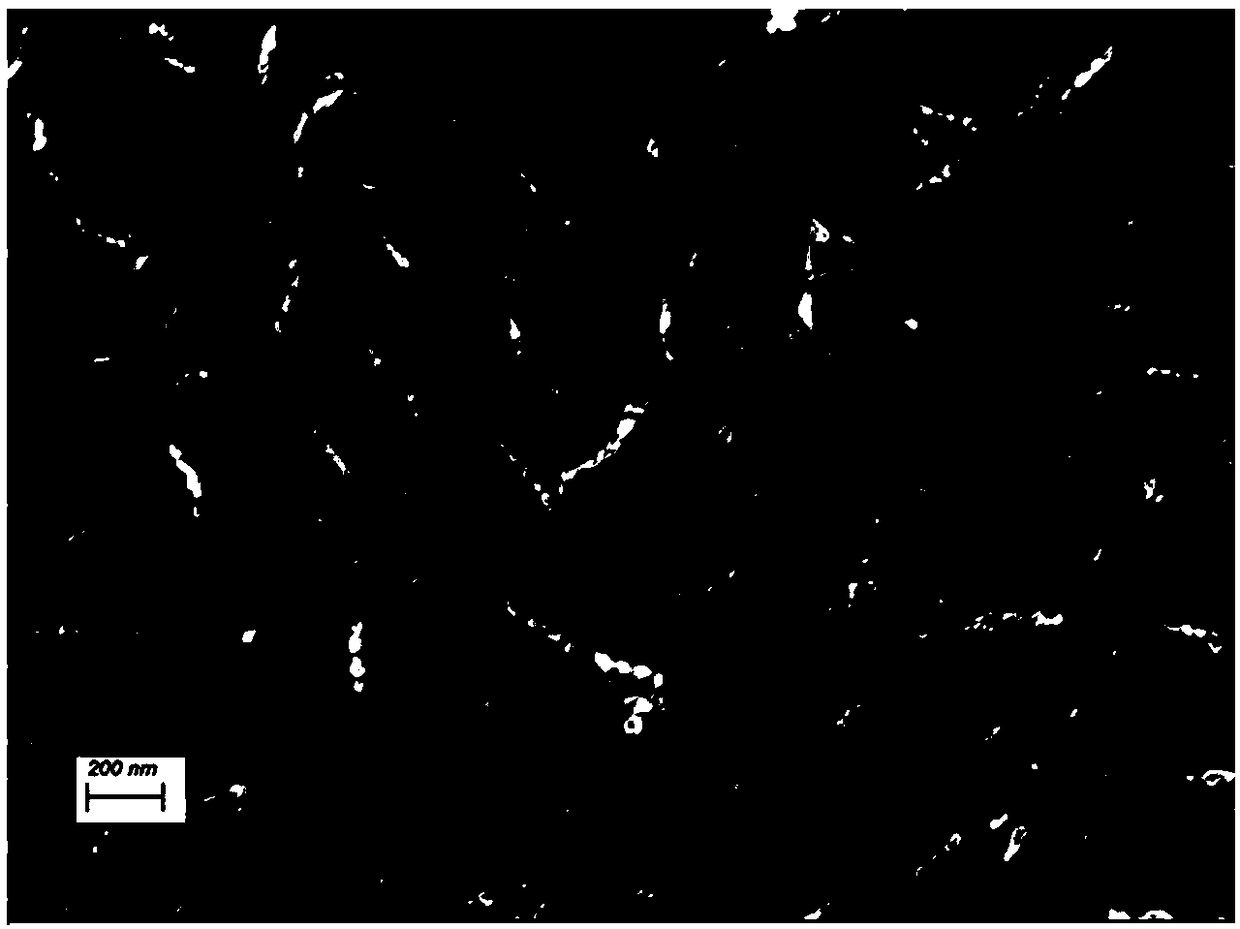

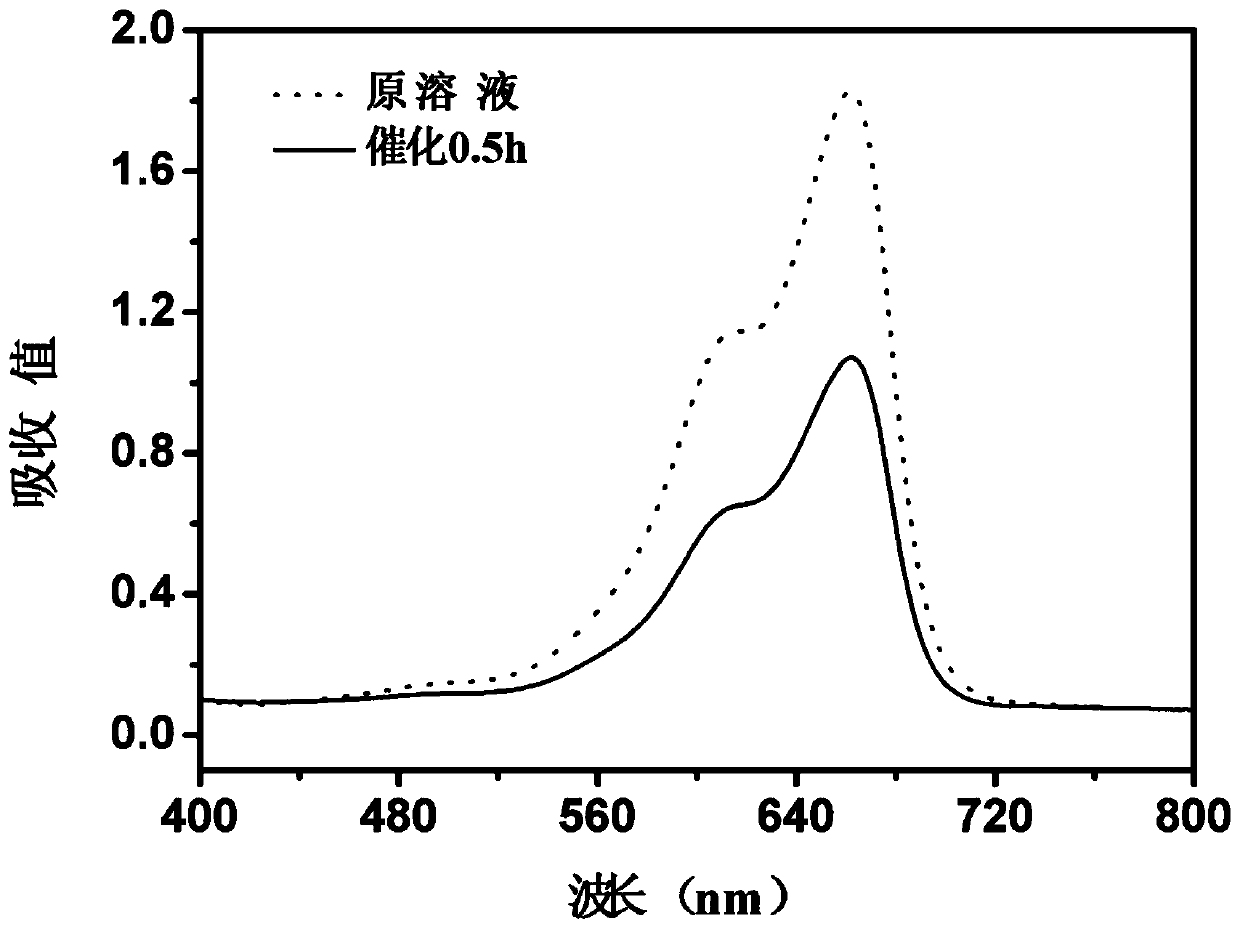

An ultraviolet photoelectric detector based on a ZnO nano-grid and a preparation method thereof

ActiveCN109103277AExcellent photoelectric response performanceReduce manufacturing costMaterial nanotechnologyFinal product manufacturePhotovoltaic detectorsUltraviolet

The invention relates to an ultraviolet photoelectric detector based on ZnO nano-grid and a preparation method thereof. The ultraviolet photoelectric detector based on the ZnO nano-grid is prepared through the steps of preparing a mixed solution, a multilayer thin film, high-temperature sintering, metal nanometer particles, electrodes and the like. As the preparation method of the invention has wide application range, the preparation of the ultraviolet photoelectric detector based on the ZnO nano-grid can be realized on a plurality of large-size substrates, the production cost is reduced, themanufacturing equipment is simple, the process is mature, and the large-scale production is convenient. In addition, the photoelectric response performance of the ultraviolet photoelectric detector ofthe invention is excellent.

Owner:WUYI UNIV

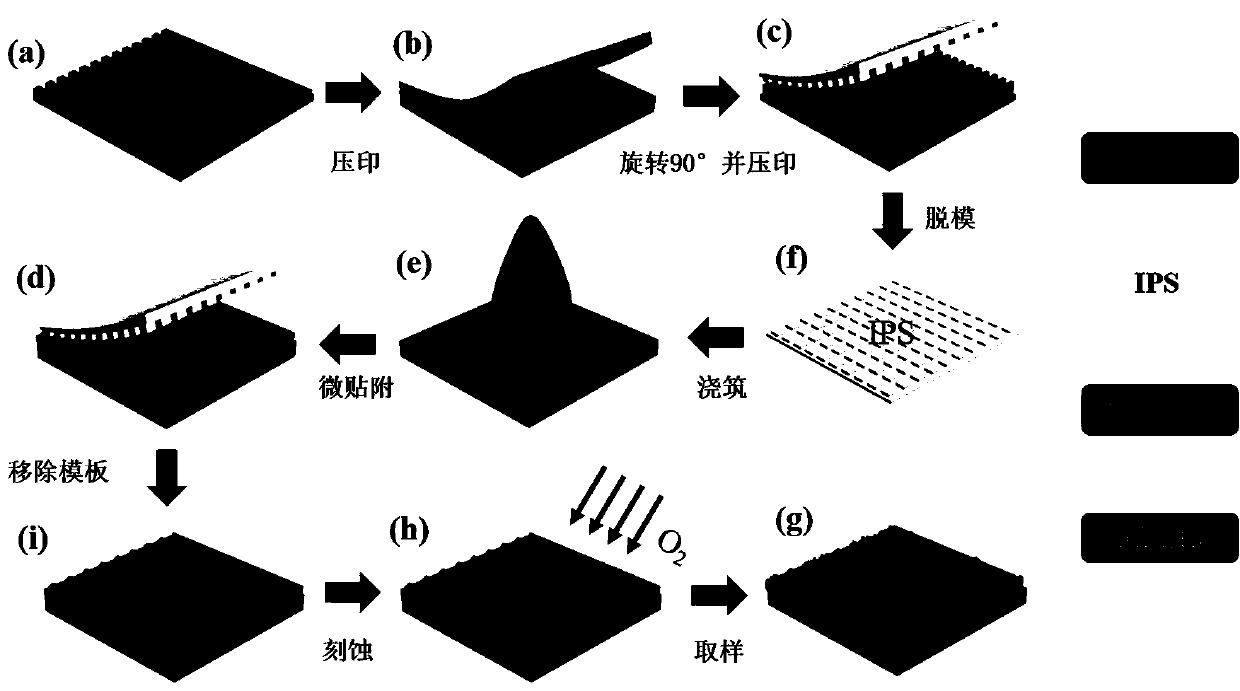

QLED device with enhanced composite structure and preparation method of QLED device

ActiveCN110120461ASimple processLow costSolid-state devicesSemiconductor/solid-state device manufacturingMicro nanoSurface plasmon

The invention provides a QLED device with an enhanced composite structure and a preparation method of the QLED device. The light emitting efficiency of a positive QLED device is improved through a micro-nano structure composite structure constructed by a nano grid structure composite folded structure. The composite structure is constructed on the basis of the nanoimprint technology, the micro-attachment technology and the surface plasma etching technology, and the method comprises the steps: preparing a nanoimprint template and processing the transferred pattern again. An IPS polymer is used as a nano-imprinting template through the nano-imprinting technology, and the template pattern is transferred to the PDMS dielectric layer through the micro-attachment technology; on the basis, the composite structure is constructed on the glass substrate through the surface plasma etching technology to enhance light emitting of the QLED substrate. The QLED device with the enhanced composite structure can have the highest brightness and efficiency, and the brightness and the EQE are improved by 46% at most compared with conventional devices; and the construction mode of the composite structureis simple, the cost is low, and industrial popularization and application are facilitated.

Owner:HENAN UNIVERSITY

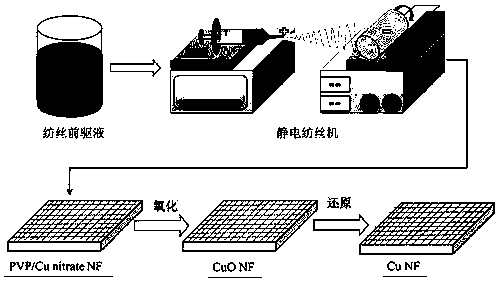

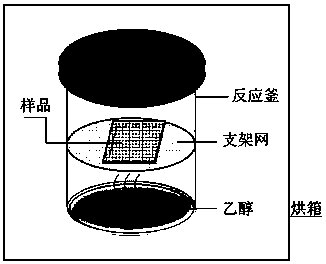

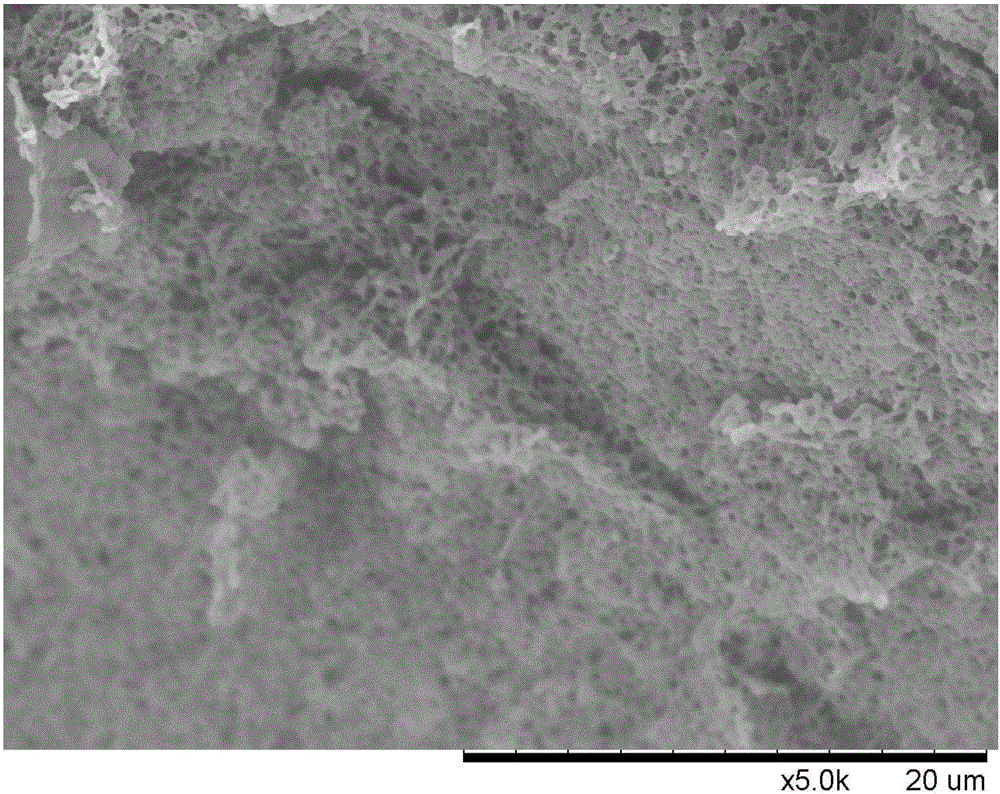

Method for preparing copper nano grid transparent electrode based on gas phase reduction of copper oxide

ActiveCN109686497AImprove performancePreserve shapeApparatus for heat treatmentAlcohol reductionNanowire

Owner:TAIYUAN UNIV OF TECH

A kind of preparation method of nanogrid Octogen

ActiveCN103626711BMild reaction conditionsReduce manufacturing costOrganic chemistryNanotechnologyMicro structureGram

The invention discloses a preparation method of nano grid octogen, which comprises the steps of adding a HMX / DMSO complex into pure water or a surfactant solution, stirring for certain time, filtering, washing and drying to obtain nano grid octogen powder with different micro structures. The method is used for quickly preparing nano grid octogen based on the HMX / DMSO complex, and can realize preparation from gram level to kilogram level; expensive large equipment is not required; the method is performed under room temperature conditions, and reaction conditions are mild; the preparation cost is low.

Owner:INST OF CHEM MATERIAL CHINA ACADEMY OF ENG PHYSICS

Method for producing transistor T type nano grid using once electron beam exposure

InactiveCN100511596CEasy to manufactureNo sleeve alignment issuesPhotomechanical apparatusSemiconductor/solid-state device manufacturingCooking & bakingElectron-beam lithography

The invention discloses a method for using once electric beam exposure to manufacture transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue ZEP520A on the third layer electric beam glue, and then soft-baking; E, carrying out gate electric beam exposure; F, sequentially developing the four layer electric beam glue ZEP520A, the third layer electric beam glue which is liable to realize glue-stripping and peeling, the second layer electric beam glue ZEP520A and the first layer electric beam glue which is liable to realize glue-stripping and peeling; G, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. The invention has strong reliability, simple processes and is easy to peel off and strip the glue.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of zno nanometer material, and preparation method thereof

ActiveCN108821326BThe preparation equipment is matureSimple processMaterial nanotechnologyZinc oxides/hydroxidesDopantMicrosphere

The invention provides a ZnO nanomaterial and a preparation method thereof. The material includes a substrate layer, a nanowall formed by stacking ZnO nanowires and a nanogrid composed of nanowalls arranged on the substrate layer. Specifically, It includes the following steps: 1), using zinc acetate, pore-forming agent, and dopant to prepare a precursor mixed solution; 2), using the precursor mixed solution to prepare a precursor film; 3), high-temperature sintering to obtain ZnO nanomaterials; prepared by the present invention The equipment is mature, the process is simple, and it is convenient for large-scale production; by accurately controlling the sintering temperature, and using zinc acetate and pore-forming agents to decompose into water and carbon dioxide, and separate them from the microspheres, it helps to form pores and nanowires; during the 500°C insulation stage , the precursor will be completely decomposed and promote the crystallization of ZnO nanowires, thereby obtaining ZnO nanomaterials with good crystallization state. The size of the prepared microspheres is controllable and the pore distribution is uniform; the ZnO nanomaterials prepared by the present invention have a wide application range.

Owner:WUYI UNIV

Method for preparing transistor T type nano grid

ActiveCN100543940CEasy to manufactureLoose conditionsSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingElectron-beam lithography

The invention discloses a method for manufacturing transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue UVIII on the third layer electric beam glue, and then soft-baking; E, carrying out gate cap electric beam exposure, and sequentially developing the four layer electric beam glue UVIII, the third layer electric beam glue which is liable to realize glue-stripping and peeling; F, carrying out the gate feet electric beam exposure, and sequentially developing the second layer electric beam glue ZEP520A and the first layer electric beam glue which is liable to realize glue-stripping and peeling; G, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. Usage of the invention can easily manufacture the gate lines having small size, greatly reducing the process difficulty.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A method for preparing a transparent conductive nanowire grid film on a three-dimensional microstructure surface

ActiveCN109950366BGuaranteed light transmissionGuaranteed electrical conductivityFinal product manufactureNanotechnologyNanowireThin membrane

Owner:XIAN TECH UNIV

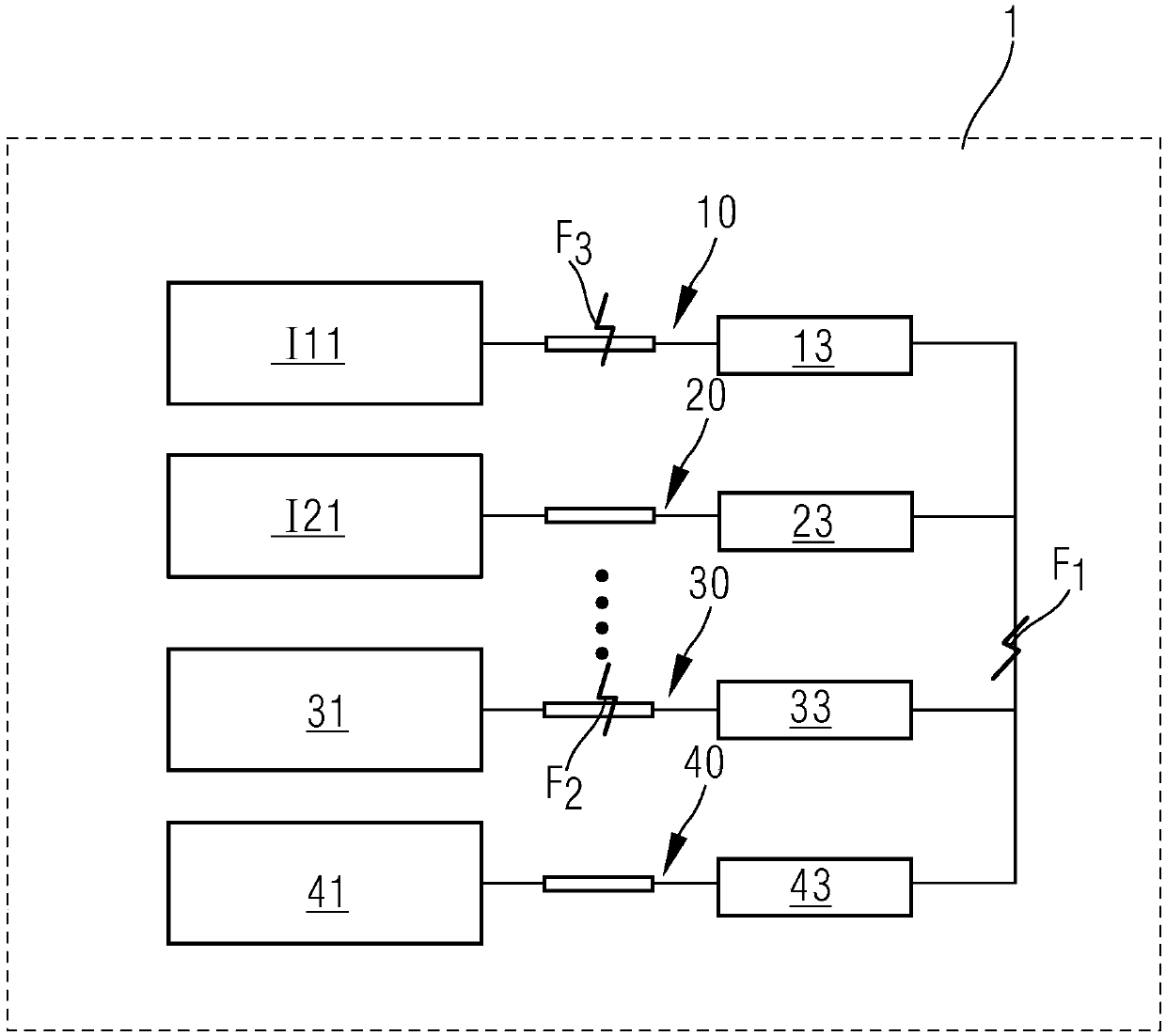

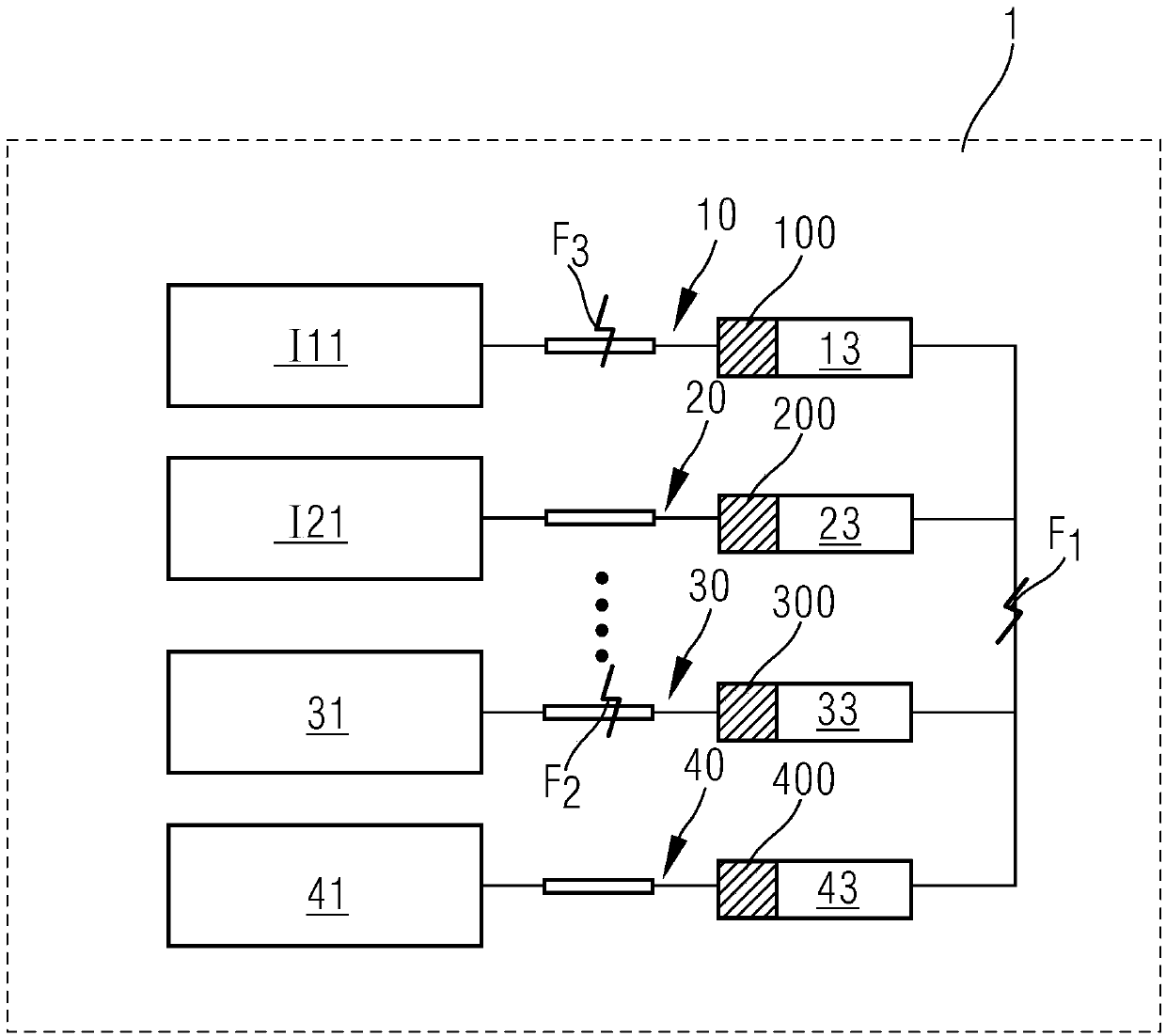

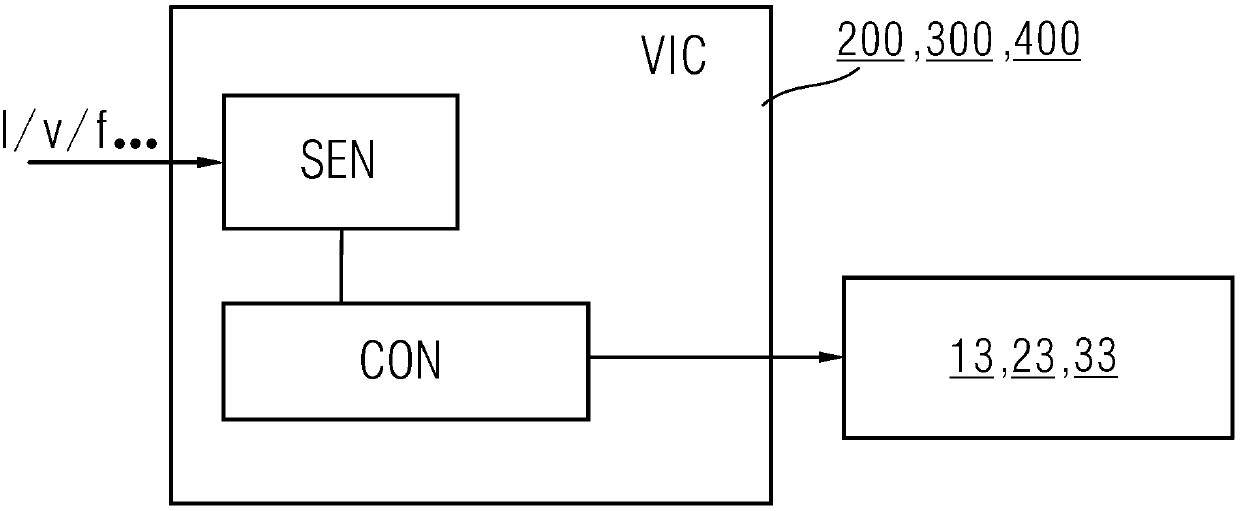

Virtual inverter control device used for nano grid, and nano grid

PendingCN109995069ASingle network parallel feeding arrangementsInformation technology support systemElectricityFeature parameter

The invention provides a nano grid and a virtual inverter control device (VIC, 100, 200, 300) for the nano grid (1), wherein the nano grid (1) comprises at least one parallel branch (10, 20, 30, 40),wherein at least one branch of the branch (10, 20, 30, 40) is provided with a protection device (13, 23, 33, 43); the nano grid is characterized in that one of the protection devices is configured with one virtual inverter control device (VIC) ); the virtual inverter control device (VIC) comprises a sensor component (I210) capable of detecting at least one characteristic parameter on the branch, and a control component (230) capable of influencing the electric connection state of the protection device corresponding to the inverter control device (VIC) according to the characteristic parameters.

Owner:SIEMENS AG

Method for preparing transistor T type nano grid

ActiveCN100524634CEasy to manufactureEasy to glueSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingElectron-beam lithography

The invention discloses a method for manufacturing transistor T-shaped nanometer gate, comprising the steps of: A, coating a first layer electric beam glue which is liable to realize glue-stripping and peeling on a cleaned epitaxial wafer, and then soft-baking; B, coating a second layer electric beam glue ZEP520A on the first layer electric beam glue, and then soft-baking; C, coating a third layer electric beam glue which is liable to realize glue-stripping and peeling on the second layer electric beam glue ZEP520A, and then soft-baking; D, coating a fourth layer electric beam glue ZEP520A on the third layer electric beam glue, and then soft-baking; E, carrying out gate feet electric beam exposure; F, carrying out gate cap electric beam exposure; G, sequentially developing the four layer electric beam glue ZEP520A, the third layer electric beam glue, the second layer electric beam glue ZEP520A and the first layer electric beam glue; H, eroding the gate groove, evaporating and peeling off gate metals to form the transistor T-shaped nanometer gate. Usage of the invention can easily manufacture the gate lines having extremely small size, and the invention has high alignment precision and strong reliability without growth and etching mediums, thus largely reducing the process difficulty.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A method for preparing a hemt device nano-gate

ActiveCN108470768BSimple processLow costSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireGallium nitride

The invention discloses a HEMT device nanometer grid electrode preparation method; in the HEMT device making process, an Ag nano wire is employed as a mask to make source drain electrode metal depositions; the method also comprises the steps of: using an NH3.H2O, H2O2, and H2O mixture solution ultrasonic cleaning method to remove Ag nano wire; forming a slit between the source electrode and drainelectrode, wherein the slit and the Ag nano wire are equivalent in dimensions; finally, making a nanometer grid electrode in the slit. The formed HEMT device has a low grid source conduction resistance, a high power density and frequency response, is simple in process, low in cost, and can provide important meanings for realizing a high performance nitride-based device.

Owner:SOUTH CHINA UNIV OF TECH