Method for preparing transistor T type nano grid

A transistor and nanotechnology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of poor adhesion, difficult to remove electron beam glue, affecting the exposure and development of gate feet, and achieve electron beam exposure. And the development conditions are loose, the development time is easy to control, and the development is easy to control.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

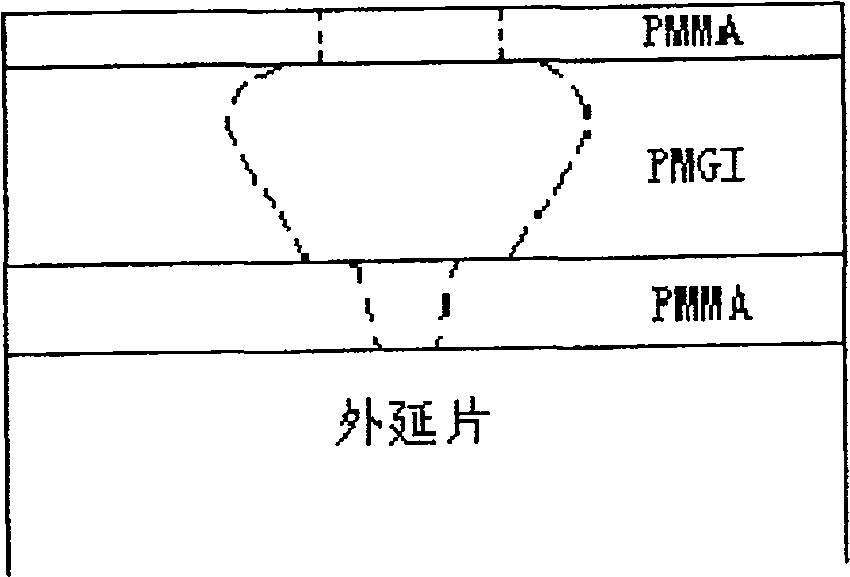

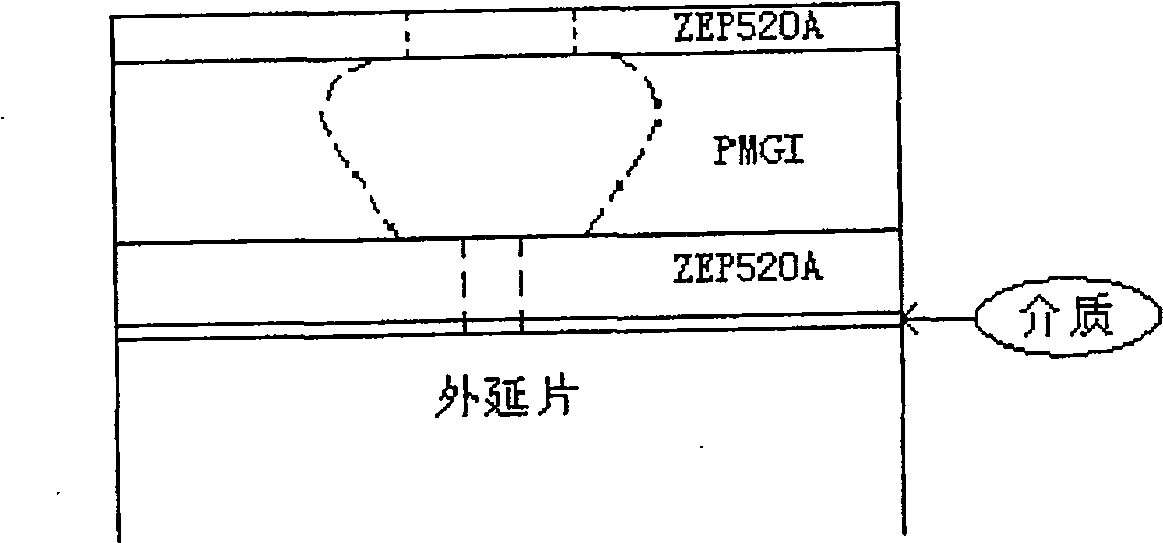

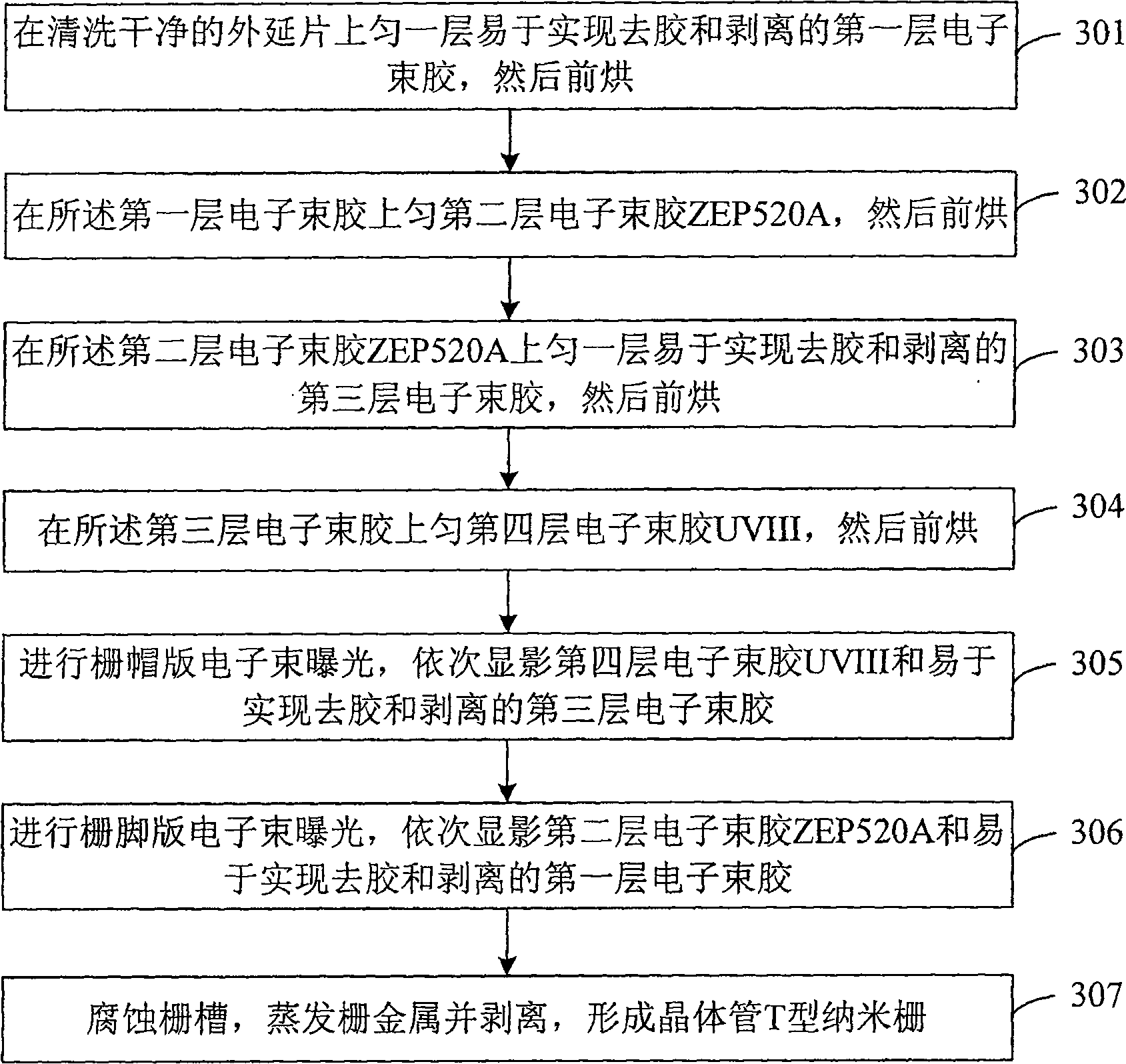

[0069] In this embodiment, the method for fabricating a high electron mobility transistor (HEMT) T-type nano-gate is aimed at some shortcomings in the current fabrication of a high electron mobility transistor (HEMT) T-type nano-gate. PMGI / ZEP520A / PMGI / UVIII four layers The electron beam photoresist structure (shown in Table 1) and two electron beam exposure methods were used to fabricate high electron mobility transistor (HEMT) T-type nano gates.

[0070] Table 1 is a schematic diagram of the PMGI / ZEP520A / PMGI / UVIII four-layer electron beam photoresist structure used in the method for fabricating a high electron mobility transistor (HEMT) T-type nano gate according to the present invention:

[0071]

[0072] Table 1

[0073] In this embodiment, the first layer of electron beam glue and the third layer of electron beam glue, which are easy to achieve stripping and stripping, are PMGI electron beam glue, which is used in the method of fabricating high electron mobility transistor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More