Method for preparing transistor T type nano grid

A transistor and nanometer technology, which is applied in the field of preparing T-type nano-gates of high electron mobility transistors, can solve the problems of increasing the alignment error of gate caps and gate feet, difficult control of thin line etching, and difficult removal of electron beam glue, etc., to achieve Easy to remove glue, easy to control the development time, easy to produce the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

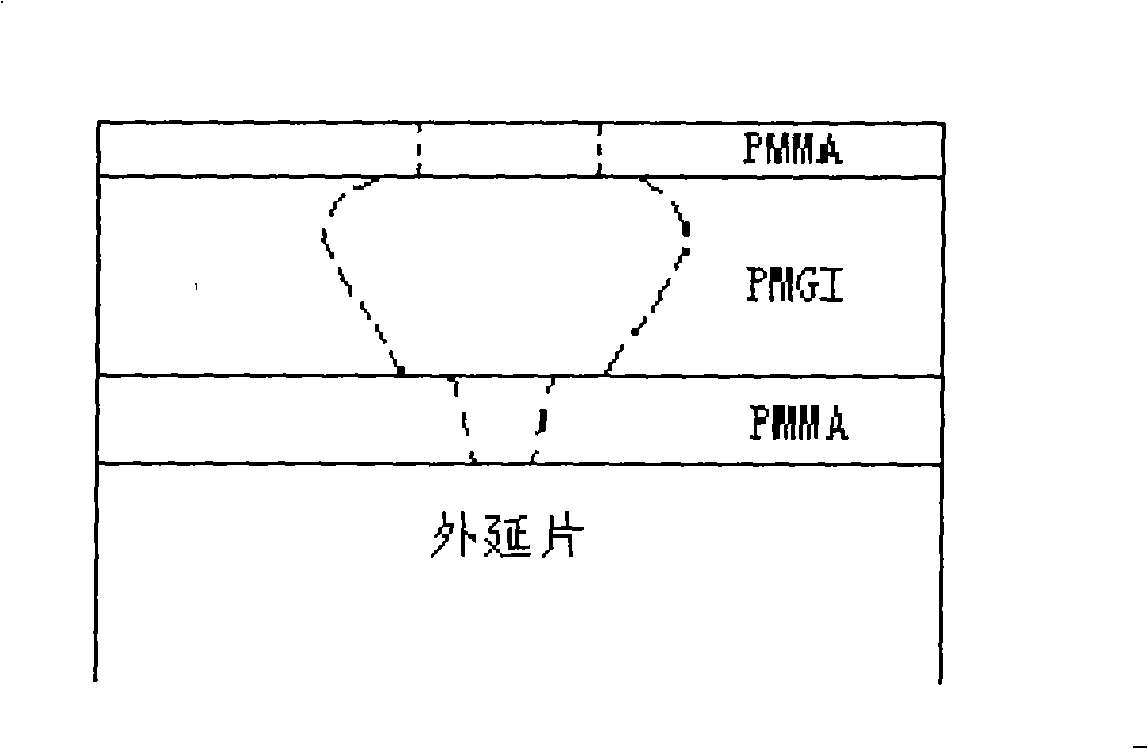

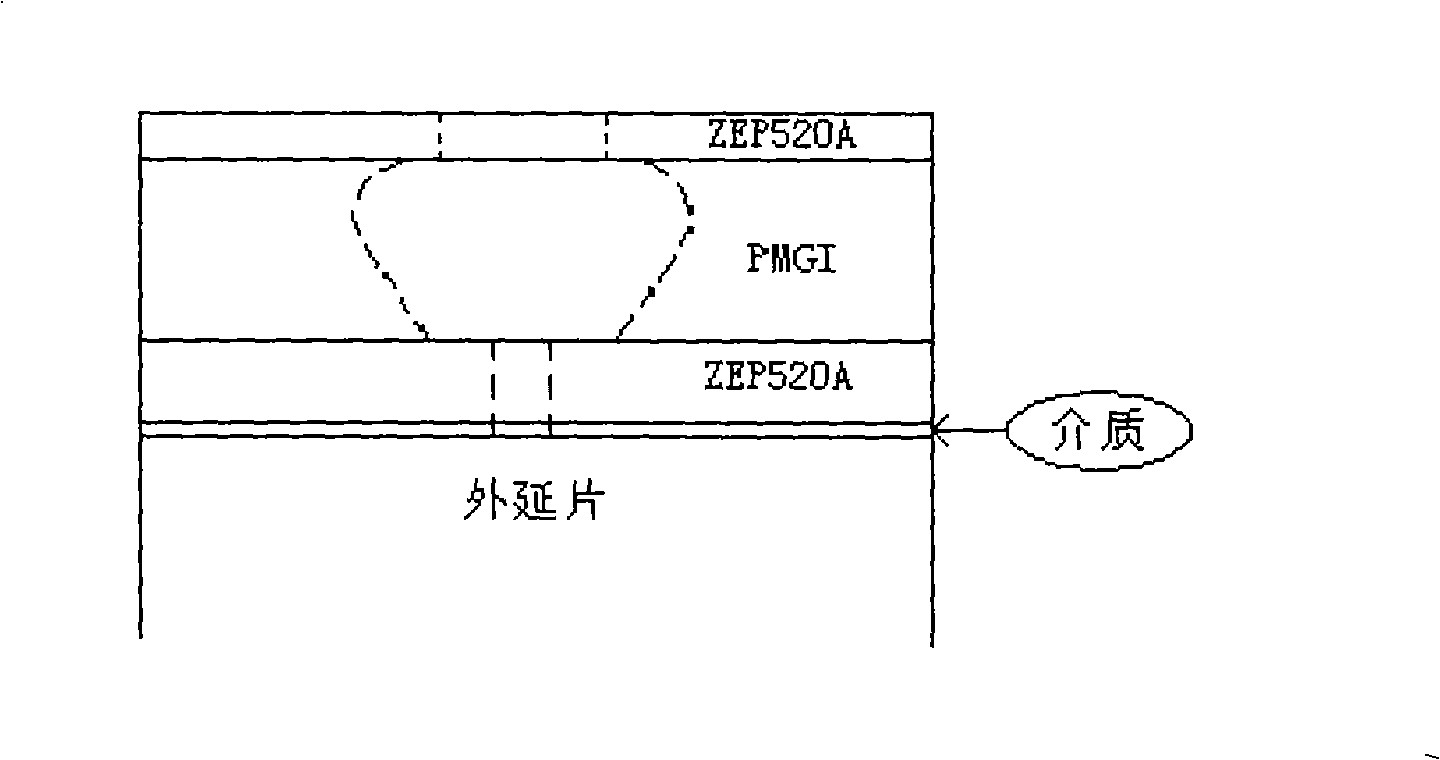

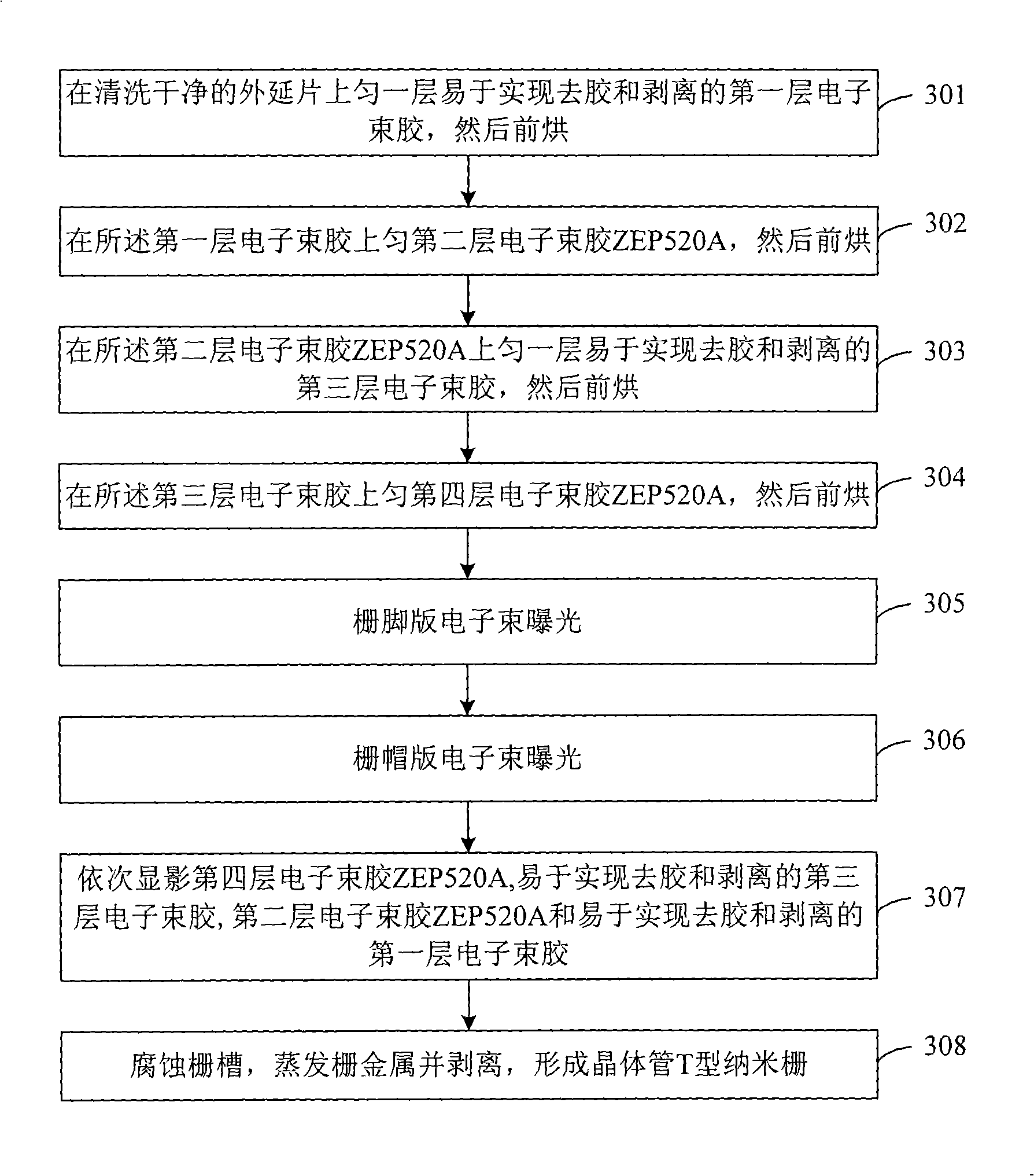

[0071] The method for preparing T-type nano-gates of high electron mobility transistors (HEMT) in this example is to address some shortcomings in the preparation of T-type nano-gates of high electron mobility transistors (HEMTs), using four layers of PMGI / ZEP520A / PMGI / ZEP520A Electron beam photoresist structure (as shown in Table 1) and two electron beam exposure methods to prepare high electron mobility transistor (HEMT) T-type nano-gate.

[0072] Table 1 is a structural representation of the PMGI / ZEP520A / PMGI / ZEP520A four-layer electron beam photoresist used in the method for preparing a high electron mobility transistor (HEMT) T-type nano-gate of the present invention:

[0073]

[0074] Table 1

[0075] In this embodiment, the first layer of electron beam glue and the third layer of electron beam glue that are easy to realize deglue and stripping are PMGI electron beam glue, which is used in the preparation method of high electron mobility transistor (HEMT) T-type nano-g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More