Fractional frequency all-digital phase-locked loop and control method thereof

An all-digital phase-locked loop, fractional technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of limiting the energy efficiency and performance of the phase-locked loop, deterioration of the noise performance of the phase-locked loop, and unstable loop operation. Reduced design difficulty and power consumption, reduced requirements, easy-to-implement effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

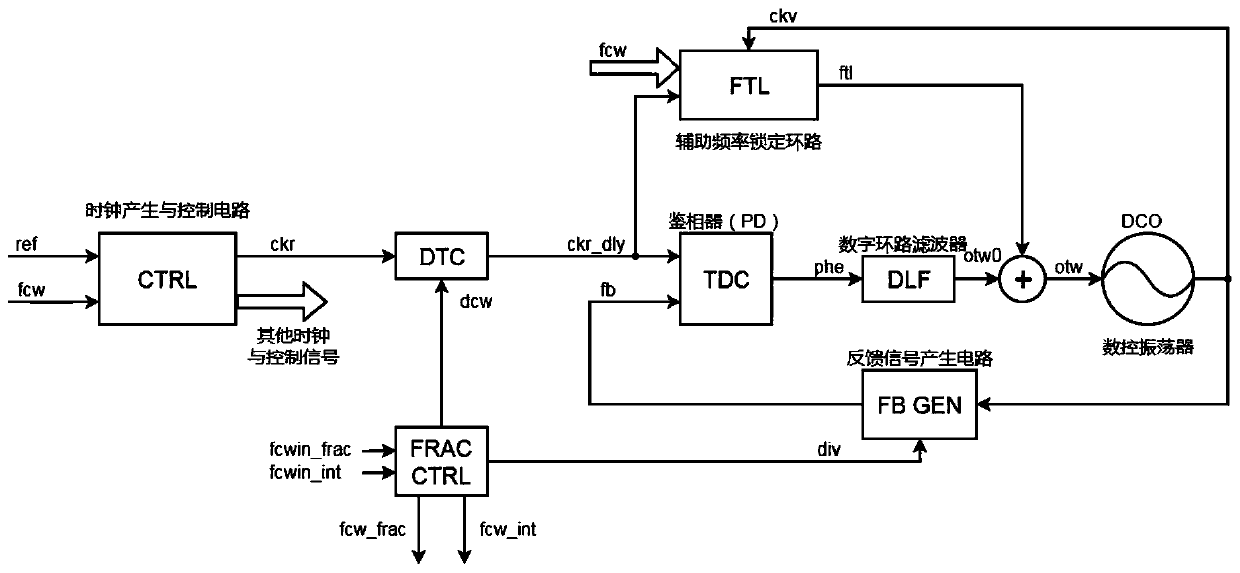

[0050] The present invention provides a fractional frequency all-digital phase-locked loop, such as figure 1 shown, including:

[0051] The clock generation and control circuit CTRL is used to generate the clock signal ckr required for the correct operation of the phase-locked loop according to the input reference clock ref, the integer frequency control word fcw_int, and the fractional frequency control word fcw_frac;

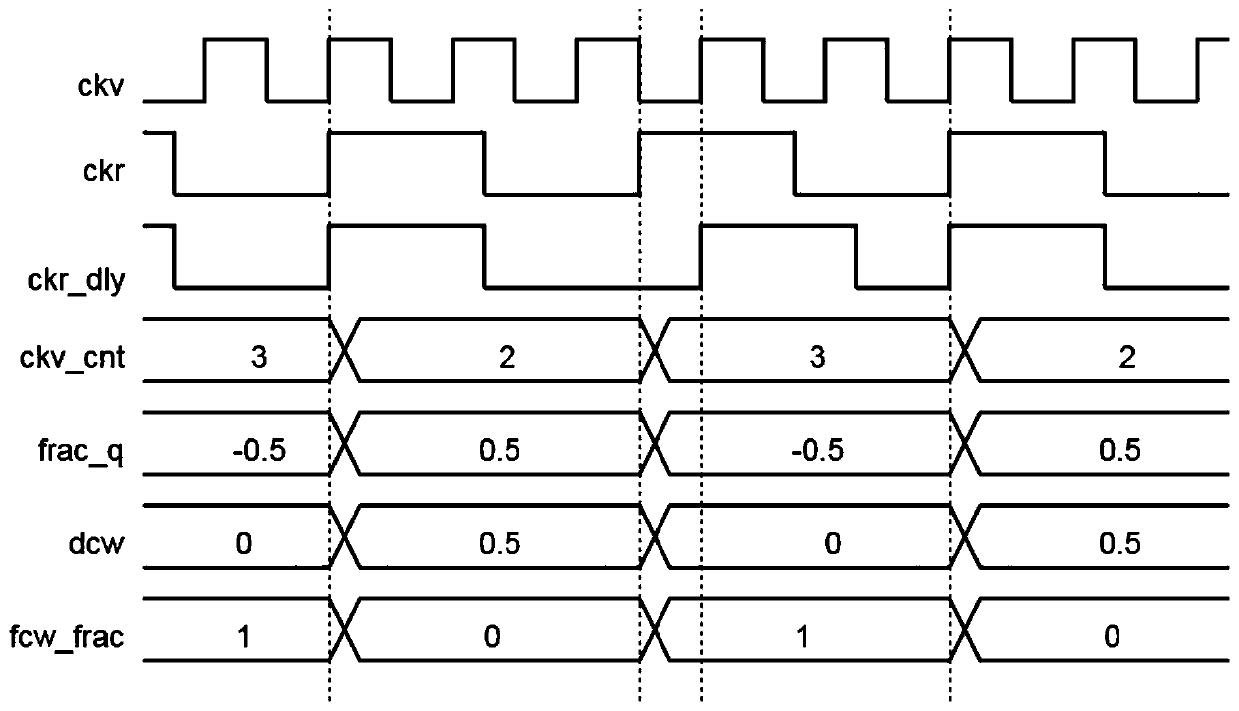

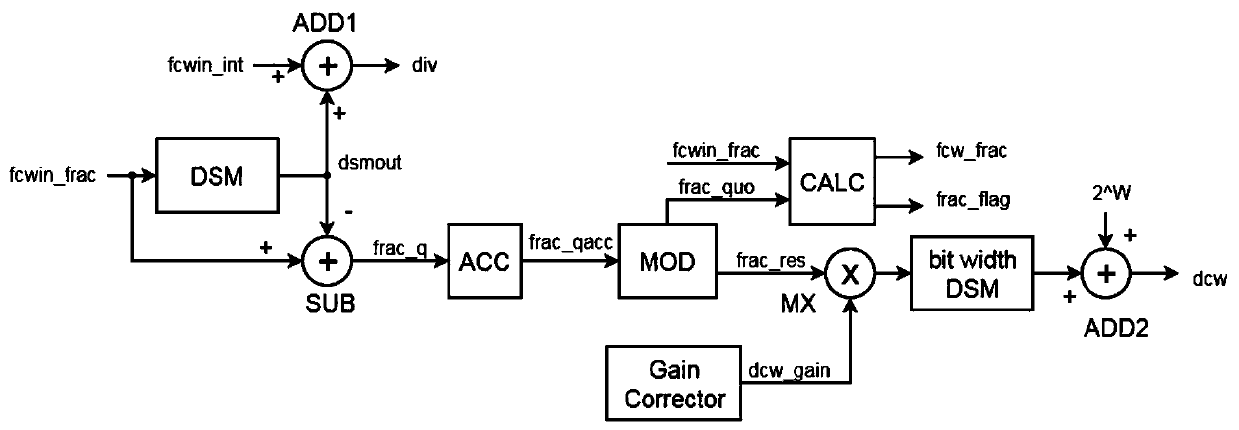

[0052] The fractional frequency contro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More