System on chip and FPGA kernel information processing method thereof

A system-on-chip and core technology, applied in electrical digital data processing, architecture with a single central processing unit, CAD circuit design, etc., can solve the problems of interconnection communication, reduced wiring efficiency, unbalanced wiring resources, etc., to improve wiring Efficiency, reduce chip power consumption, improve the effect of interconnect timing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

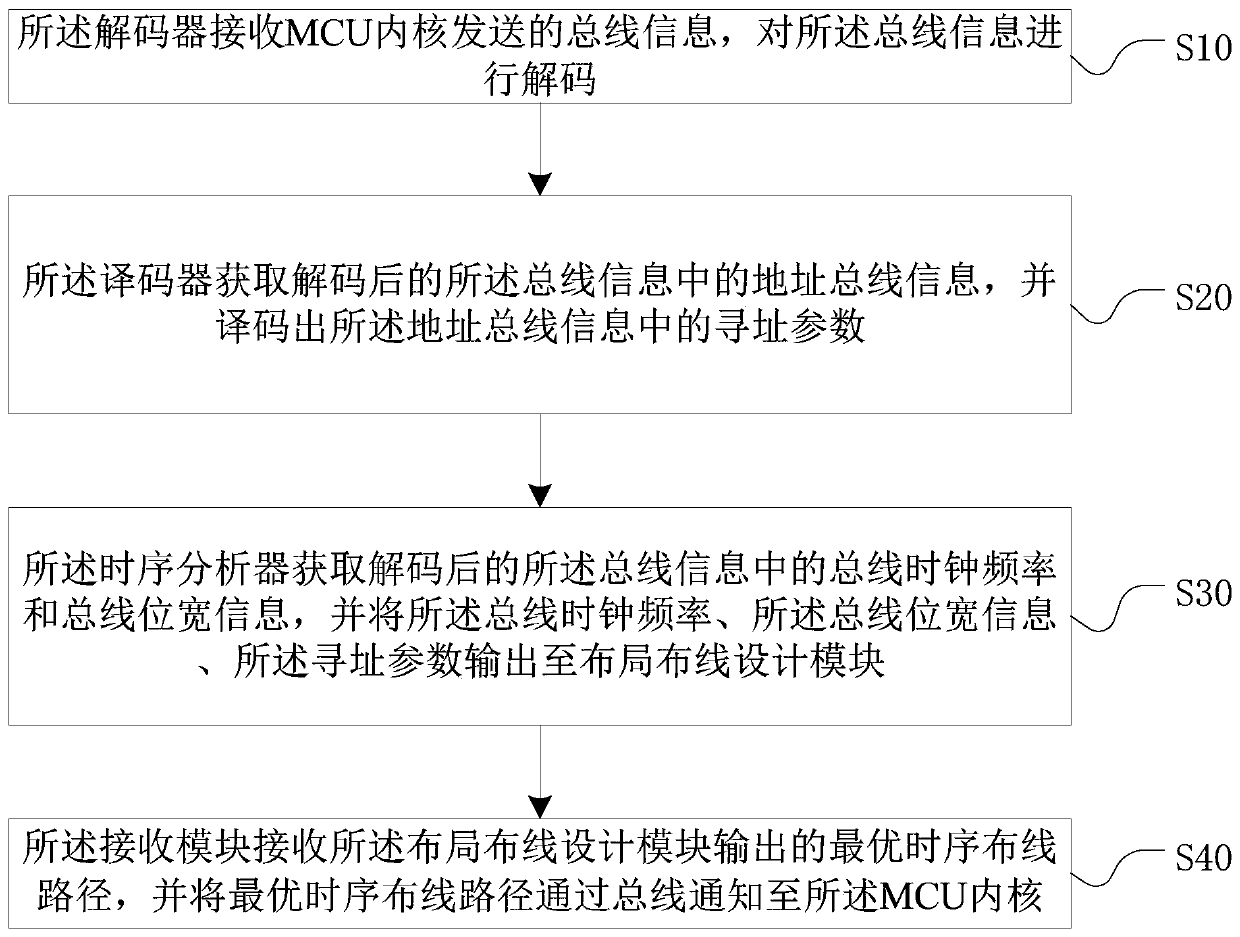

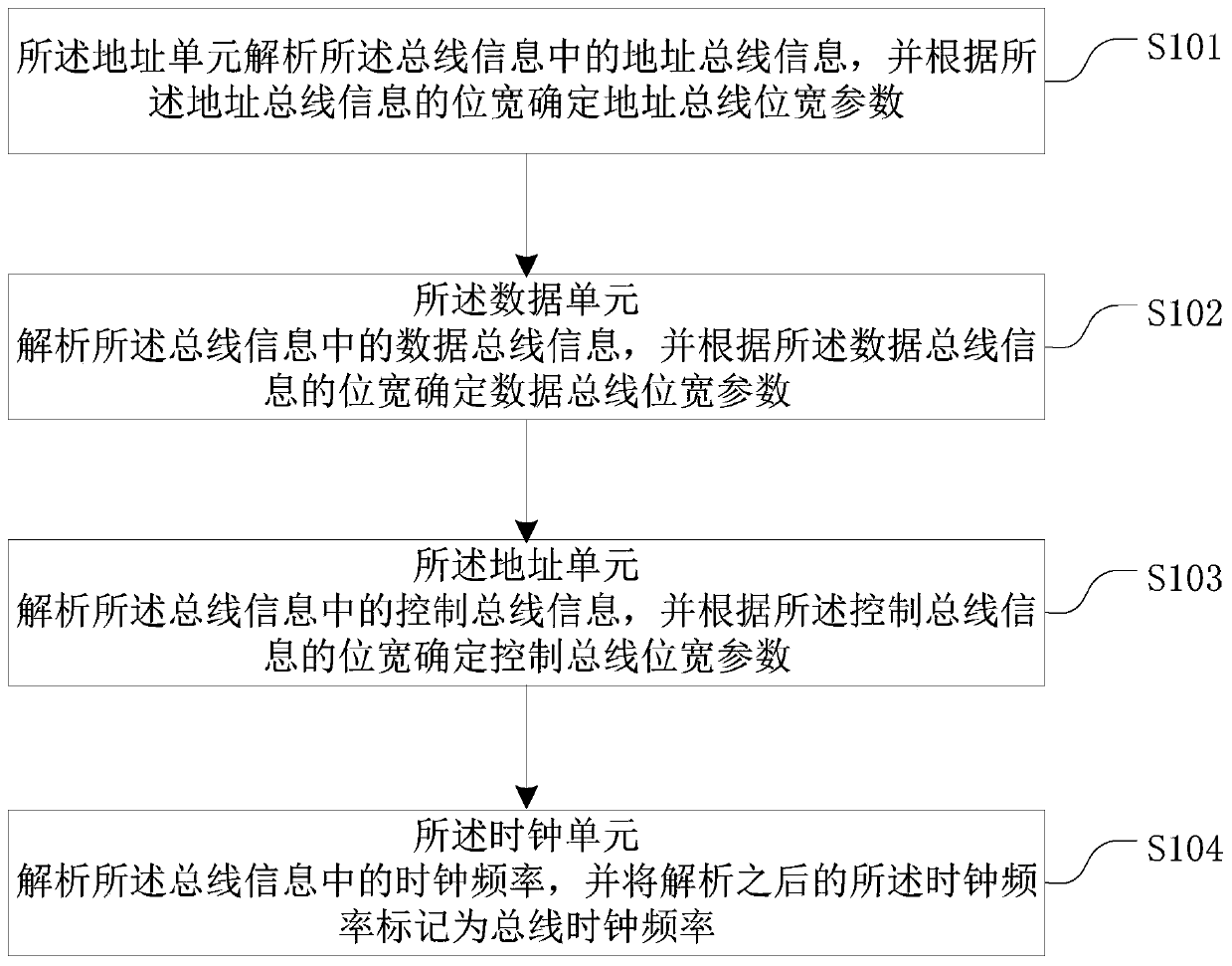

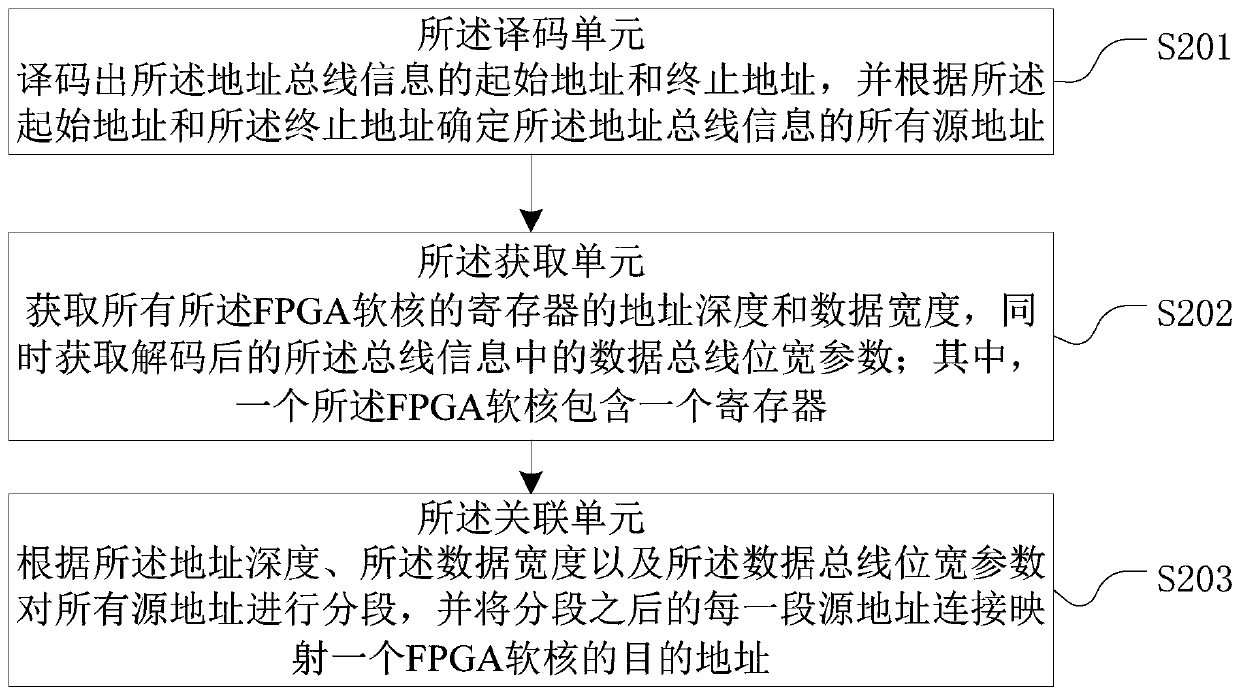

[0017] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0018] The present invention provides a system on chip 1, by automatically identifying the bus information of the MCU core 2 to output the optimal timing wiring path of the FPGA core 3 that matches the MCU core 2, and performing wiring according to the optimal timing wiring path, thereby improving the wiring efficiency. Therefore, the interconnection timing between the MCU core 2 and the FPGA core 3 is improved, the power consumption of the chip is redu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More