3D NAND manufacturing method and memory

A technology of 3D NAND and manufacturing method, which is applied in the direction of semiconductor devices, electric solid devices, electrical components, etc., can solve the problems such as structural instability cannot be guaranteed, and achieve the effect of more structure, enlarged opening area, and stable structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] As mentioned in the background technology section, in the prior art, as the number of layers of the O / N stack structure in the 3D NAND flash memory increases, the structural instability cannot be guaranteed during the manufacturing process.

[0039] The inventors have found that the reasons for the above phenomenon are as follows:

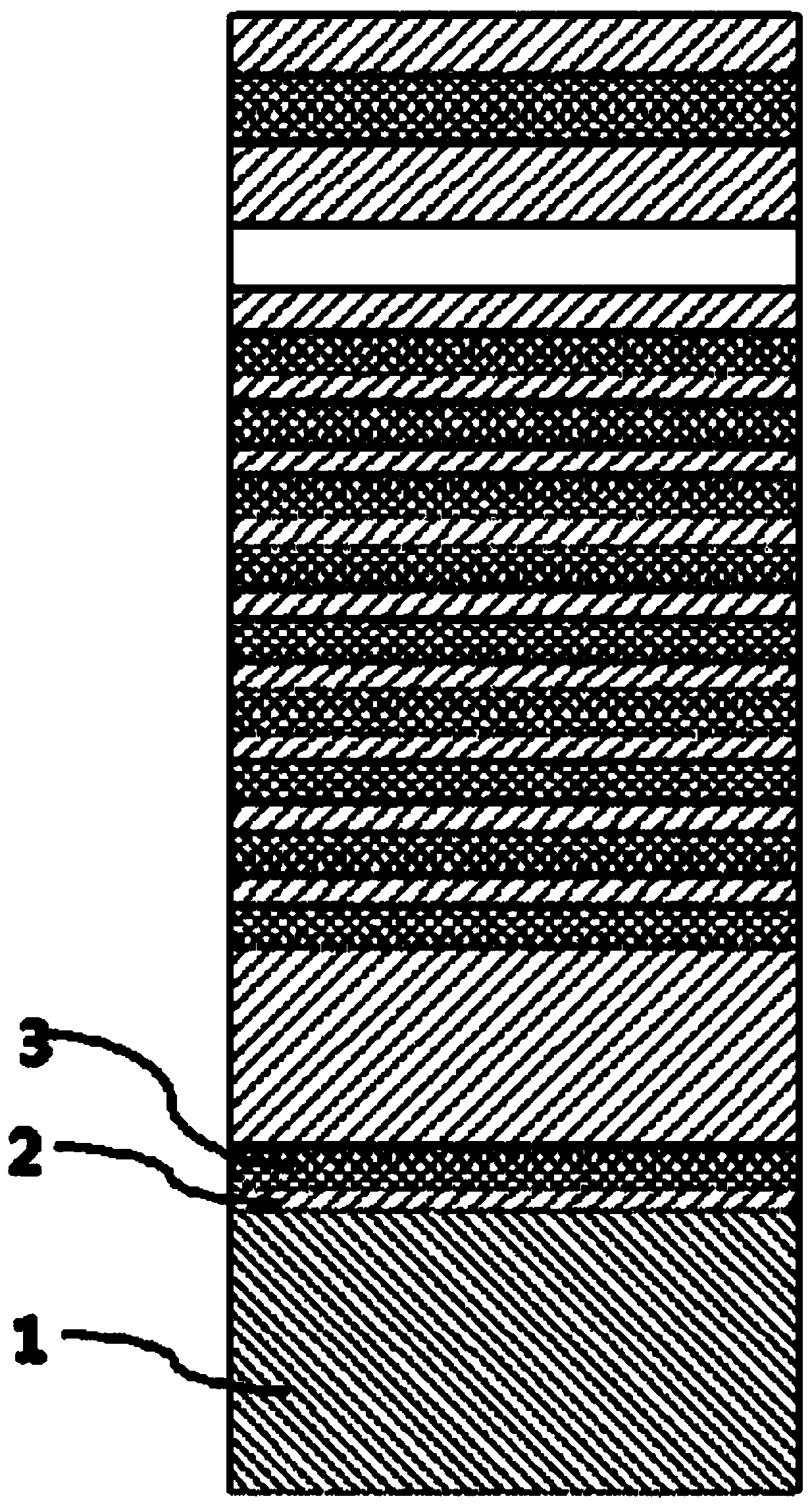

[0040] Please refer to Figure 1a-1m , the 3D NAND flash memory in the prior art adopts the following method:

[0041] S1: deposition substrate stack structure, see Figure 1a Specifically, a substrate 1 is provided, the surface of the substrate is formed with a multi-layer interlayer dielectric layer 2 and a sacrificial dielectric layer 3 interleaved, and the sacrificial dielectric layer 3 is formed between adjacent interlayer dielectric layers 2 ; The interlayer dielectric layer 2 is a silicon oxide layer, and the sacrificial dielectric layer 3 is a silicon nitride layer, thereby forming an O / N stack structure (O / N Stacks);

[0042] S2: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com