Layout method for three-dimensional FPGA chip

A three-dimensional chip and layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as improved layout quality, low process reusability, and high software engineering complexity, so as to speed up development progress, The effect of reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

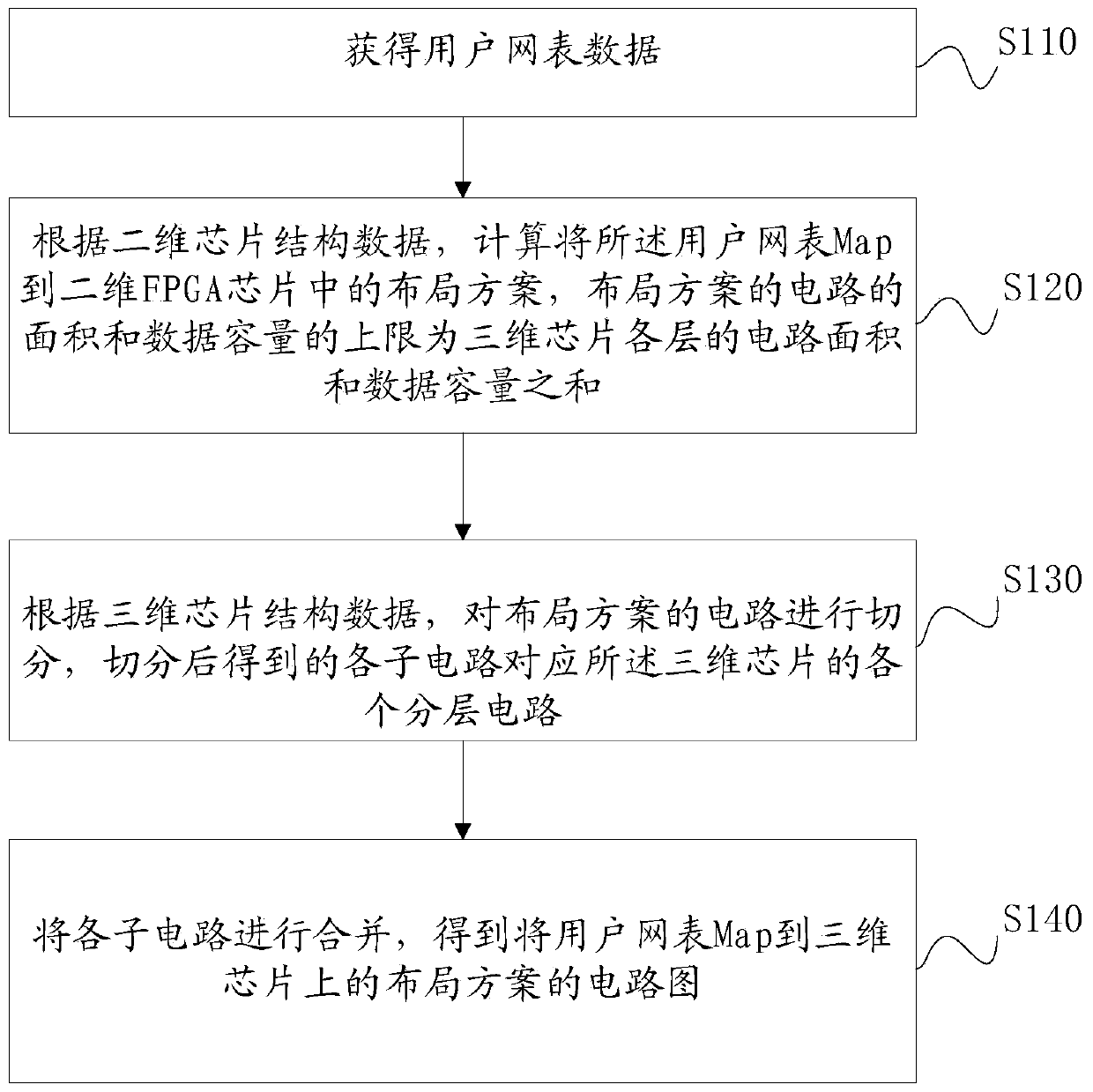

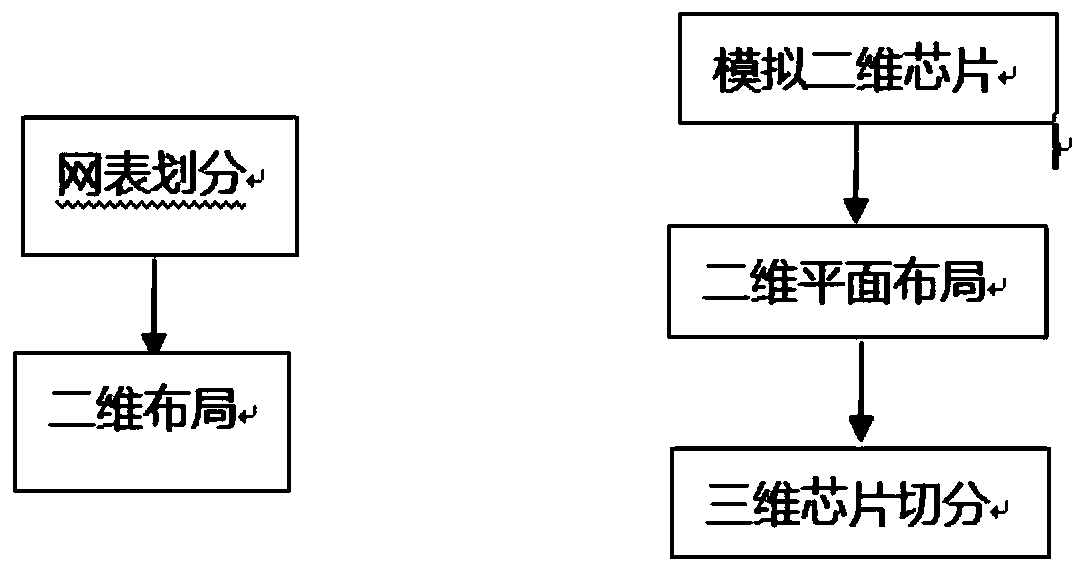

[0025] In the current three-dimensional chip layout, it is generally used to divide the user netlist first, and then carry out independent two-dimensional plane layout on the divided netlist. The present invention proposes a method for three-dimensional chip layout. Chip, carry out two-dimensional plane layout, after the layout result is generated, and then divide the chip, see figure 2 . This 3D chip layout method can better reuse the curr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More