OTP memory and manufacturing method thereof

A manufacturing method and memory technology, applied in read-only memory, static memory, semiconductor/solid-state device manufacturing, etc., can solve the problems of large storage unit area, unfavorable application of high density of kilobit level, etc., and improve the writing speed. , read the effect of simple and fast operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

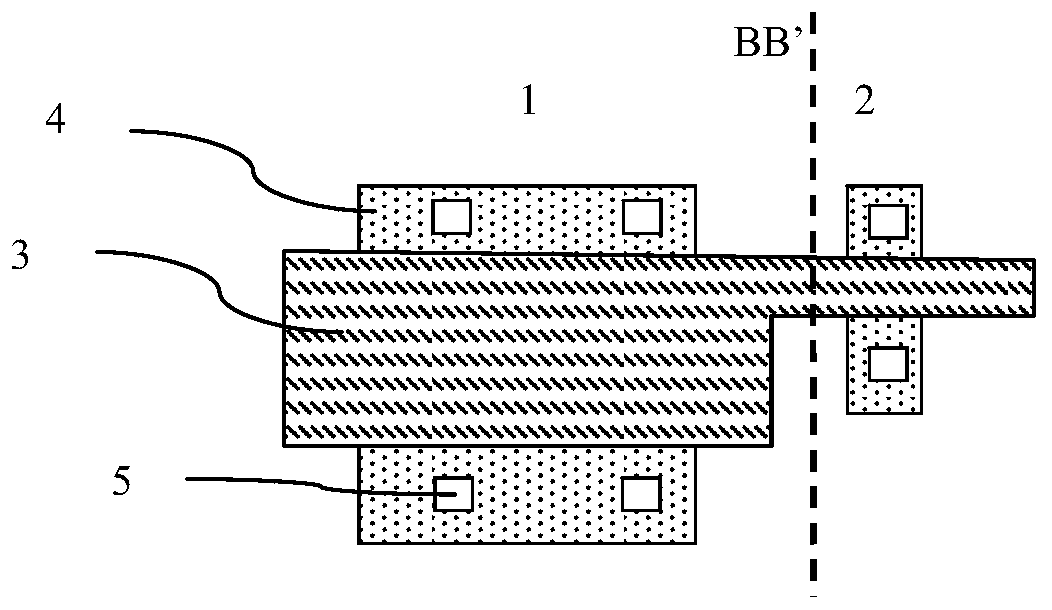

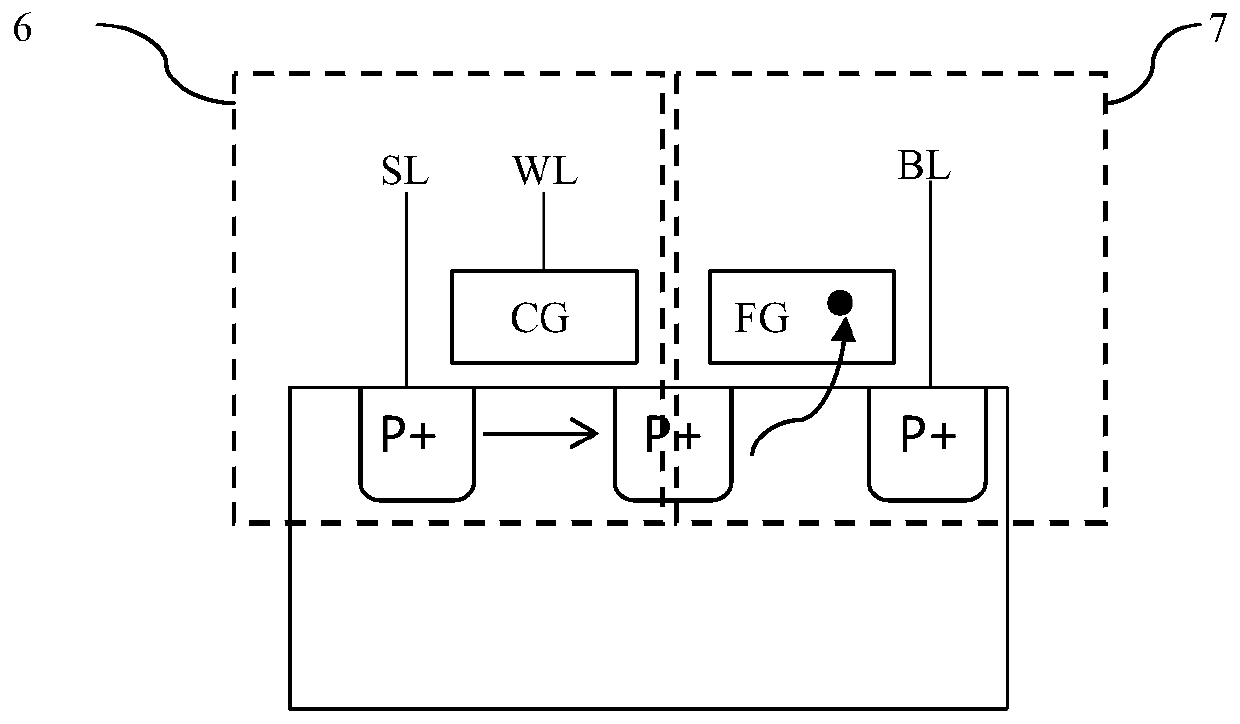

[0068] like Figure 4 Shown, is the layout of the OTP memory of the embodiment of the present invention; As Figure 5 As shown, it is the OTP memory edge of the embodiment of the present invention Figure 4 A cross-sectional view of line AA; the cell structure of the OTP memory according to the embodiment of the present invention includes: a first active region 201 and a second active region 202 .

[0069] The first active region 201 and the second active region 202 vertically intersect each other.

[0070] EDNMOS is formed in the first active region 201 , and PMOS is formed in the second active region 202 .

[0071] The EDNMOS includes a first source region 205, a first channel region 206, a drift region 207, a first drain region 209 and a first gate structure, and the first gate structure is composed of a first gate dielectric layer 214a and a first Polysilicon gates 203 are superimposed, the direction between the first source region 205 and the first drain region 209 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More