Efficient bit flipping decoder based on self-adaptive threshold value

An adaptive threshold and bit flipping technology, applied in the field of decoder design, can solve problems such as unsuitable application scenarios and increase overall complexity, and achieve the effects of reducing decoding delay, high throughput, and accurately matching the decoding process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

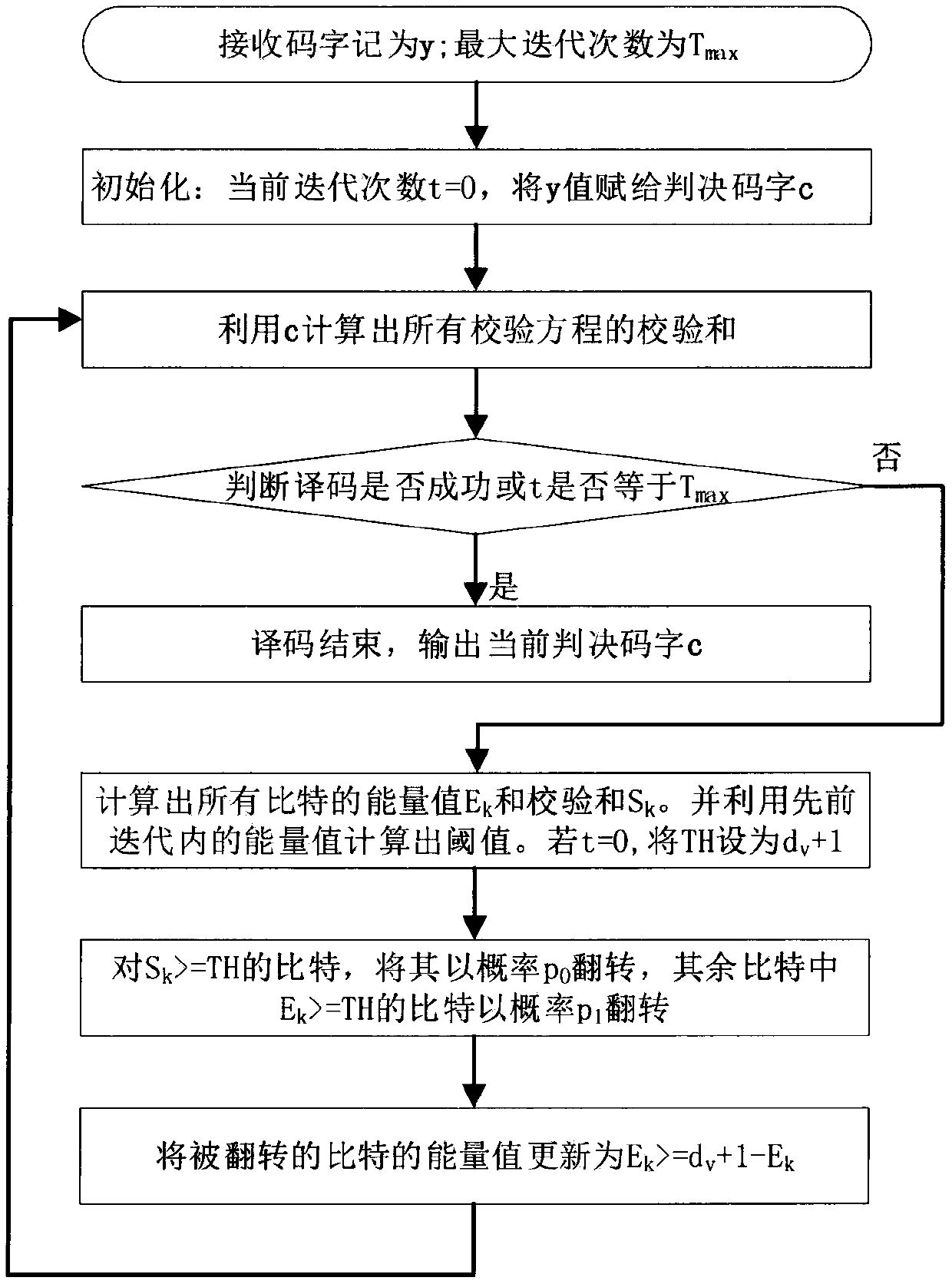

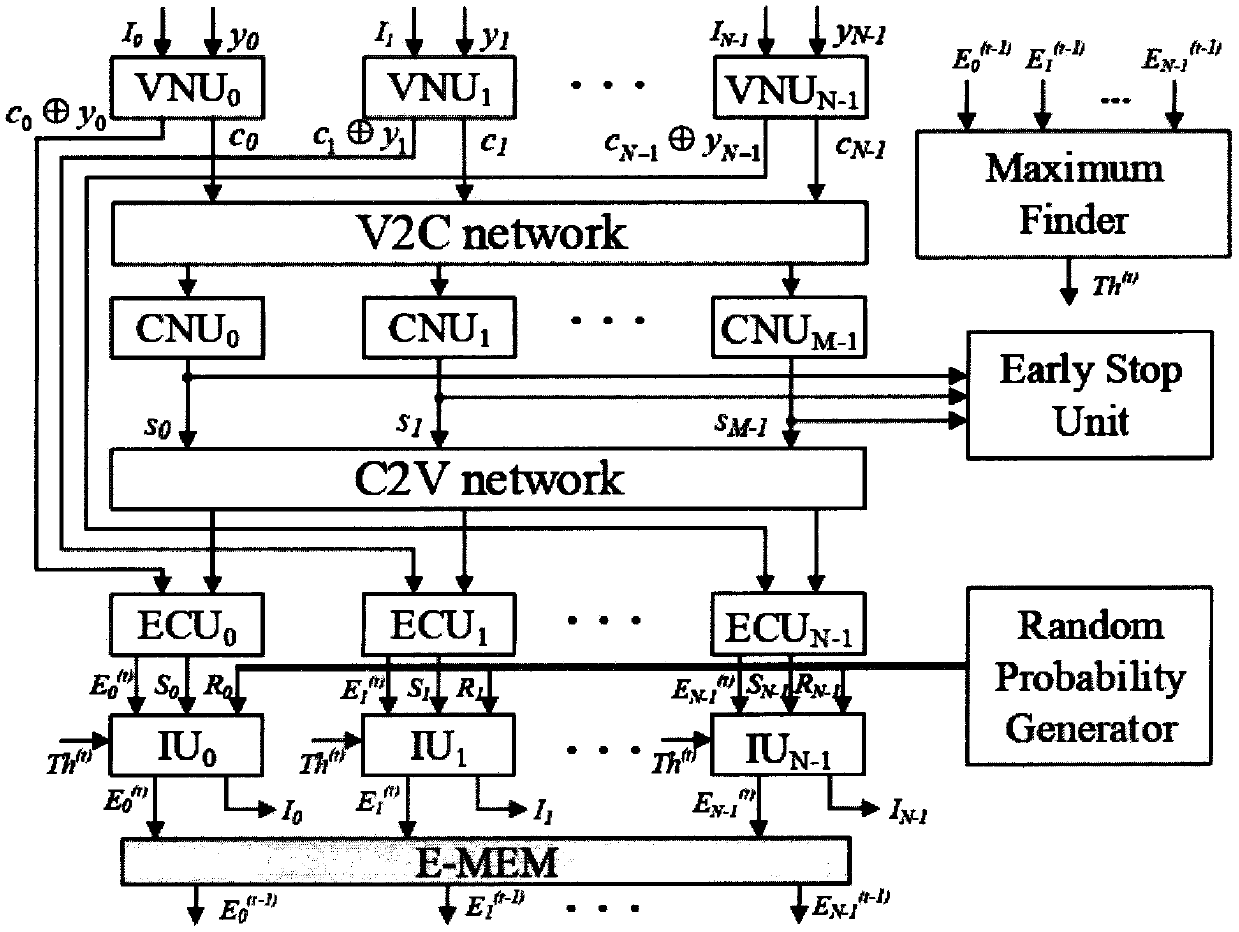

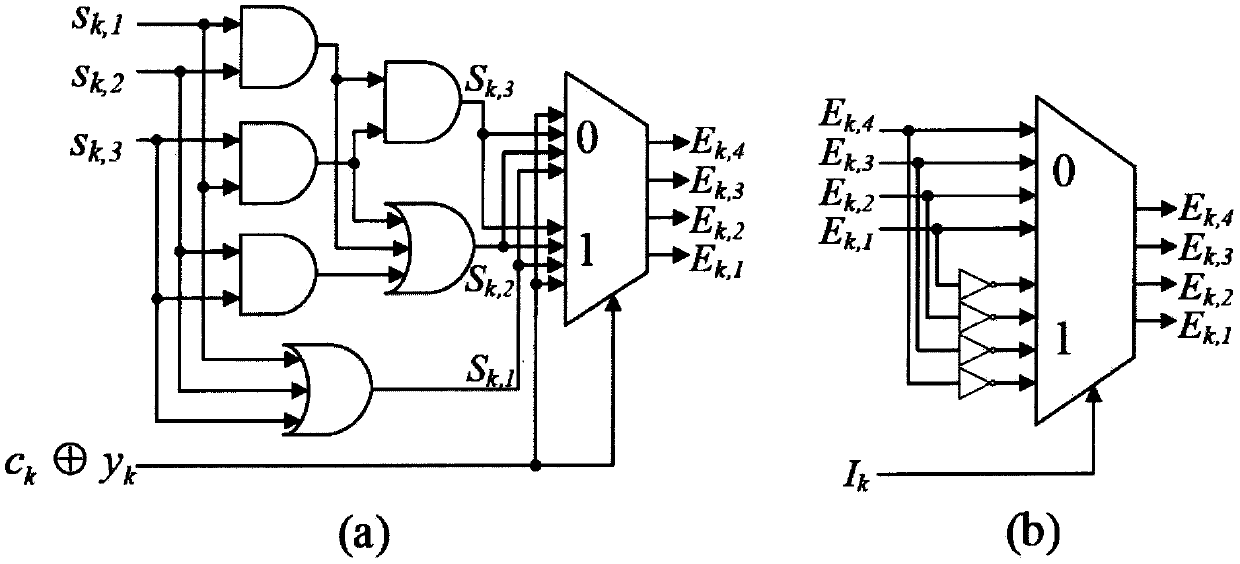

Method used

Image

Examples

Embodiment

[0028] Embodiment: Take the codeword whose code length is 1296, code rate is 1 / 2, column weight is 3, and row weight is 6 as an example. Figure 4 It is a schematic diagram of the performance simulation of the decoder of the present invention. The maximum number of iterations for all BF algorithms is set to 300, and the maximum number of iterations for the OMS algorithm is set to 20. It can be seen that compared with the current optimal TRGDBF algorithm, the SABF disclosed in the present invention can improve the performance by an order of magnitude while having a shorter critical path. When the maximum number of iterations is increased to 1000, the performance of SABF can be further improved by an order of magnitude, and the decoding performance of OMS algorithm can be achieved. In addition, the proposed SABF decoder architecture is described in Verilog language, and the obtained RTL is synthesized with Synopsys tools. The technology used is TSMC 90nm CMOS technology. Figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More