Integrated circuit ESD protection circuit

An ESD protection, integrated circuit technology, applied in the field of ESD protection design, can solve the problems of low turn-on voltage, easy breakdown and failure of gate oxide layer, large area, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

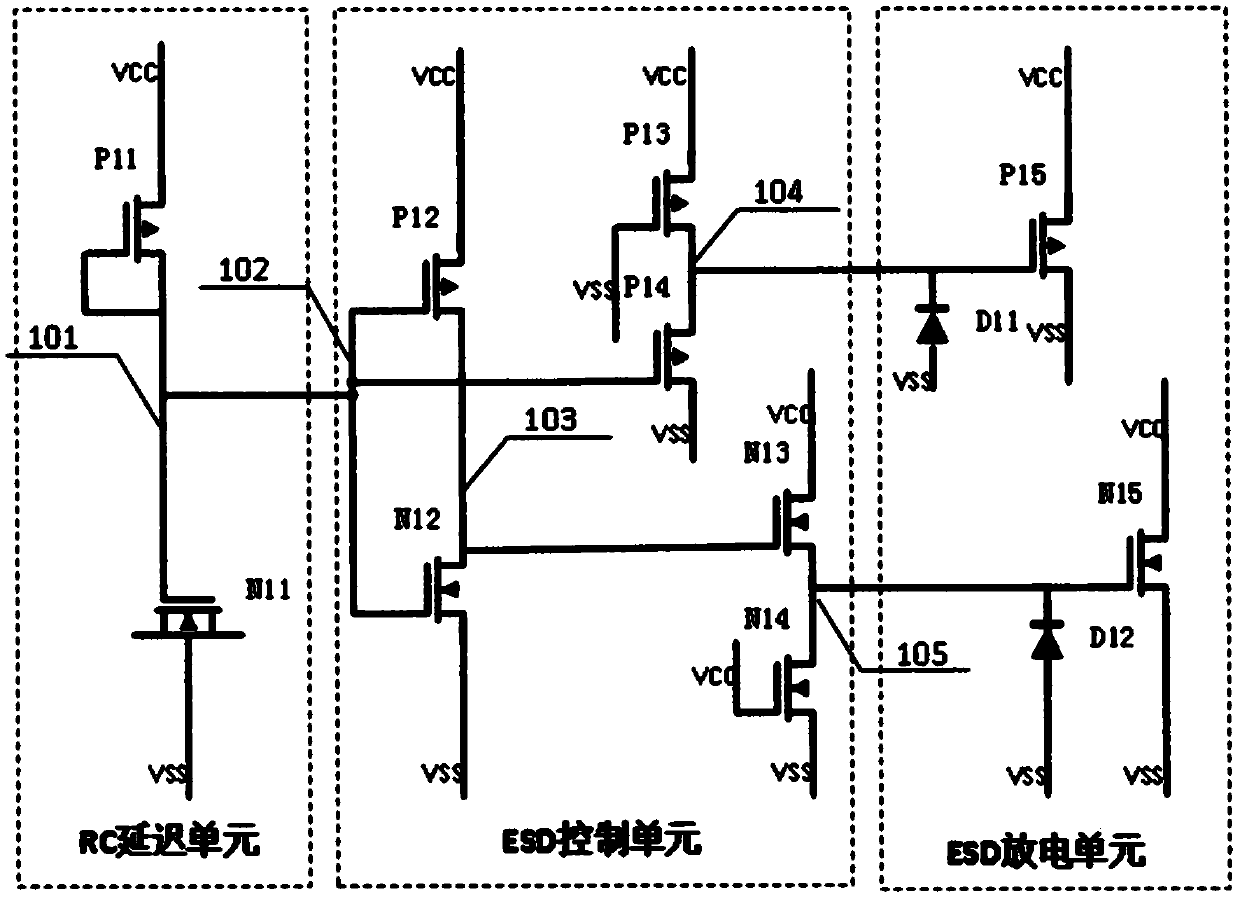

[0027] Specific embodiments of the present invention are as attached figure 1 shown.

[0028] It mainly includes three parts, which are RC delay unit, ESD control unit and ESD discharge unit.

[0029] The RC delay unit is composed of an equivalent capacitance N11 composed of NMOS and an equivalent resistance P11 composed of PMOS, wherein the source and substrate of the equivalent resistance P11 are connected to the power supply VCC, and the gate and drain are connected to the output point 101 , so the P11 device is in the normally open state of the channel, forming a PMOS channel resistance. The resistance formed by this method has a smaller area than the resistance formed by polysilicon, which can save layout area and reduce chip cost. The source, drain and substrate of the equivalent capacitor N11 are all connected to the ground VSS, and the gate is connected to the output point 101, so the equivalent capacitor is formed by the gate oxide layer of the NMOS N11. The RC st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More