High-cardinal-number approximate Booth encoding method and mixed-cardinal-number Booth encoding approximate multiplier

A technology of mixed radix and encoding method, applied in the direction of electrical digital data processing, digital data processing components, instruments, etc., can solve the problems of unfavorable product compression module design, complex coding circuit circuit, and large number of partial products, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

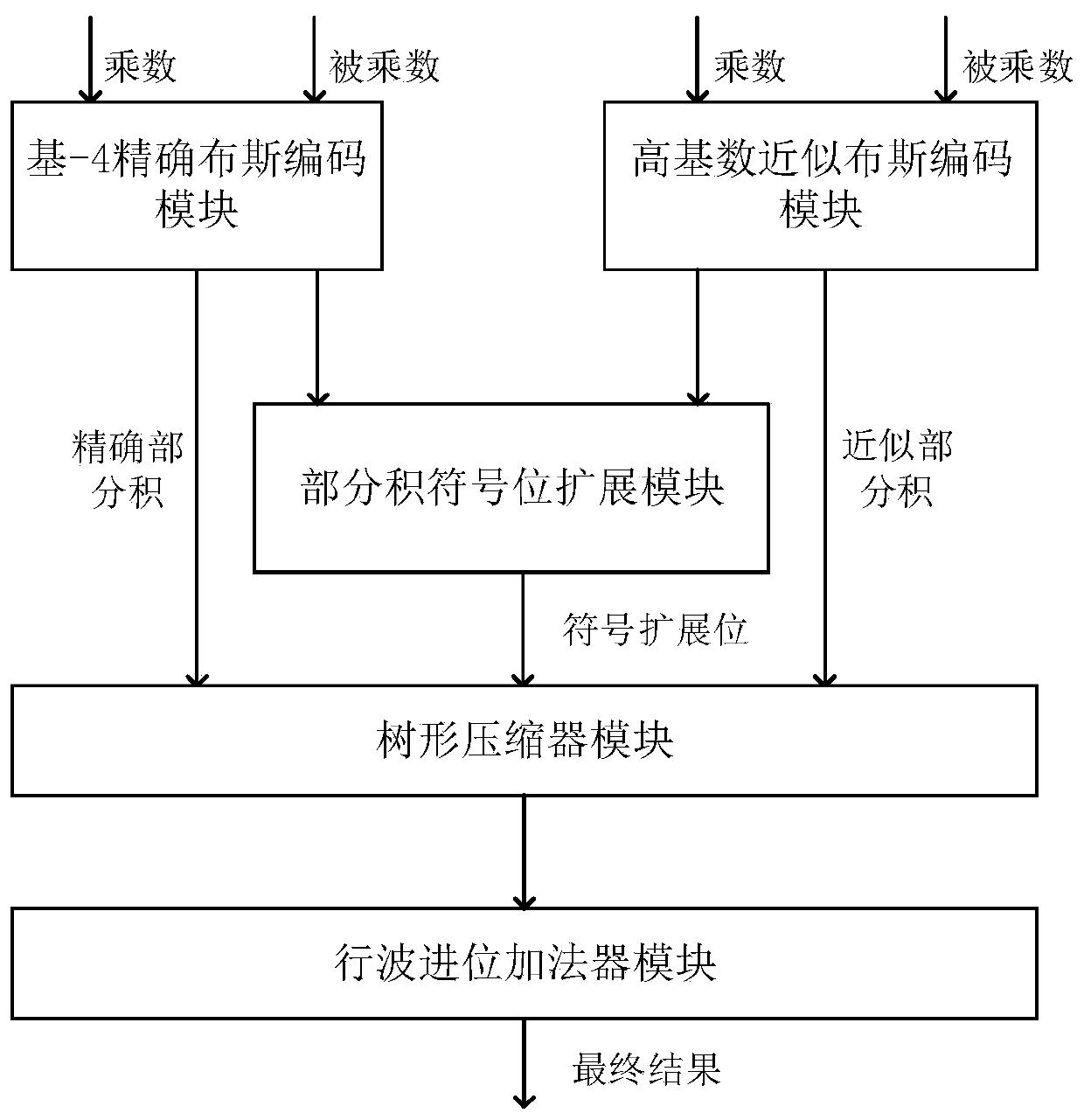

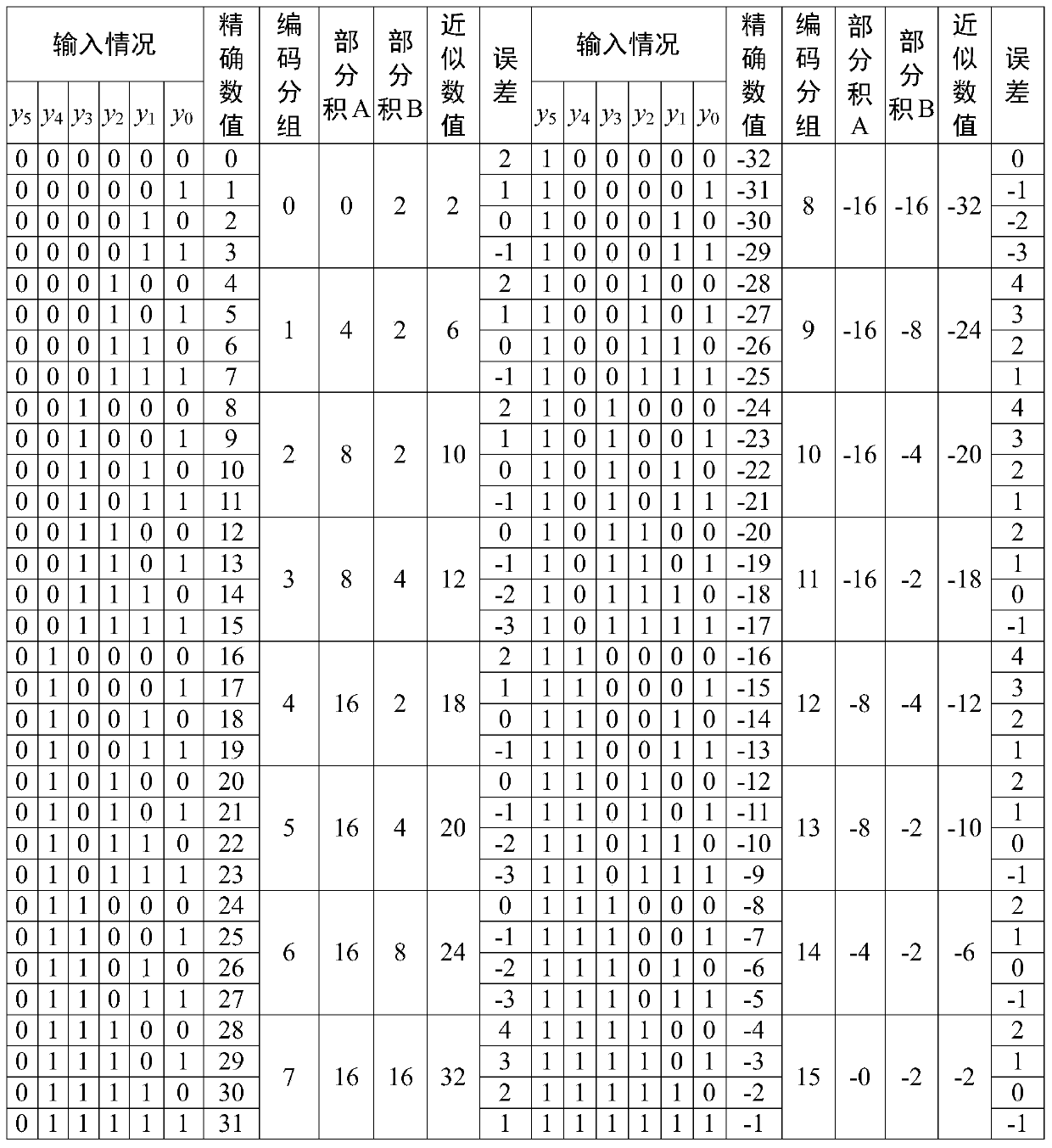

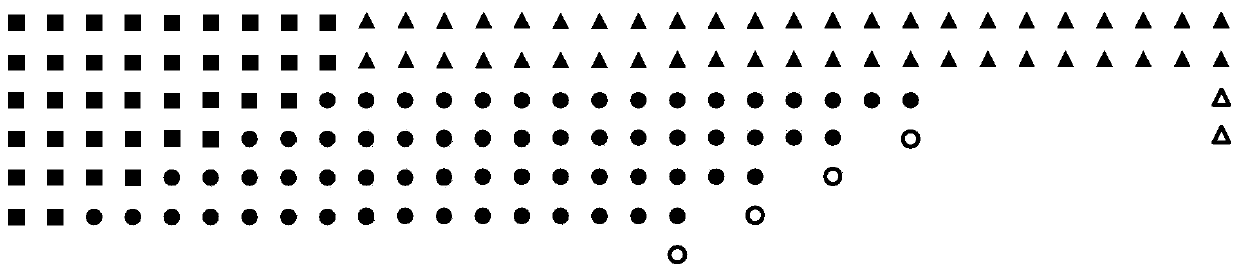

[0056] The invention proposes a novel high-radix approximation Booth encoding method, which can significantly reduce the hardware complexity of the encoding circuit and the partial product compression circuit. For an n-bit multiplier and an n-bit multiplicand, the high-radix approximate Booth encoding method proposed by the present invention encodes m bits with lower weights in the multiplicand, and combines the n-bit multiplier to obtain a partial product. In multiplication and addition operations, the closer the data is to the most significant bit, the greater the impact on the final result. Therefore, although the number of digits required by Booth codes of three kinds of high bases of base-64, base-256, and base-1024 in the low significant digit part are respectively 6, 8, and 10 bits, the present invention only takes the upper 4 bits there...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More