Trench type SiC IGBT structure and preparation method thereof

A trench type and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as poor electrical conductivity and performance, and achieve the effects of improving lifespan, improving conduction performance, and increasing surface area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

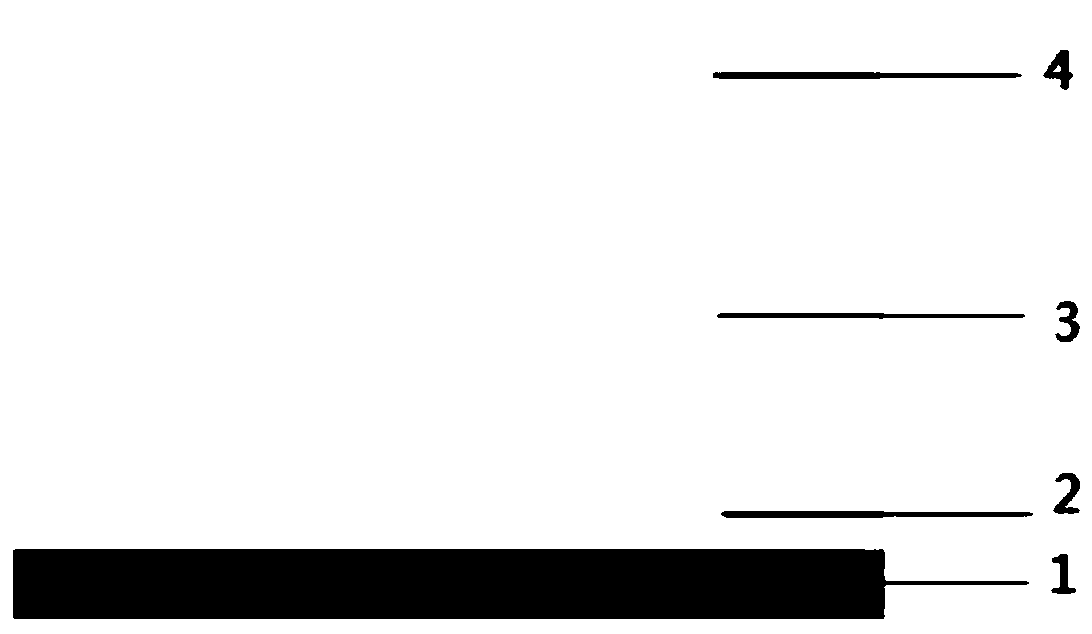

[0055] A structure of a trench silicon carbide IGBT, comprising:

[0056] N+ type SiC substrate 1;

[0057] A P-type SiC drift layer 3 disposed on the upper part of the N+ type SiC substrate 1, and a P-type SiC buffer layer 2 is provided between the N-type substrate 1 and the P-type SiC drift layer 3;

[0058] An N-type doped region 4 disposed on the upper surface of the P-type SiC drift layer 3;

[0059]A P-type doped region 5 disposed on a local upper surface of the N-type doped region 4;

[0060] A trench 6 disposed on the upper surface of the P-type SiC drift layer 3 and penetrating the N-type doped region 4, and the depth of the trench 6 is greater than the depth of the N-type doped region 4;

[0061] The inner wall of the trench 6 is provided with a second oxide layer 11, and the upper part of the trench is provided with a first oxide layer 8;

[0062] A gate 7 covered by the first oxide layer 8 and the second oxide layer 11 is arranged in the trench 6, and the upper ...

Embodiment 2

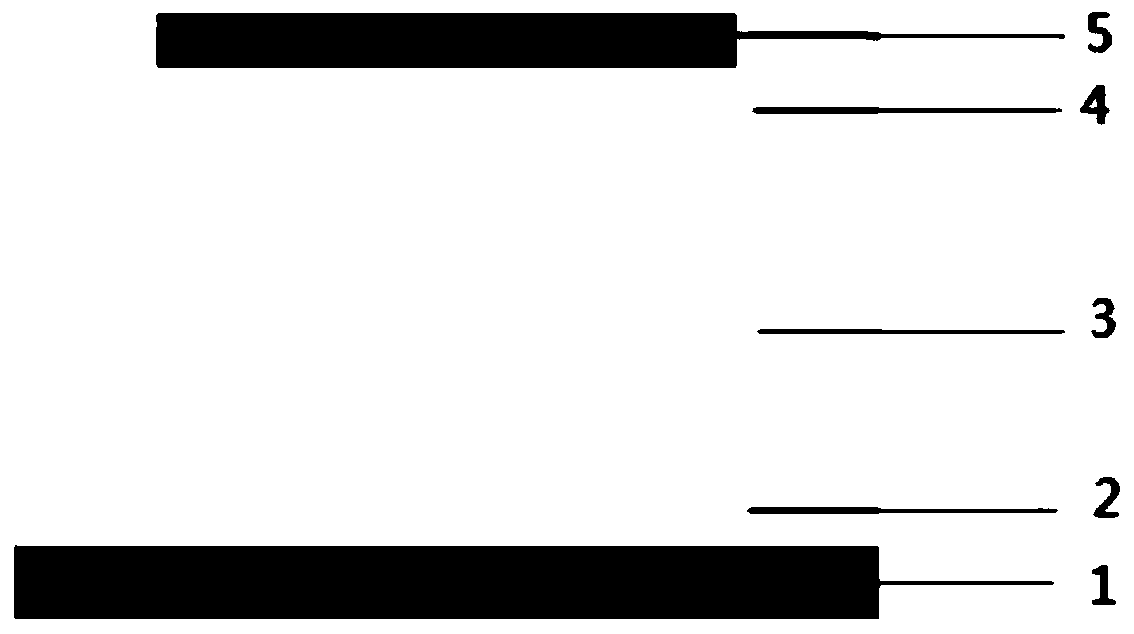

[0080] A structure of a trench silicon carbide IGBT, comprising:

[0081] N+ type SiC substrate 1;

[0082] A P-type SiC drift layer 3 disposed on the upper part of the N+ type SiC substrate 1, and a P-type SiC buffer layer 2 is provided between the N+ type SiC substrate 1 and the P-type SiC drift layer 3;

[0083] An N-type doped region 4 disposed on the upper surface of the P-type drift layer 3;

[0084] The P-type doped region 5 arranged on the upper part of the N-type doped region 4; the trench 6 arranged on the upper surface of the P-type SiC drift layer 3 and running through the N-type doped region 4, and the depth of the trench 6 is greater than that of the N-type doped region. The depth of the miscellaneous area 4;

[0085] The inner wall of the trench 6 is provided with a second oxide layer 11, and the upper part of the trench is provided with a first oxide layer 8;

[0086] A gate 7 covered by the first oxide layer 8 and the second oxide layer 11 is arranged in th...

Embodiment 3

[0105] A structure of a trench silicon carbide IGBT, comprising:

[0106] P+ type SiC substrate 1;

[0107] An N-type SiC drift layer 3 disposed on the top of the P+ type SiC substrate 1, and an N-type SiC buffer layer 2 is arranged between the P-type substrate 1 and the N-type SiC drift layer 3;

[0108] A P-type doped region 4 disposed on the upper surface of the N-type SiC drift layer 3;

[0109] An N-type doped region 5 disposed on a partial upper surface of the P-type doped region 4;

[0110] A trench 6 disposed on the upper surface of the N-type SiC drift layer 3 and penetrating the P-type doped region 4, and the depth of the trench 6 is greater than the depth of the P-type doped region 4;

[0111] The inner wall of the trench 6 is provided with a second oxide layer 11, and the upper part of the trench is provided with a first oxide layer 8;

[0112] A gate 7 covered by the first oxide layer 8 and the second oxide layer 11 is arranged in the trench 6, and the upper su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com