Wafer-level chip structure, multi-chip stacking interconnection structure and preparation method

A wafer-level chip and chip structure technology, used in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

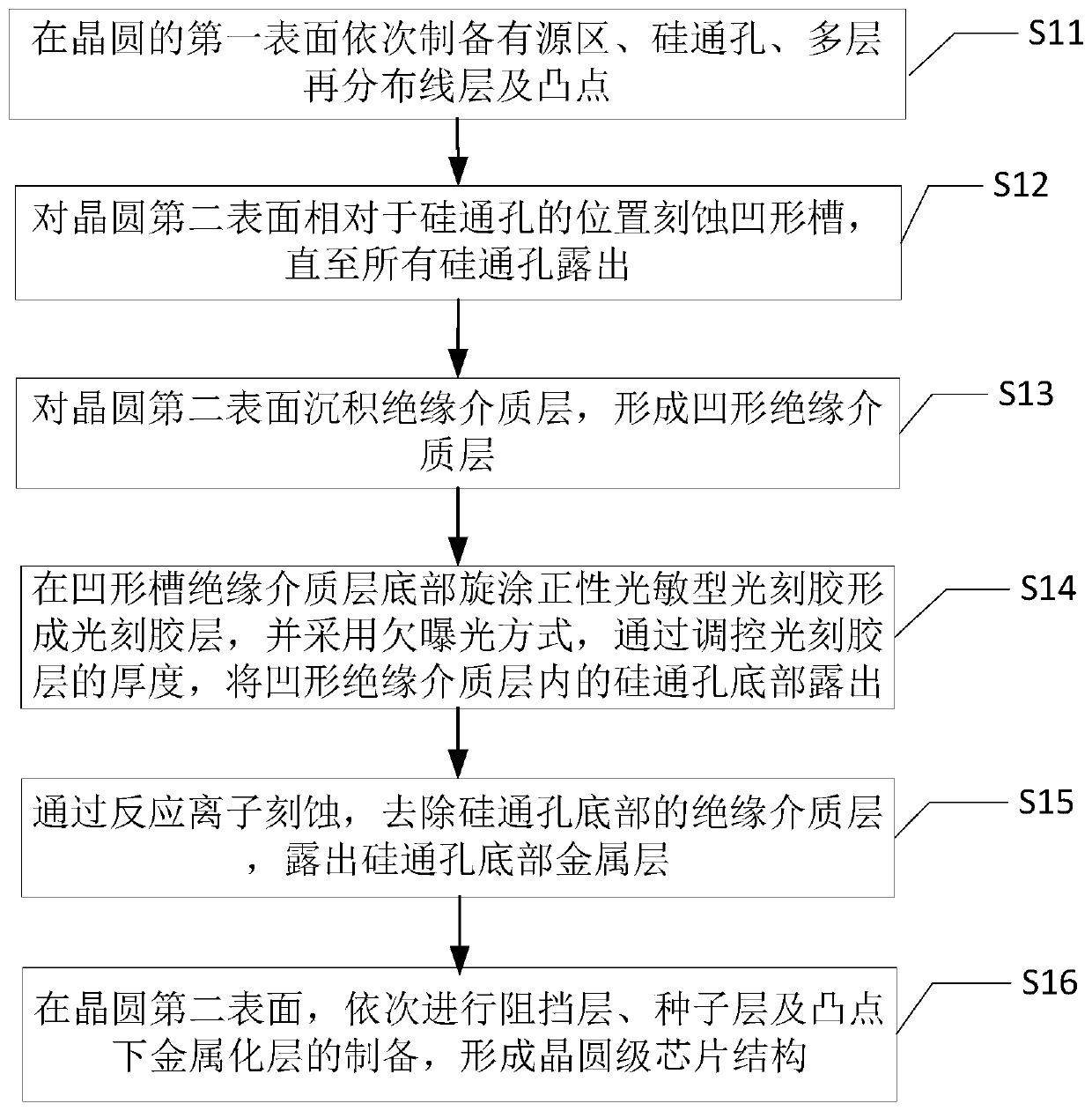

Embodiment 1

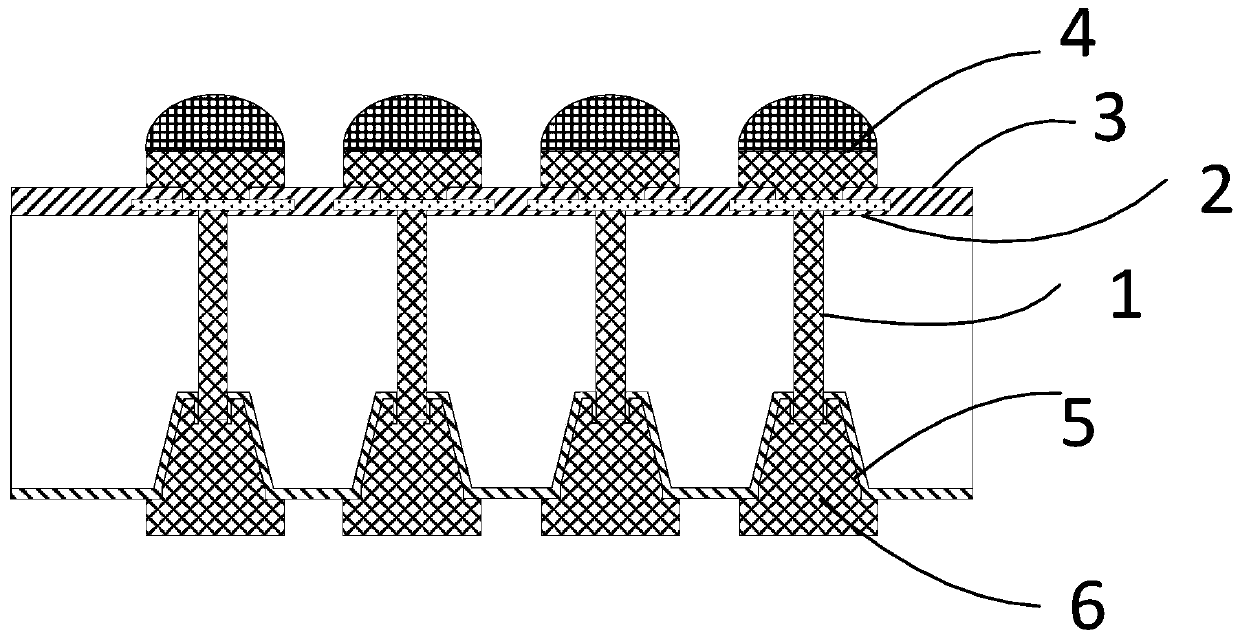

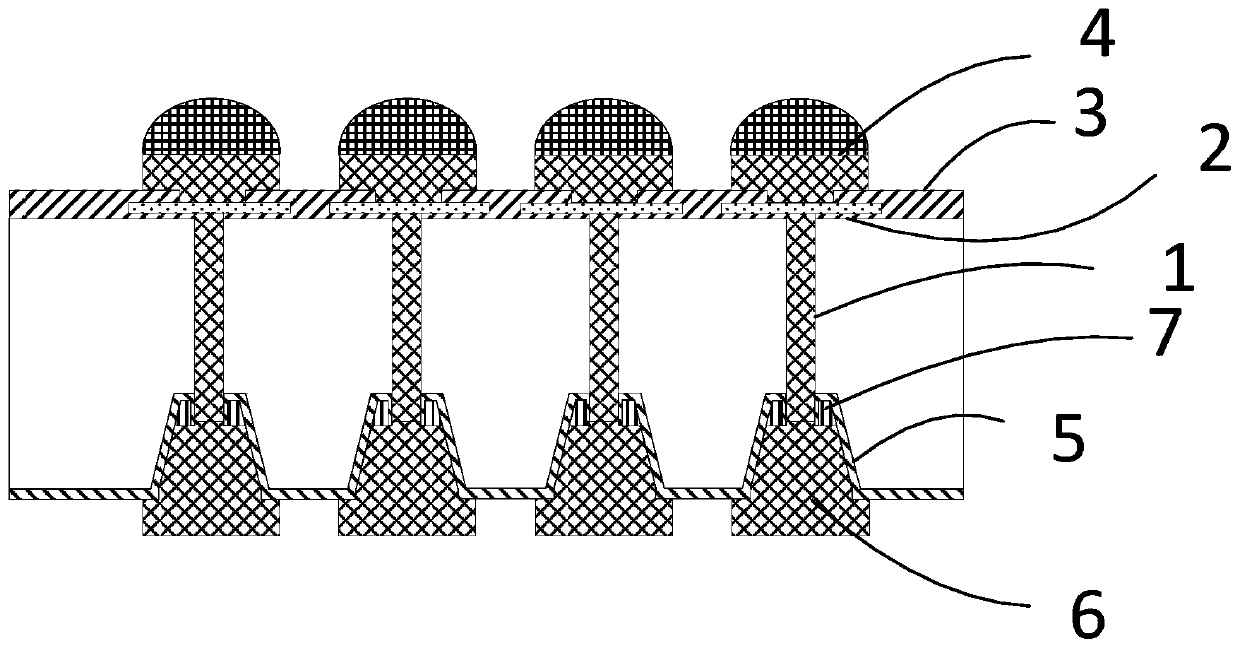

[0050] Embodiments of the present invention provide a wafer-level chip structure, such as figure 1 As shown, it includes: through-silicon via 1, and the through-silicon via is located at a preset distance from the first surface of the wafer to the second surface; the first surface of the wafer includes: an active region 2, a multi-layer Redistribution line layer 3 and bump 4; the second surface of the wafer includes: UBM layer 5 and concave insulating dielectric layer 6, the number of concave structures of the concave insulating dielectric layer 6 is the same as that of the silicon The number of through holes 1 is the same, and the bottom of the concave insulating dielectric layer is blocked by the bottom of the through-silicon hole, and the under-bump metallization layer fills the concave insulating dielectric layer and is electrically connected to the through-silicon hole. . In the embodiment of the present invention, the material filled in the TSV 1 can be copper, the bump...

Embodiment 2

[0061] An embodiment of the present invention provides a wafer-level multi-chip stacking interconnection structure, such as Figure 9 As shown, it includes: a chip bonder 8, a substrate 9 and a lead terminal 10, the chip bonder 7 is transferred to the first surface of the substrate 8, and the lead terminal 9 is formed on the second surface of the substrate, wherein,

[0062] The chip bonding body 7 includes a plurality of single wafer-level chips arranged in a stack, and the multiple single wafer-level chips are directly connected through a bonding layer. The single wafer-level chips include: a first chip structure 11, And at least one second chip structure 12, the at least one second chip structure is located at the near end of the substrate, and the first chip structure is located at the far end of the substrate; the second chip structure is described in Embodiment 1 The wafer-level chip structure, such as Figure 9 It is shown that four second chip structures 12 are includ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More