Clock phase alignment method and circuit for high-speed serial transceiver

A high-speed serial, clock phase technology, applied in electrical components, pulse processing, pulse technology, etc., can solve the problems of complex implementation and occupy a lot of resources, and achieve the effect of less resource consumption, simple structure and high alignment accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that these embodiments are only used to illustrate the present invention and are not intended to limit the scope of the present invention. After reading the present invention, those skilled in the art Modifications to various equivalent forms of the present invention fall within the scope defined by the appended claims of the present invention.

[0042] Unless otherwise defined, all technical and scientific terms used herein have the same meaning as commonly understood by one of ordinary skill in the technical field of the invention. The terminology used herein in the description of the present invention is only for the purpose of describing specific embodiments, and is not intended to limit the present invention.

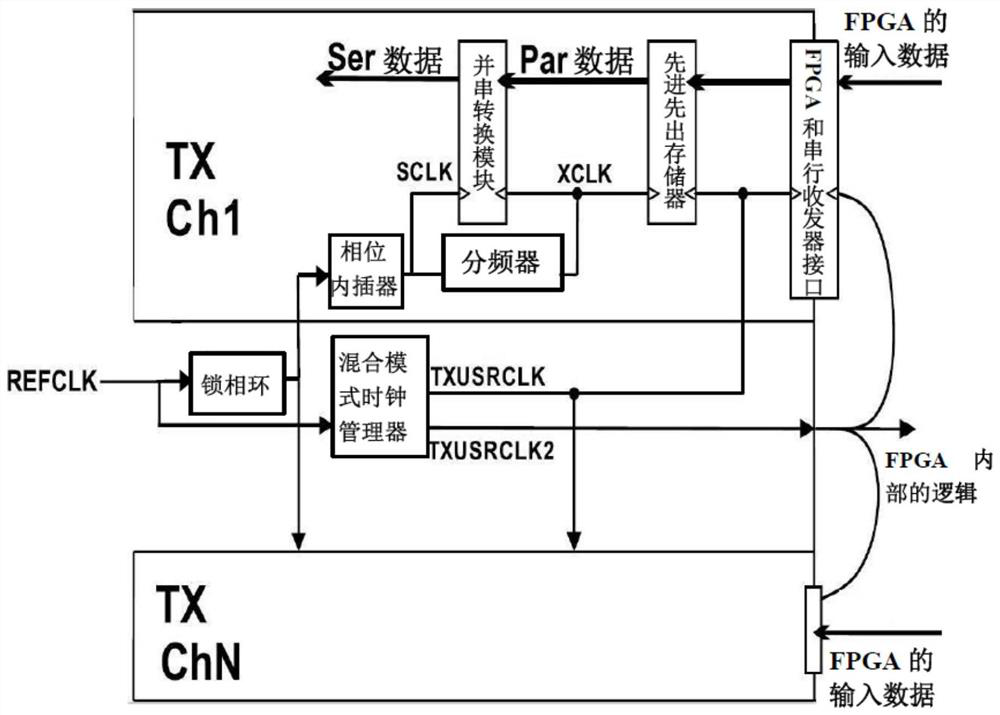

[0043] refer to figure 2 Shown is a clock phase alignment method for high-spee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More