Stacking structure and method for chips with central bonding points

A stacking structure and bonding point technology, which is applied in the direction of electrical components, transistors, and electric solid-state devices, can solve the problems that silicon wafers cannot be stacked high and stacked, and achieve the effect of rich chip selection and reduced module volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

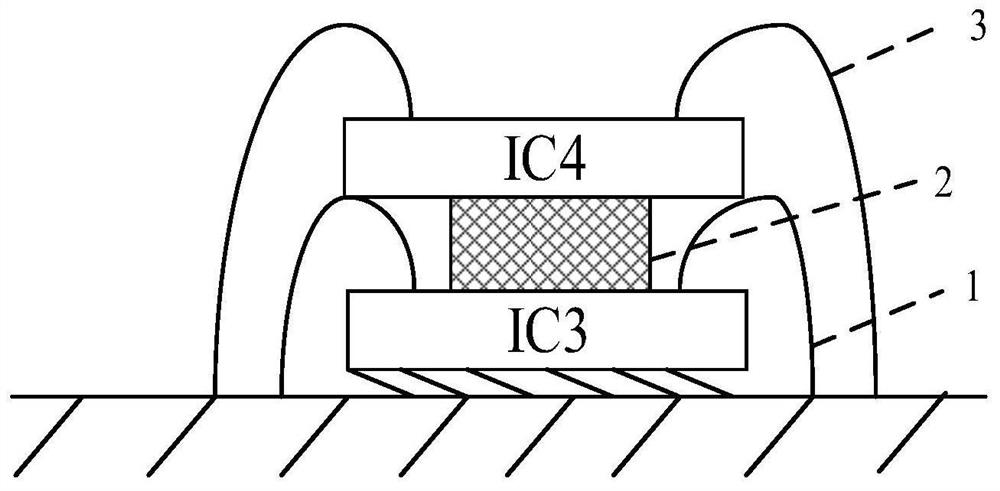

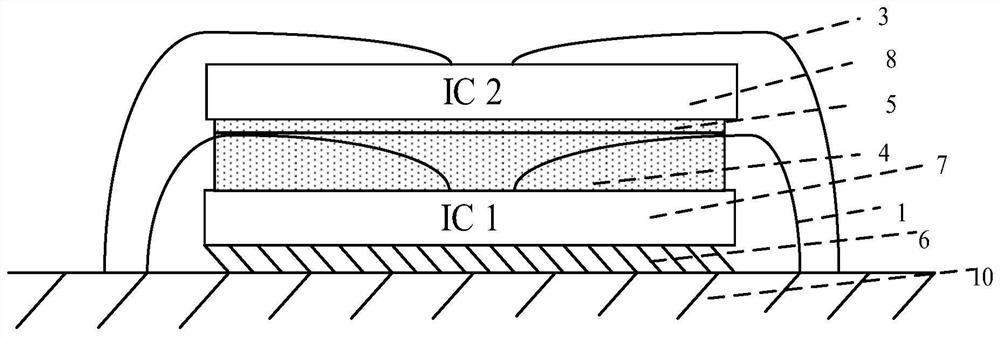

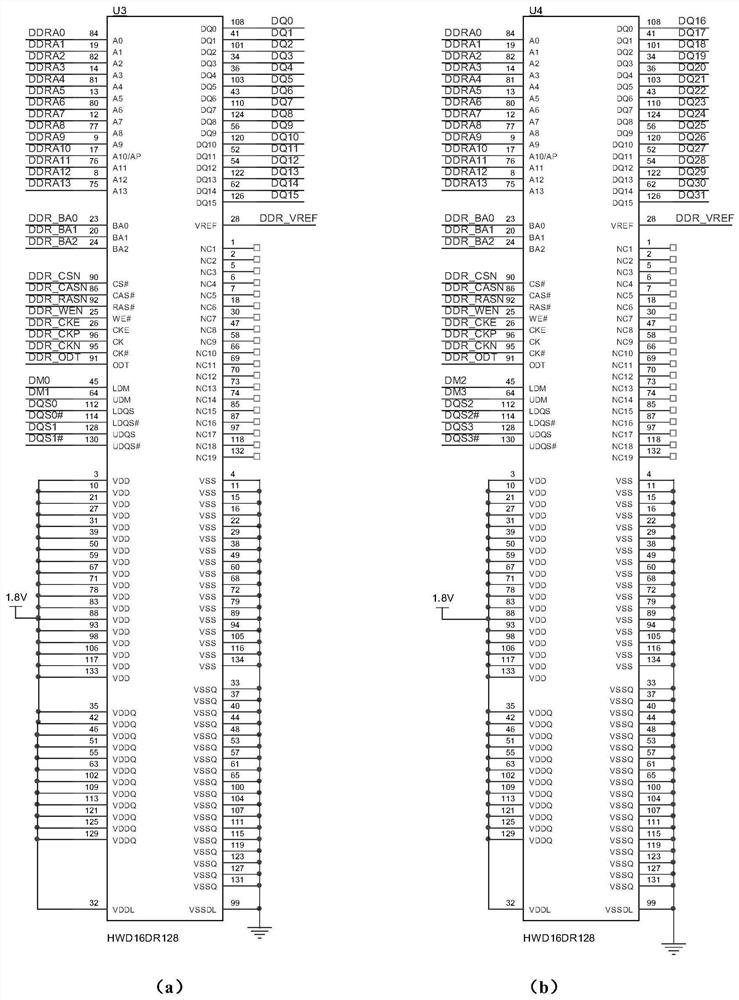

[0037] The present invention is described in further detail below in conjunction with accompanying drawing:

[0038] In the description of the present invention, it should be noted that the terms "center", "upper", "lower", "left", "right", "vertical", "horizontal", "inner", "outer" etc. The indicated orientation or positional relationship is based on the orientation or positional relationship shown in the drawings, and is only for the convenience of describing the present invention and simplifying the description, rather than indicating or implying that the referred device or element must have a specific orientation, or in a specific orientation. construction and operation, and therefore cannot be construed as limiting the present invention; the terms "first", "second", and "third" are used for descriptive purposes only, and cannot be construed as indicating or implying relative importance; in addition, unless otherwise Clearly stipulated and limited, the terms "installation"...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More