Shared cache method, baseband processing unit and chip thereof

A shared cache and cache unit technology, applied in the direction of electrical digital data processing, architecture with a single central processing unit, general-purpose stored program computer, etc., can solve the problems of increased chip design area and power consumption, and low efficiency of sampling point cache utilization , to reduce cache power consumption, facilitate miniaturization design, and improve utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

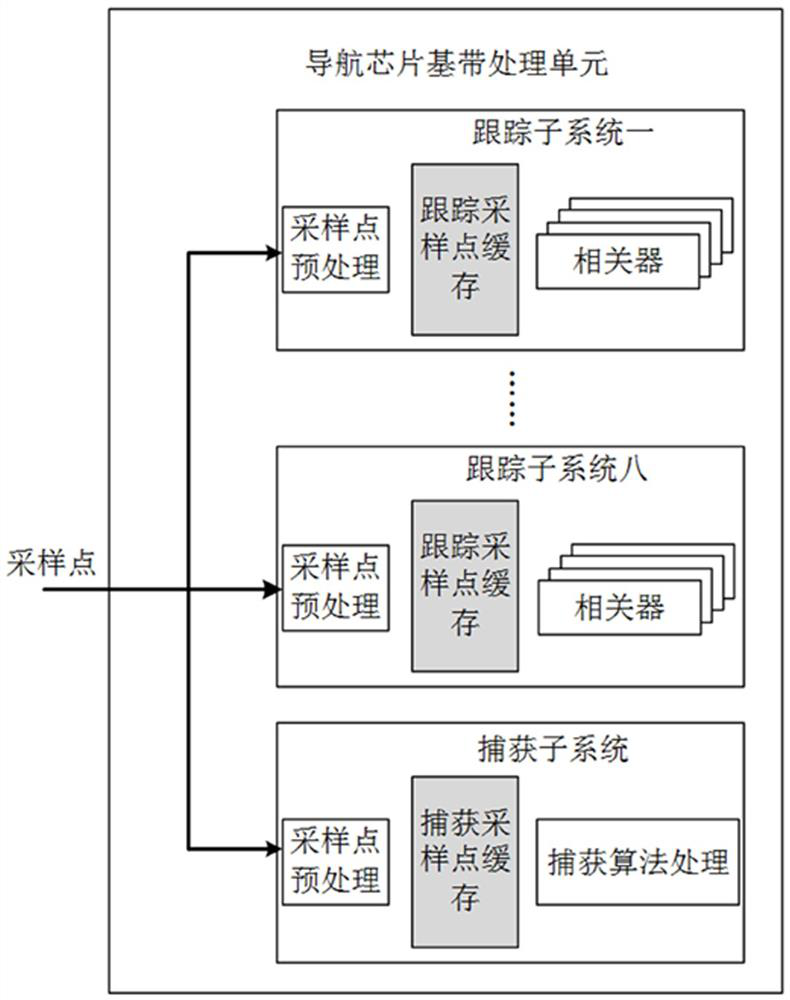

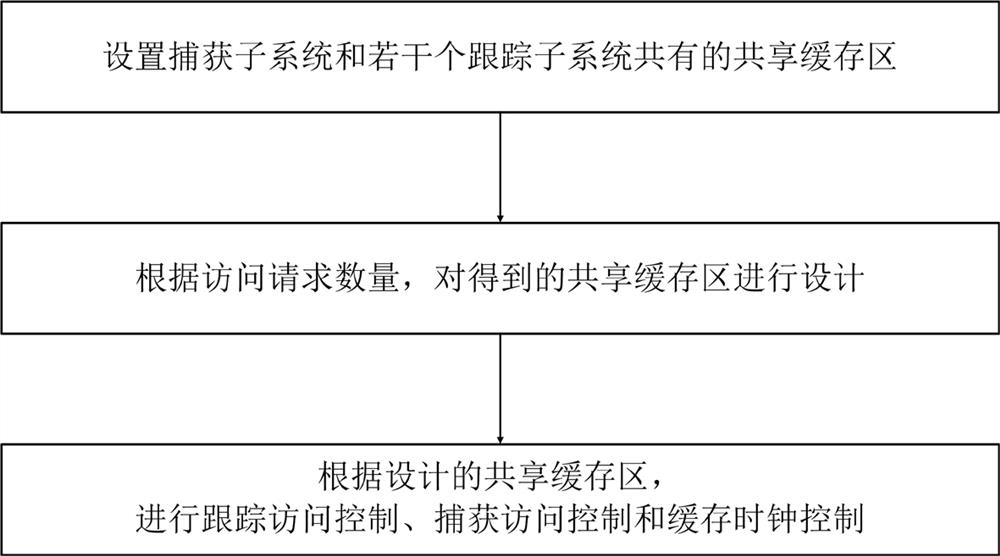

[0037] Such as figure 2 Shown is a schematic flow chart of the method of the present invention: the shared cache method provided by the present invention includes the following steps:

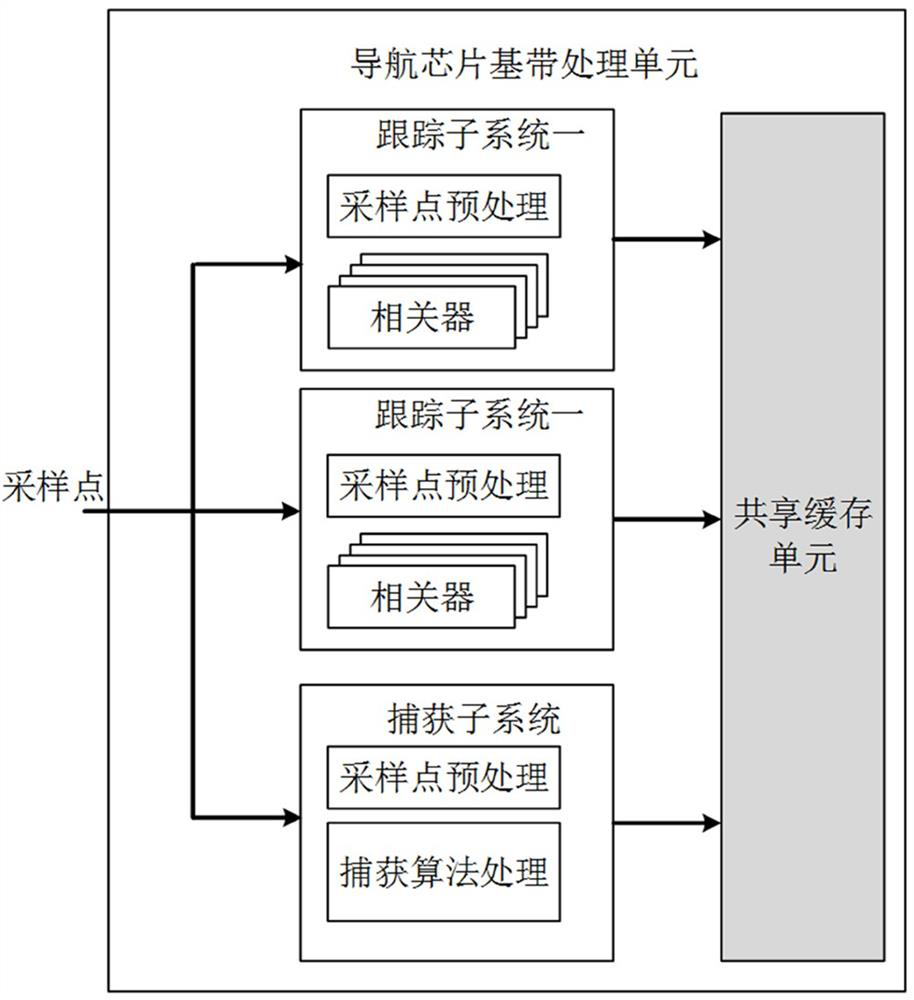

[0038] S1. Set up the shared buffer area shared by the capture subsystem and several tracking subsystems (such as image 3 shown);

[0039] S2. According to the number of access requests, design the shared buffer area obtained in step S1; specifically, there are A-way tracking subsystem and B-way capture subsystem; each way tracking subsystem has a1 write requests and a2 read requests , and a1+a2 requests of each tracking subsystem simultaneously access the same buffer area; each capture subsystem has b1 write requests, b2 read requests, and each capture subsystem has b1+b2 requests Time-sharing access to the same batch of cache intervals; a total of C KB is designed for the shared cache interval, and is divided into D cache units, each cache unit is E KB; A, B, a1, a2, b1, b2, C, D, and E a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More