Patents

Literature

89 results about "Buffer design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Apparatus and method for realizing accelerator of sparse convolutional neural network

InactiveCN107239824AImprove computing powerReduce response latencyDigital data processing detailsNeural architecturesAlgorithmBroadband

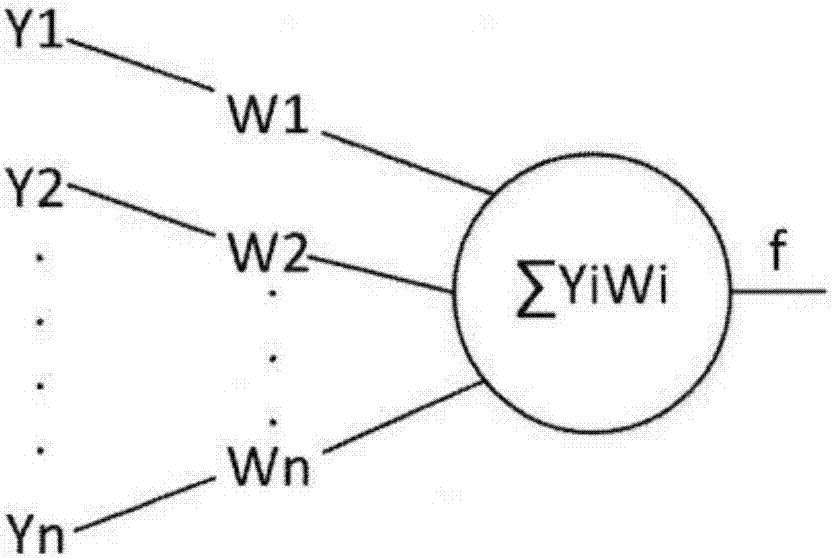

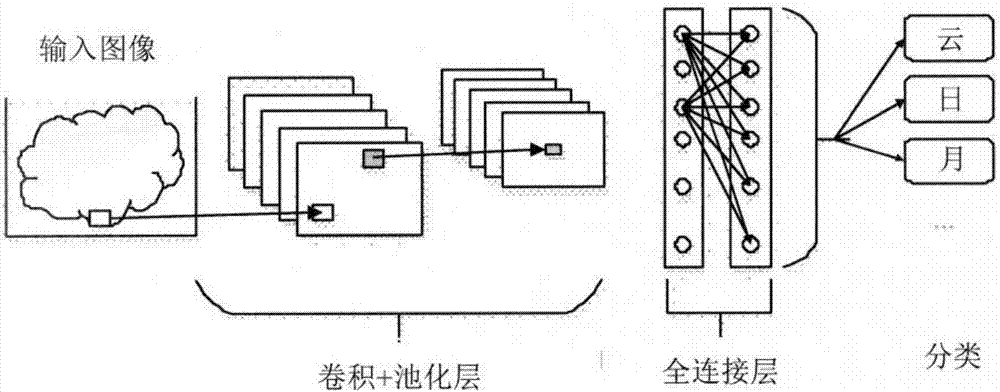

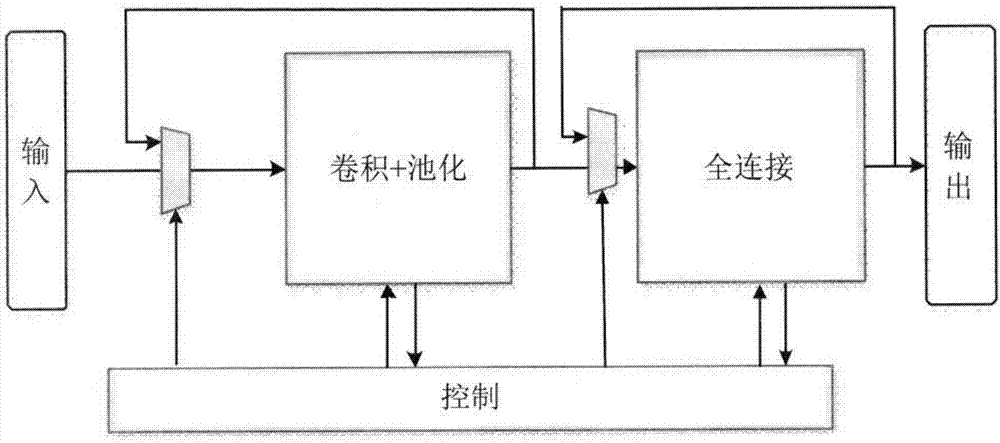

The invention provides an apparatus and method for realizing an accelerator of a sparse convolutional neural network. According to the invention, the apparatus herein includes a convolutional and pooling unit, a full connection unit and a control unit. The method includes the following steps: on the basis of control information, reading convolutional parameter information, and input data and intermediate computing data, and reading full connected layer weight matrix position information, in accordance with the convolutional parameter information, conducting convolution and pooling on the input data with first iteration times, then on the basis of the full connected layer weight matrix position information, conducting full connection computing with second iteration times. Each input data is divided into a plurality of sub-blocks, and the convolutional and pooling unit and the full connection unit separately operate on the plurality of sub-blocks in parallel. According to the invention, the apparatus herein uses a specific circuit, supports a full connected layer sparse convolutional neural network, uses parallel ping-pang buffer design and assembly line design, effectively balances I / O broadband and computing efficiency, and acquires better performance power consumption ratio.

Owner:XILINX INC

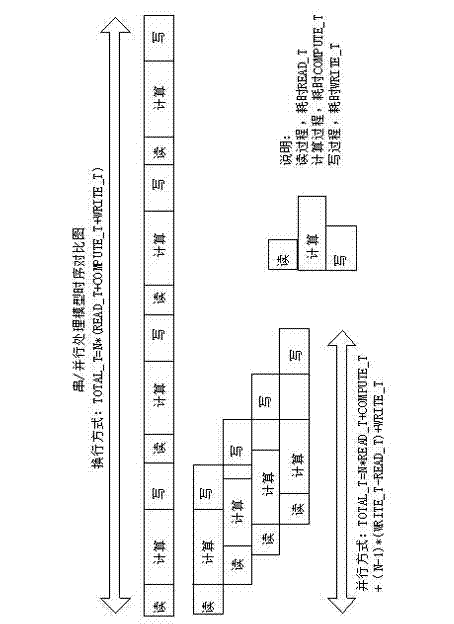

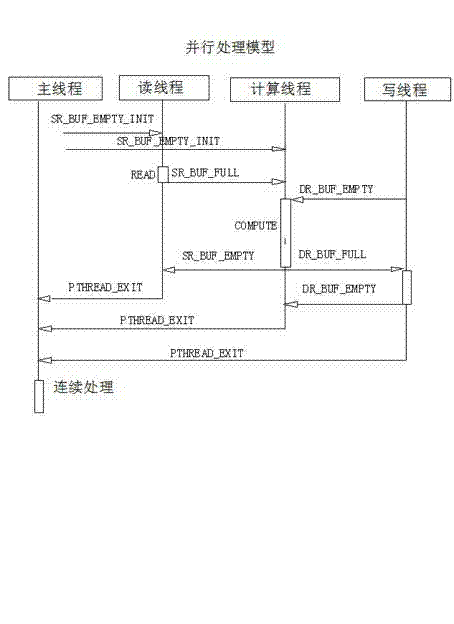

Software performance optimization method based on central processing unit (CPU) multi-core platform

ActiveCN103049245AImprove performanceReduce running timeResource allocationConcurrent instruction executionCache optimizationResource utilization

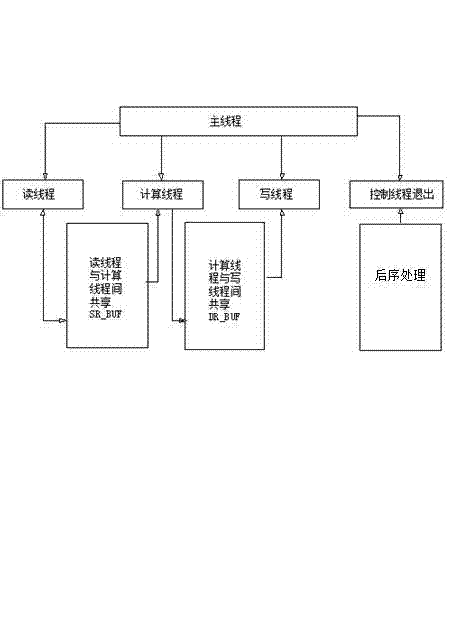

The invention provides a software performance optimization method based on a CPU multi-core platform. The method comprises software characteristic analysis, parallel optimization scheme formulation and parallel optimization scheme implementation and iteration tuning. Particularly, the method comprises application software characteristic analysis, serial algorithm analysis, CPU multi-in / thread parallel algorithm design, multi-buffer design, design of communication modes among threads, memory access optimization, cache optimization, processor vectorization optimization, mathematical function library optimization and the like. The method is widely applicable to application occasions with multi-thread parallel processing requirements, software developers are guided to perform multi-thread parallel optimization improvement on prior software rapidly and efficiently with short developing periods and low developing costs, the utilization of system resources by software is optimized, data reading and computing and mutual masking of write-back data are achieved, the software running time is shortened furthest, the hardware resource utilization rate is improved apparently, and the software computing efficiency and the software whole performance are enhanced.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

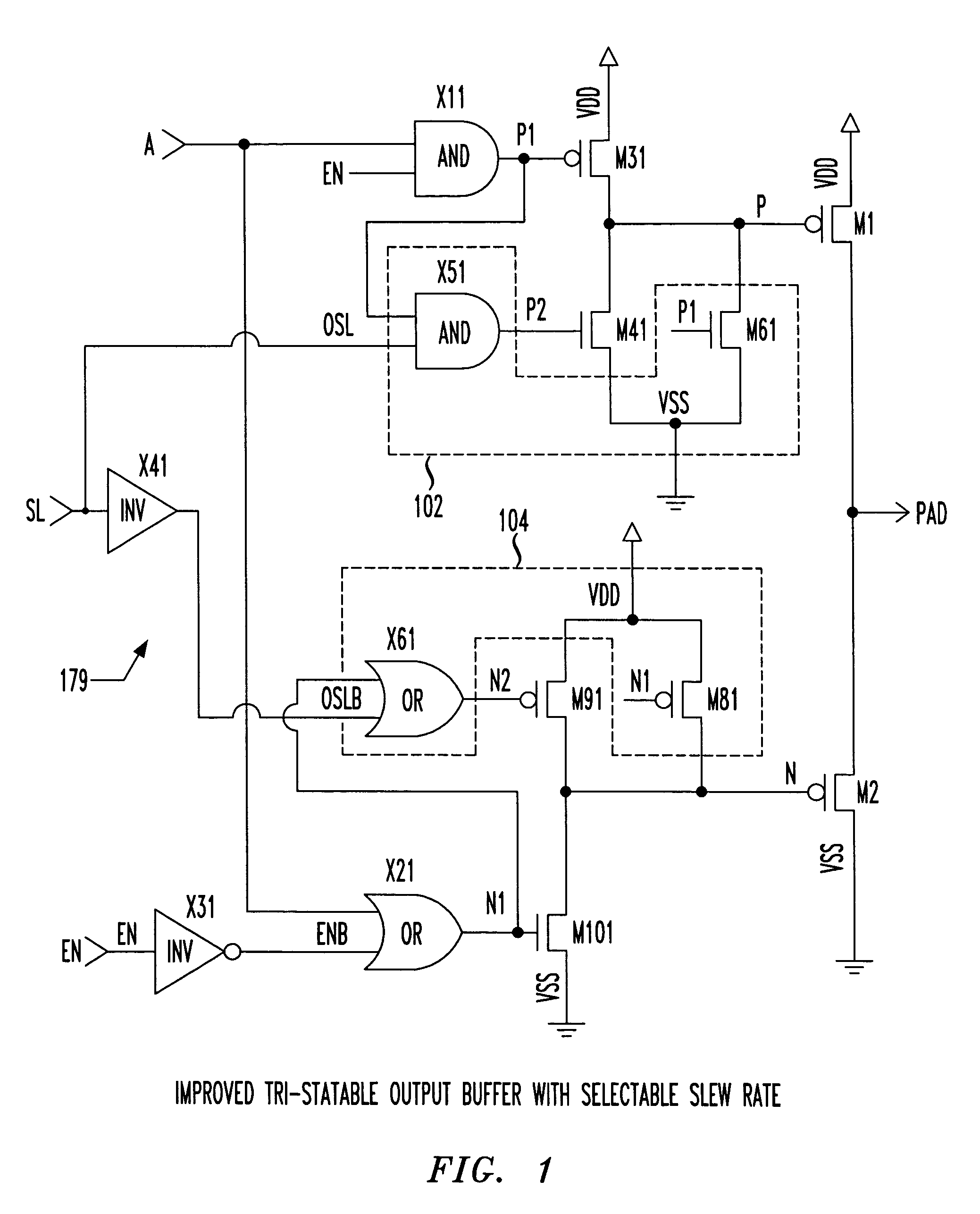

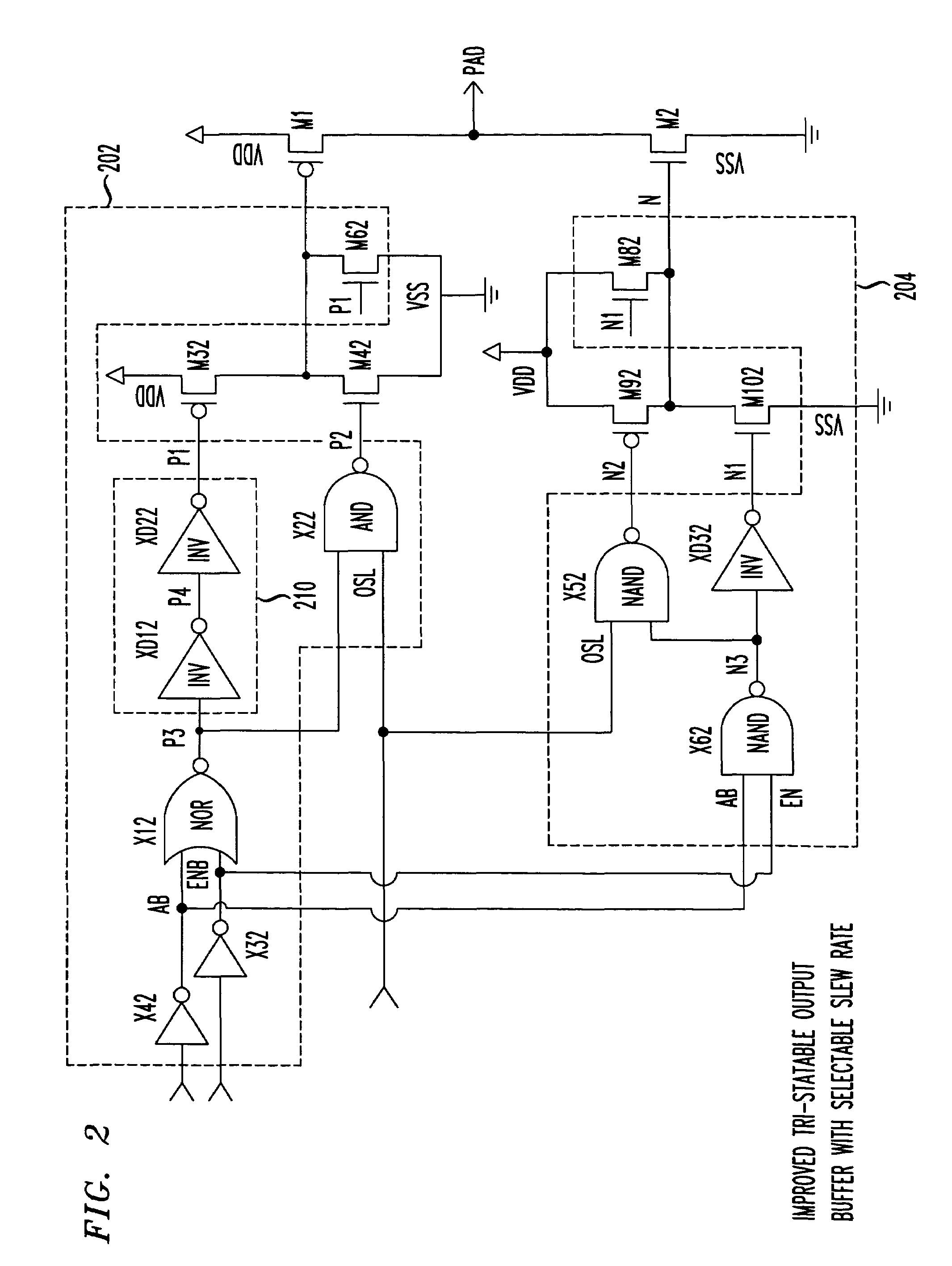

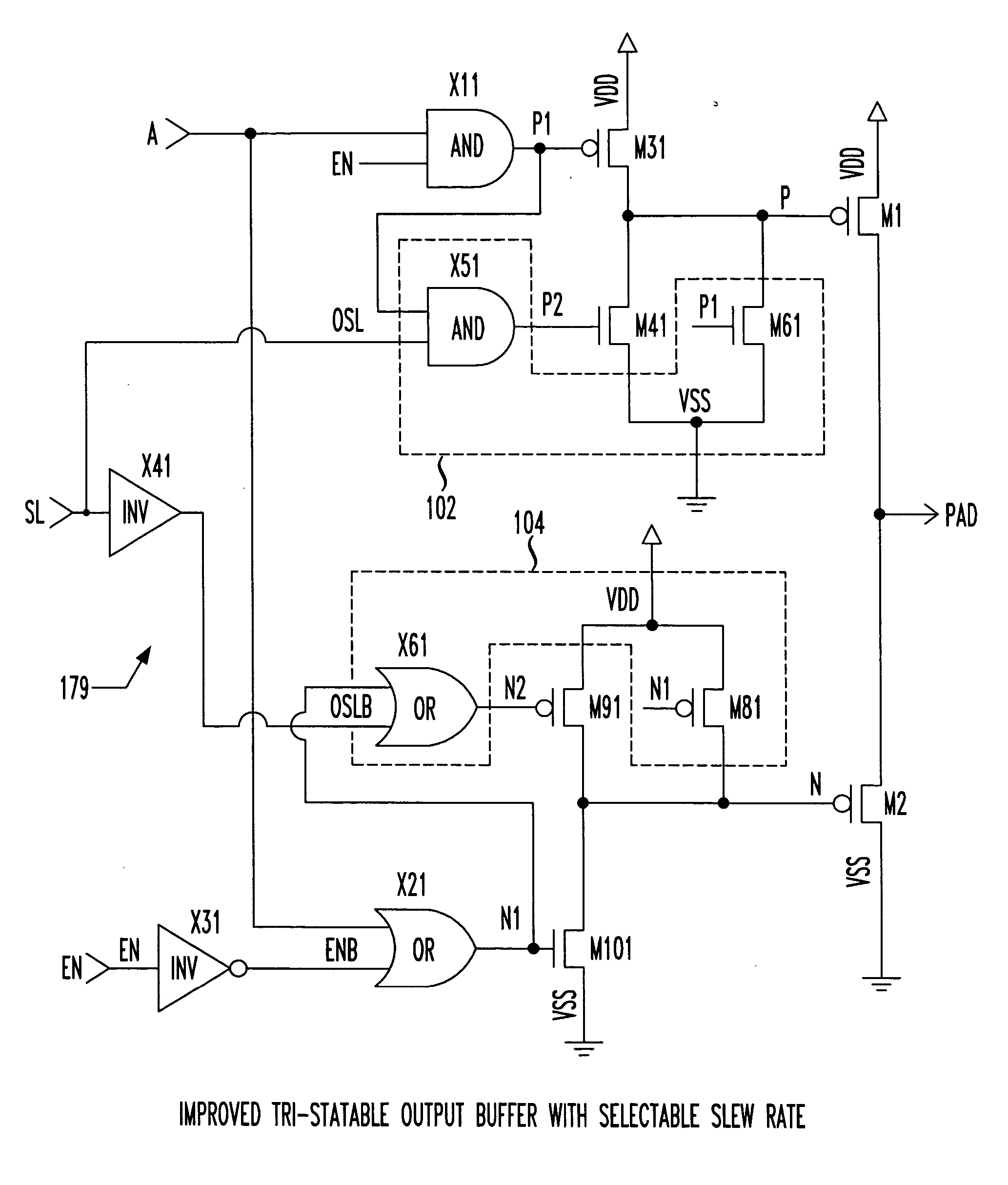

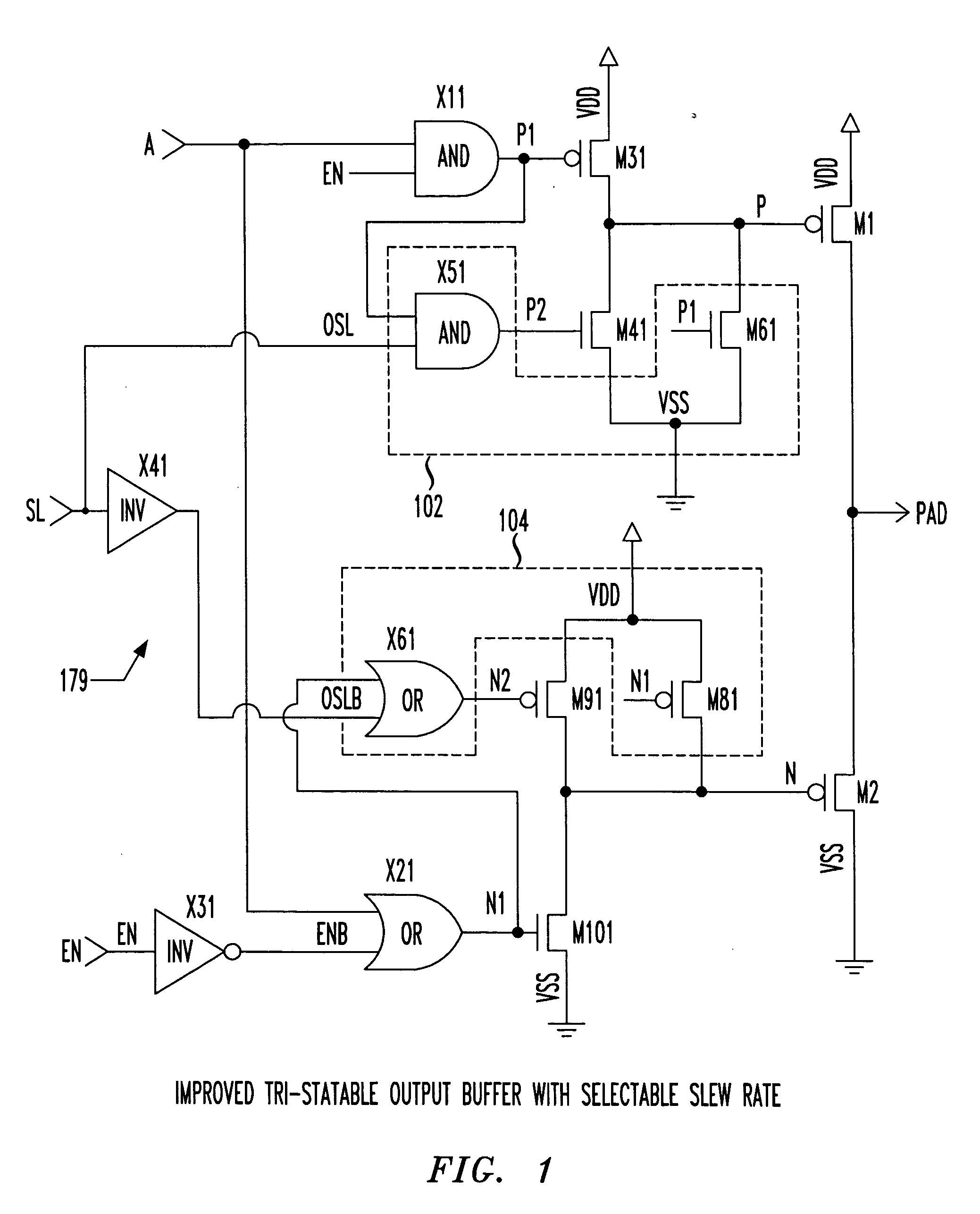

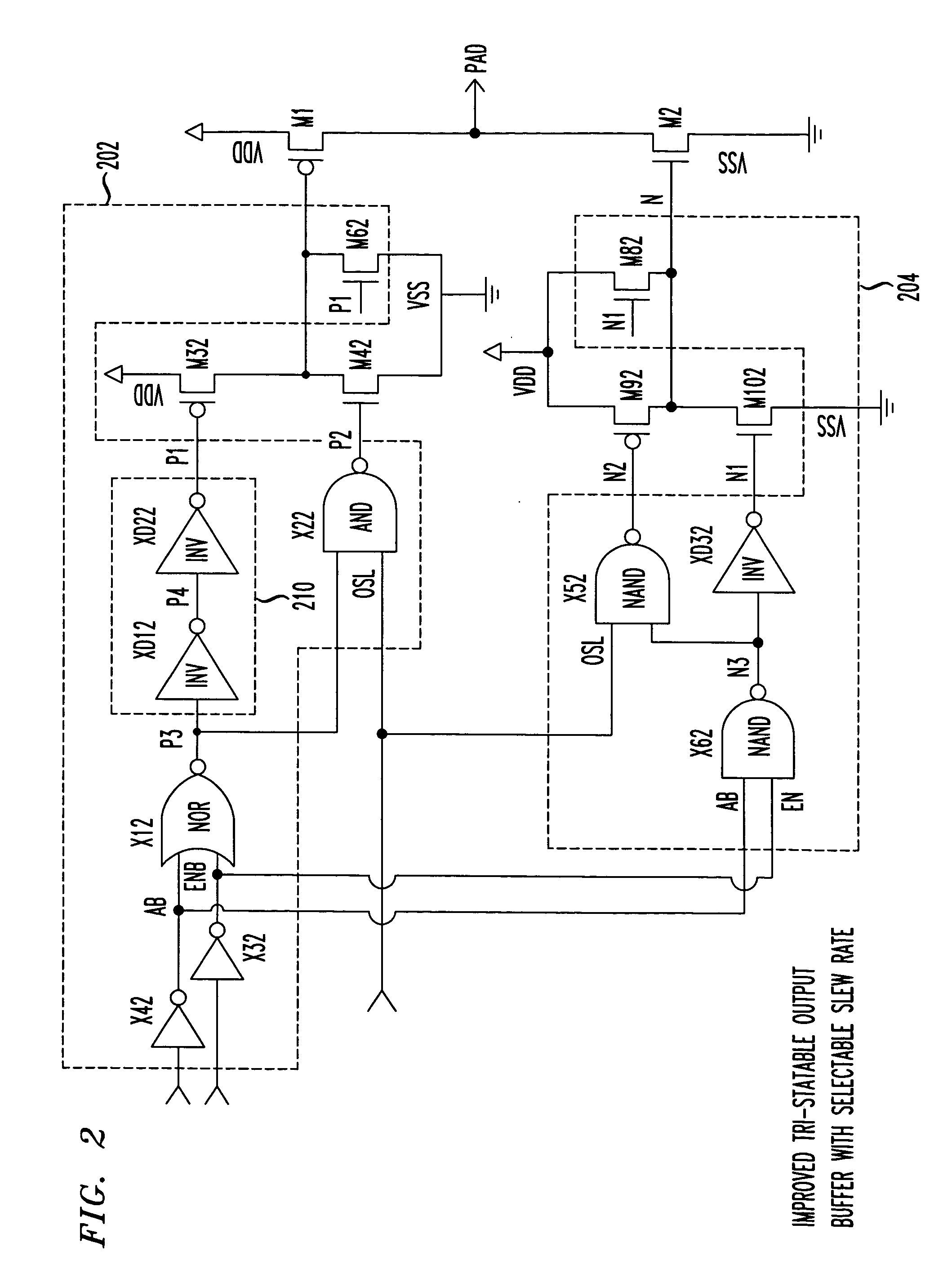

Output buffer with selectable slew rate

A buffer design for an integrated circuit that has adjustable slew rate control, yet requires significantly less space to fabricate than does a conventional buffer with slew rate control. A new slew rate control circuit design is added to a Complementary Metal Oxide Semiconductor CMOS buffer to implement slew rate control in the buffer (e.g., selection between a high slew rate and a low slew rate). The new slew rate control circuit requires significantly less space to fabricate, and when applied to each buffer in an given integrated circuit, e.g., input / output buffers that may be placed along the periphery of the integrated circuit, the savings can be extraordinary.

Owner:AVAGO TECH INT SALES PTE LTD

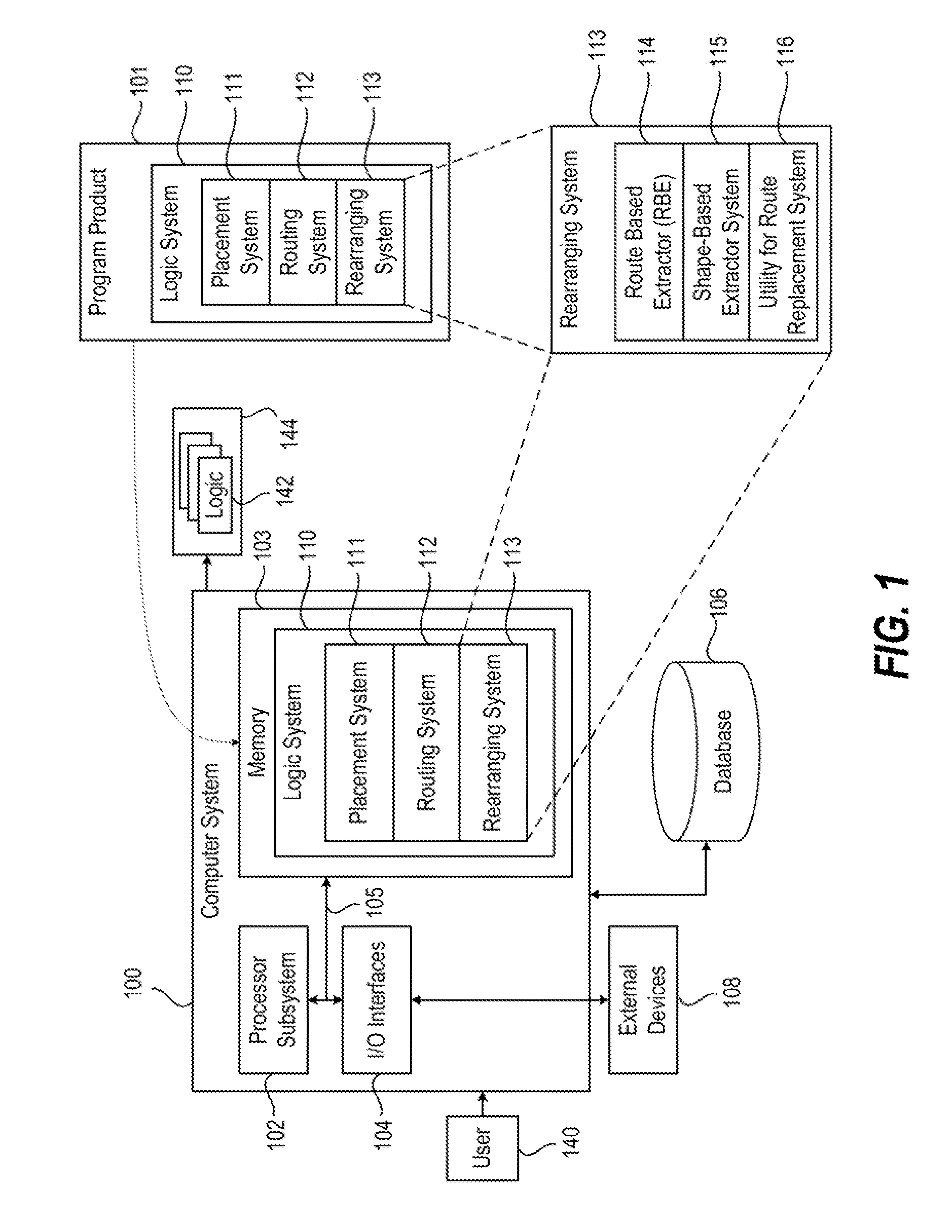

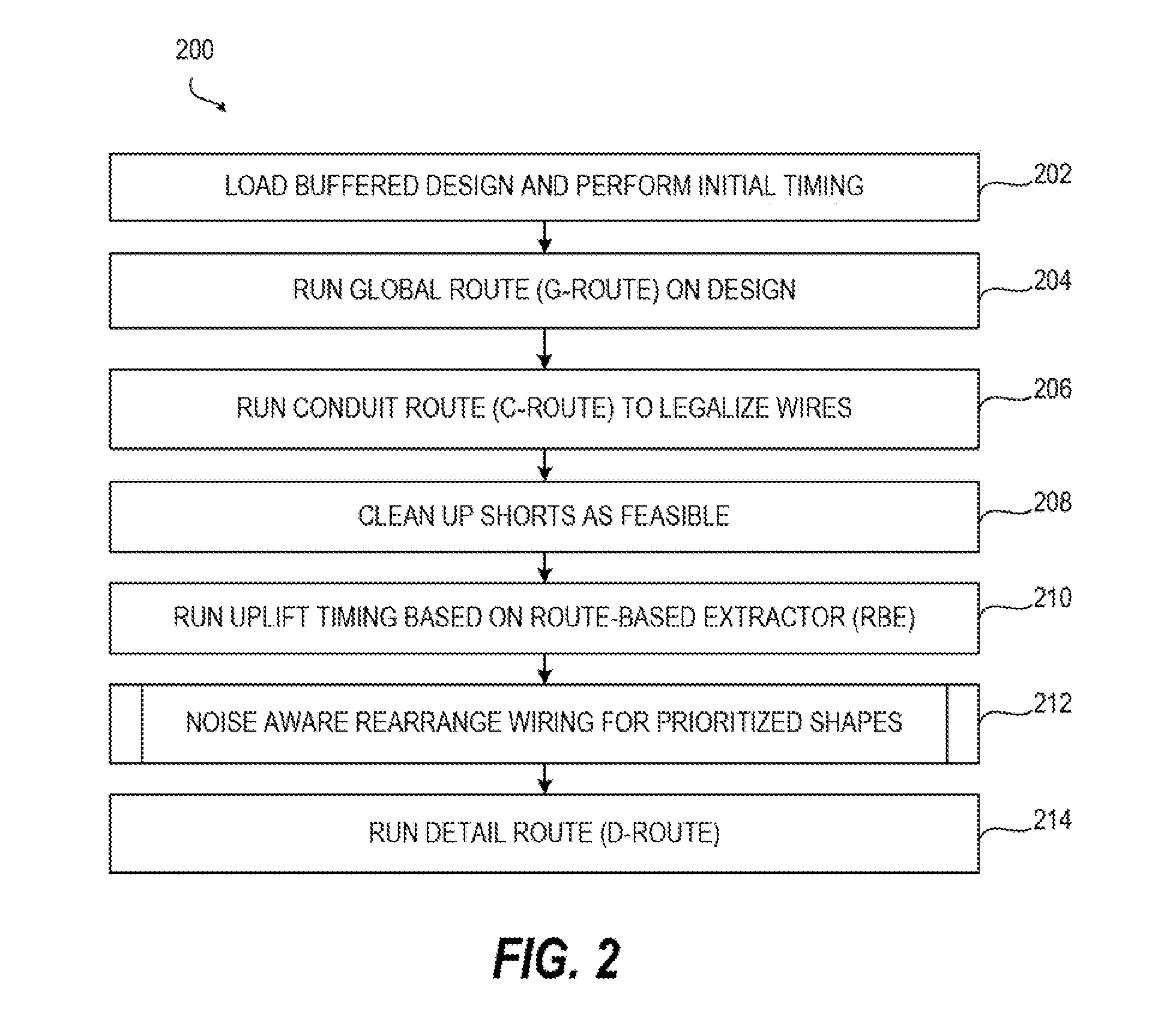

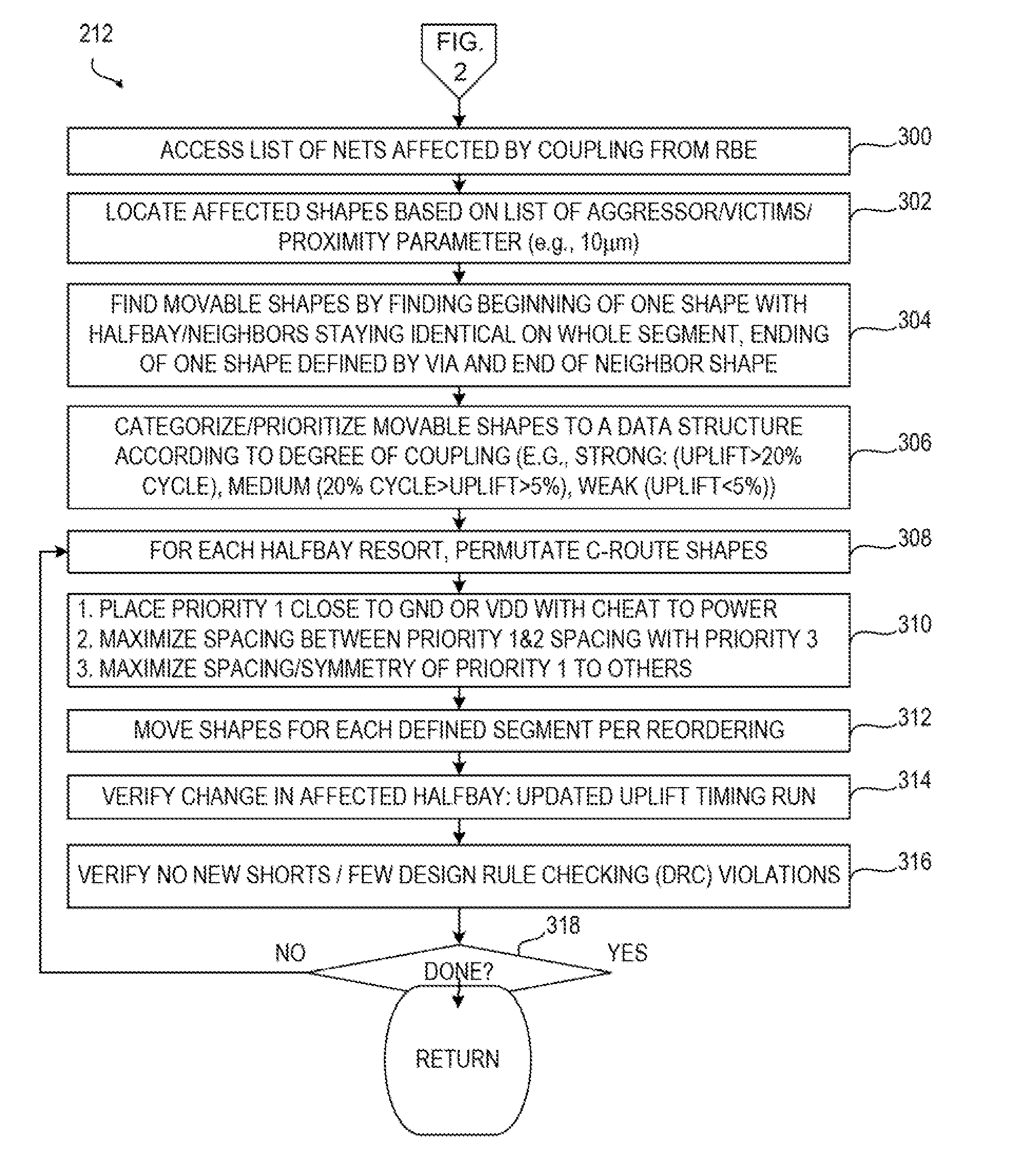

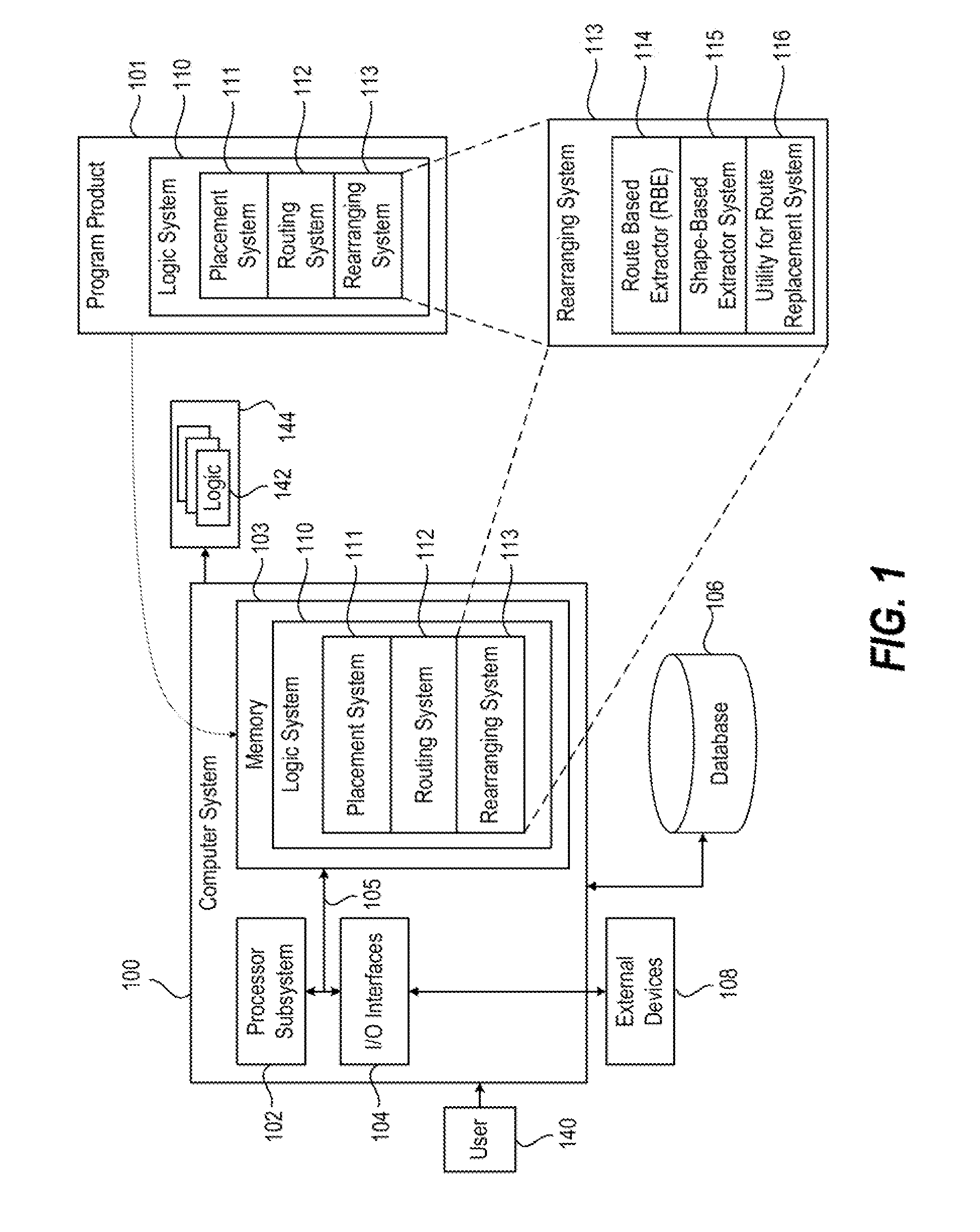

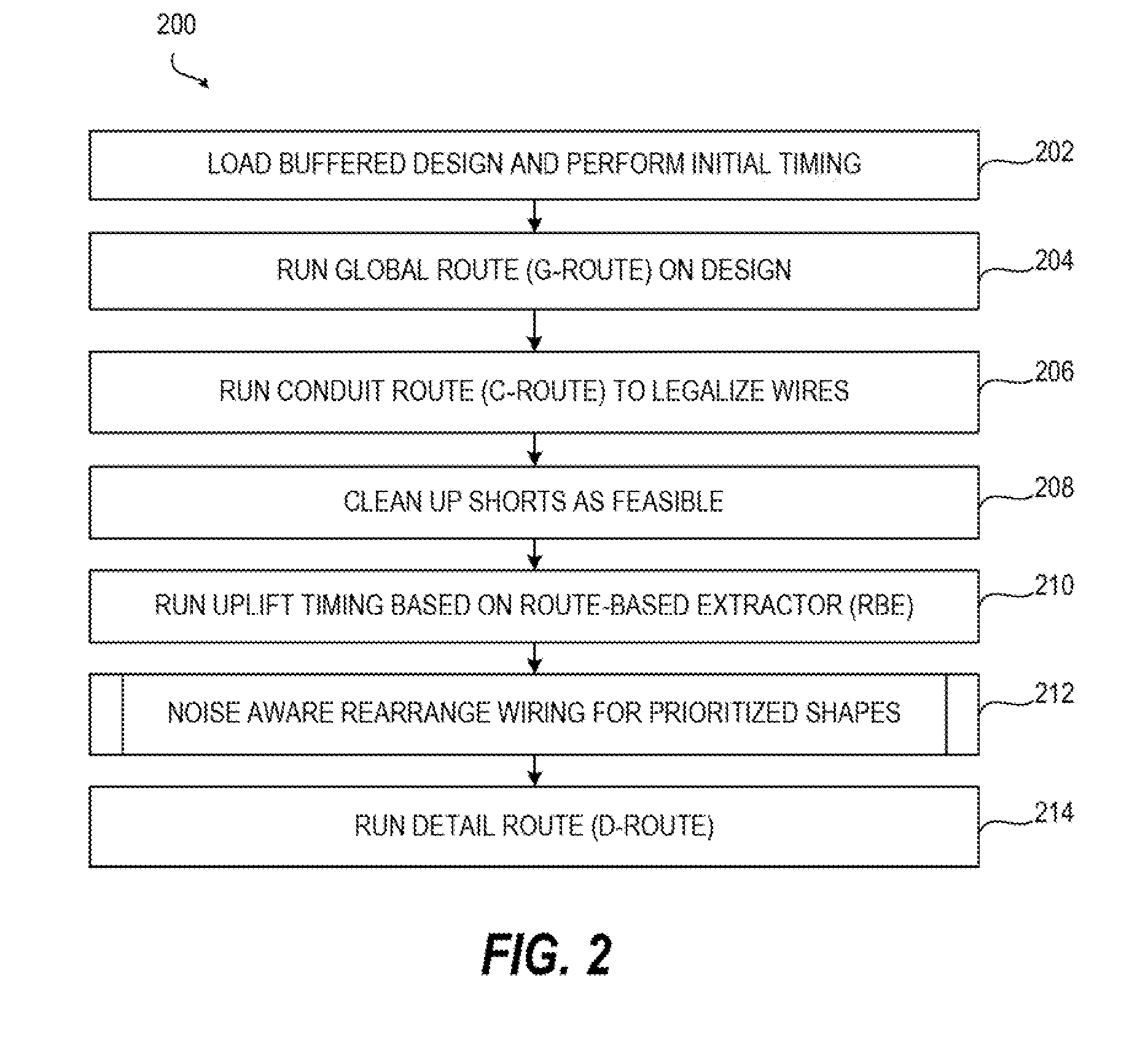

Early noise detection and noise aware routing in circuit design

InactiveUS8423940B2Reduce noiseComputer programmed simultaneously with data introductionComputer aided designData processing systemNoise detection

A computerized method, data processing system and computer program product reduce noise for a buffered design of an electronic circuit which was already placed and routed. For all areas between a power stripe and a ground stripe (half bay) in the design, the shapes are divided in different criticality levels. The shapes are rearranged based on their criticality level such that shapes with higher criticality level are placed closer to the stripes than those with lower criticality level.

Owner:GLOBALFOUNDRIES INC

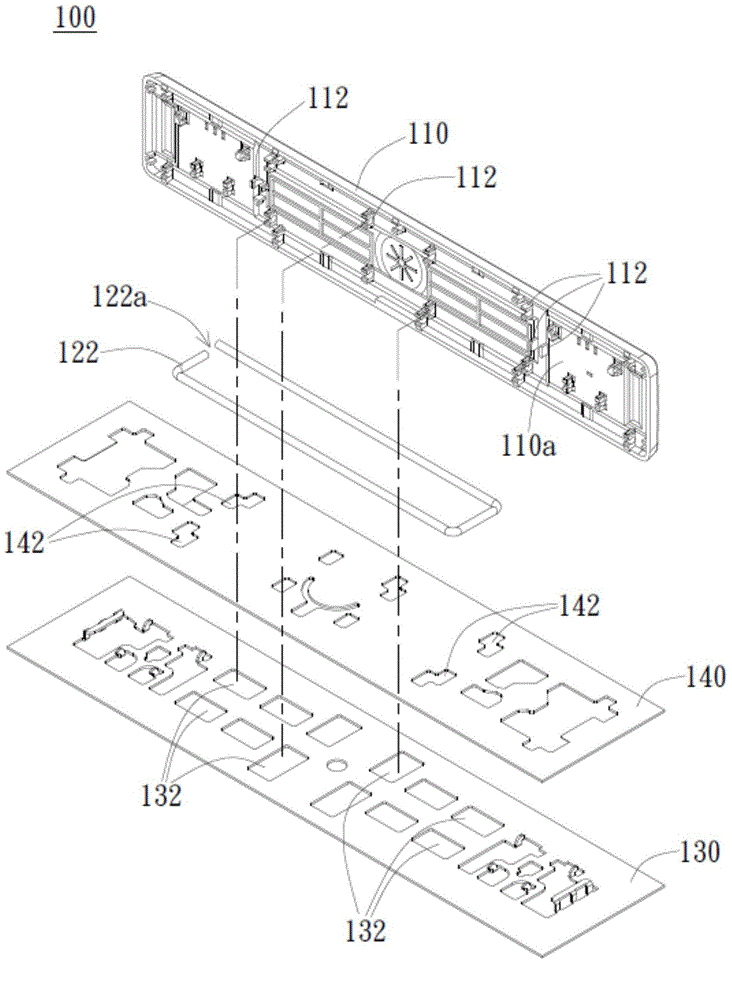

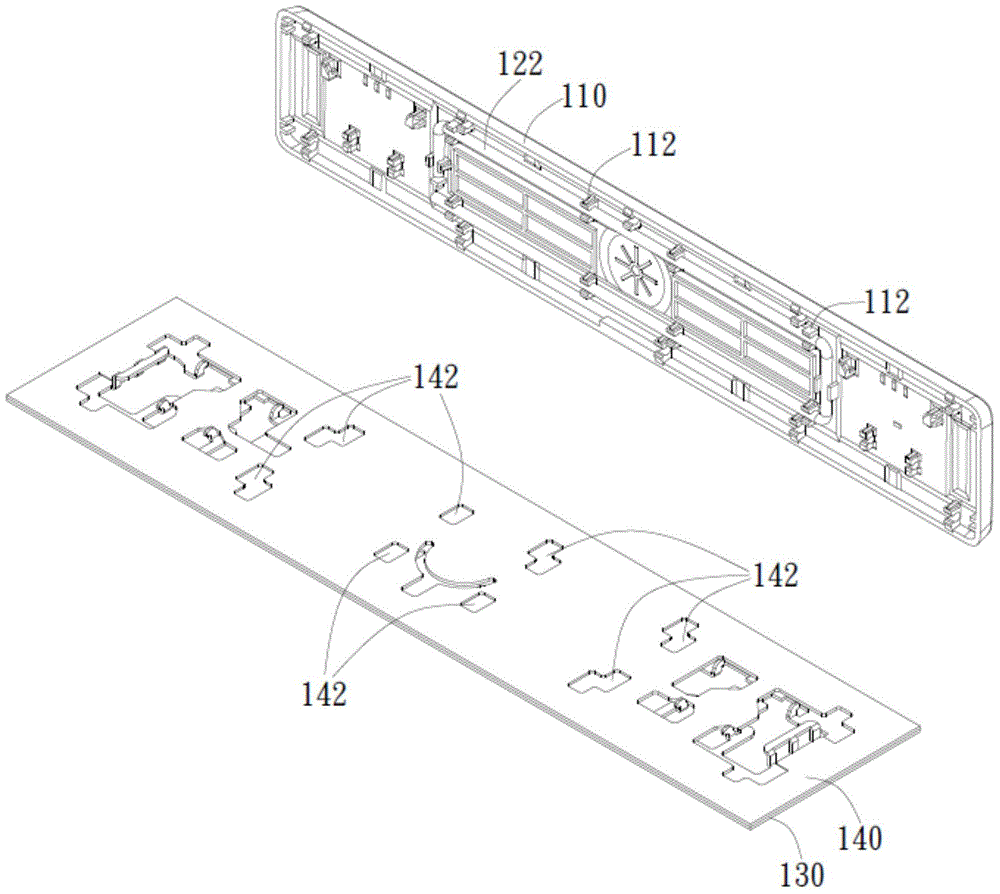

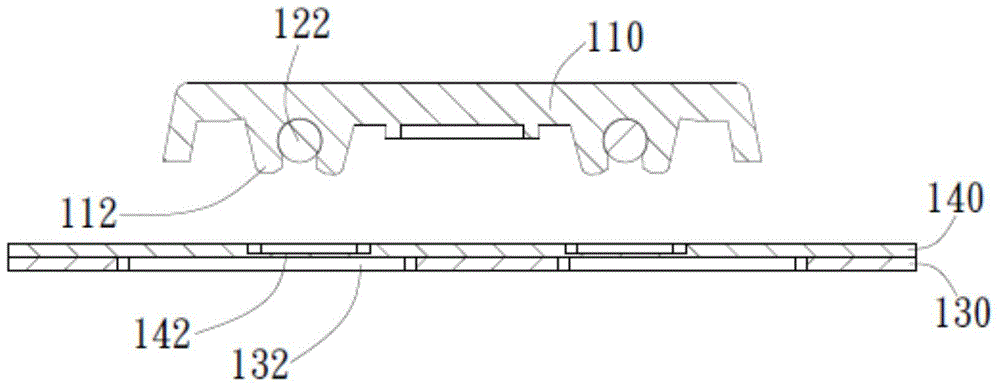

Button structure

ActiveCN104882318AAvoid or reduce noiseEmergency actuatorsContact mechanismsMembrane switchEngineering

The invention relates to a button structure. The button structure comprises a keycap, balance rods, a base plate, and a buffer plate, wherein the keycap comprises combination portions and a lower surface, the combination portions protrude from the lower surface, and when the keycap is pressed, the keycap moves downwardly to a decrease position; the balance rods are connected to the combination portions, and when the keycap is positioned at the decrease position, the lower points of the combination portions are lower than the balance rods; the base plate is arranged below the keycap, the base plate comprises recessed spaces corresponding to the combination portions, the buffer plate is arranged on the base plate, the buffer plate covers the recessed spaces and comprises deformable portions corresponding to the recessed spaces, and when the keycap moves to a lower position towards the base plate, the lower points of the combination portions are abutted against the deformable portions, and the deformable portions extend into the recessed spaces. According to the buffer design of the button structure, buffer elasticity can be provided during button operation, noises generated by direct collision with the base plate of the keycap can be avoided or reduced, and a multilayer structure of a membrane switch forms the buffer design so that the material cost is not increased, and the function of noise reduction can be effectively performed.

Owner:DARFON ELECTRONICS (SUZHOU) CO LTD +1

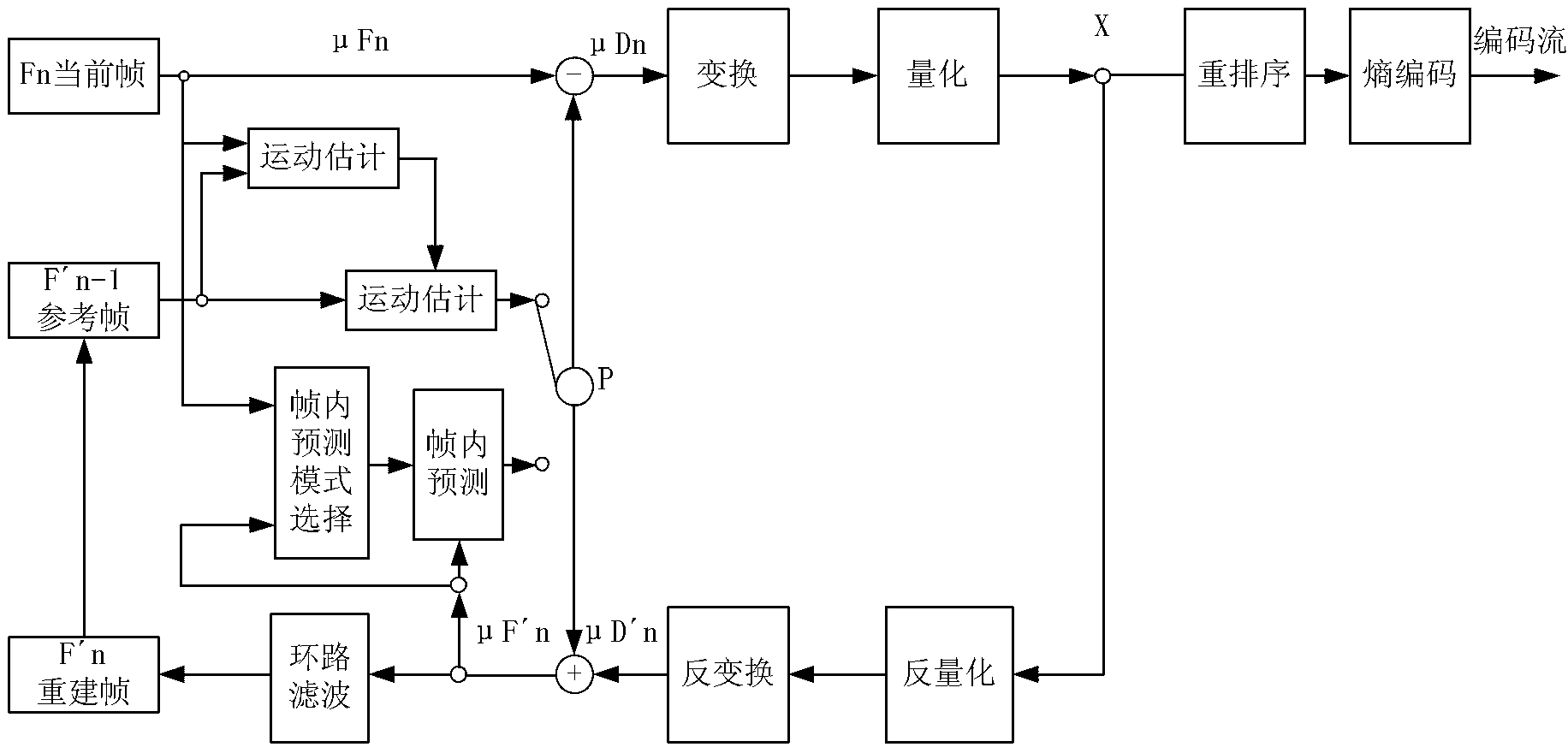

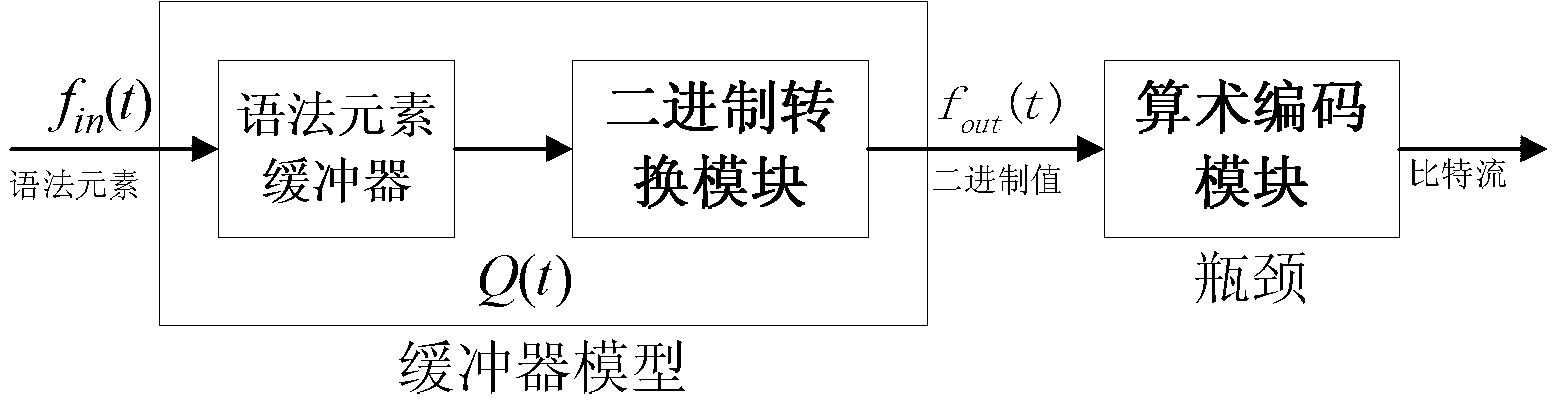

Arithmetic coder and coding method

ActiveCN103227924ASimple structureTelevision systemsDigital video signal modificationCode moduleAlgorithm

The invention discloses a design method of an arithmetic coder, and a realization device, which comprise a front-buffer design, algorithm structure joint optimization, a muti-bin processing technology and a hybrid context storage mechanism, wherein the front-buffer design is used for solving the problems that the number of binary sequences (bin) generated by a macroblock after binary conversion can fluctuate within a very wide range, but the number of the binary sequences (bin) processed by a binary arithmetic coding module (BAC) in unit time is limited; the algorithm structure joint optimization mainly uses a time borrowing technology to place low processing after range processing; the muti-bin processing technology utilizes MPS (microprocessor system) computation more easily compared with an LPS (lean process solution), so that people can process multiple MPSs in a clock period; and the hybrid context storage mechanism is a storage method invented for a special application of a 2bins / cycle throughput rate, can store a large number of context models, and can conduct quick memory on the models. The arithmetic coder and the coding method are applicable to coding of a multi-stage pipeline structure, in particular to real-time coding of high-definition resolution.

Owner:PEKING UNIV

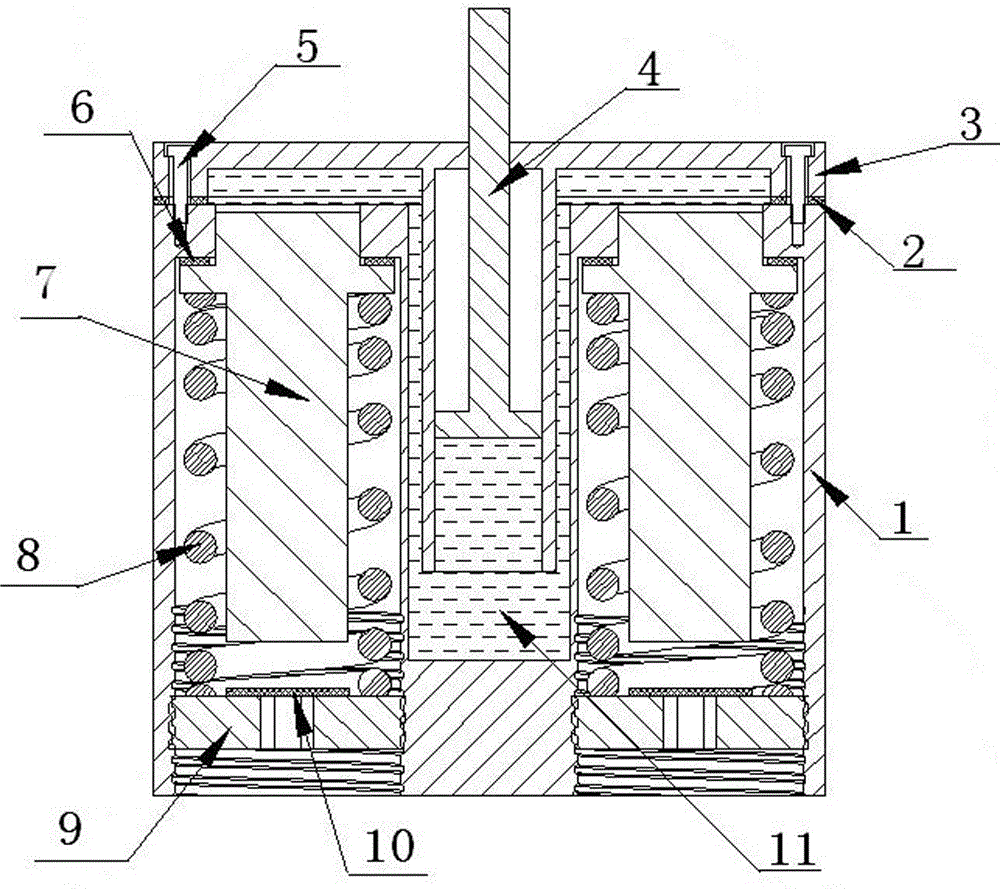

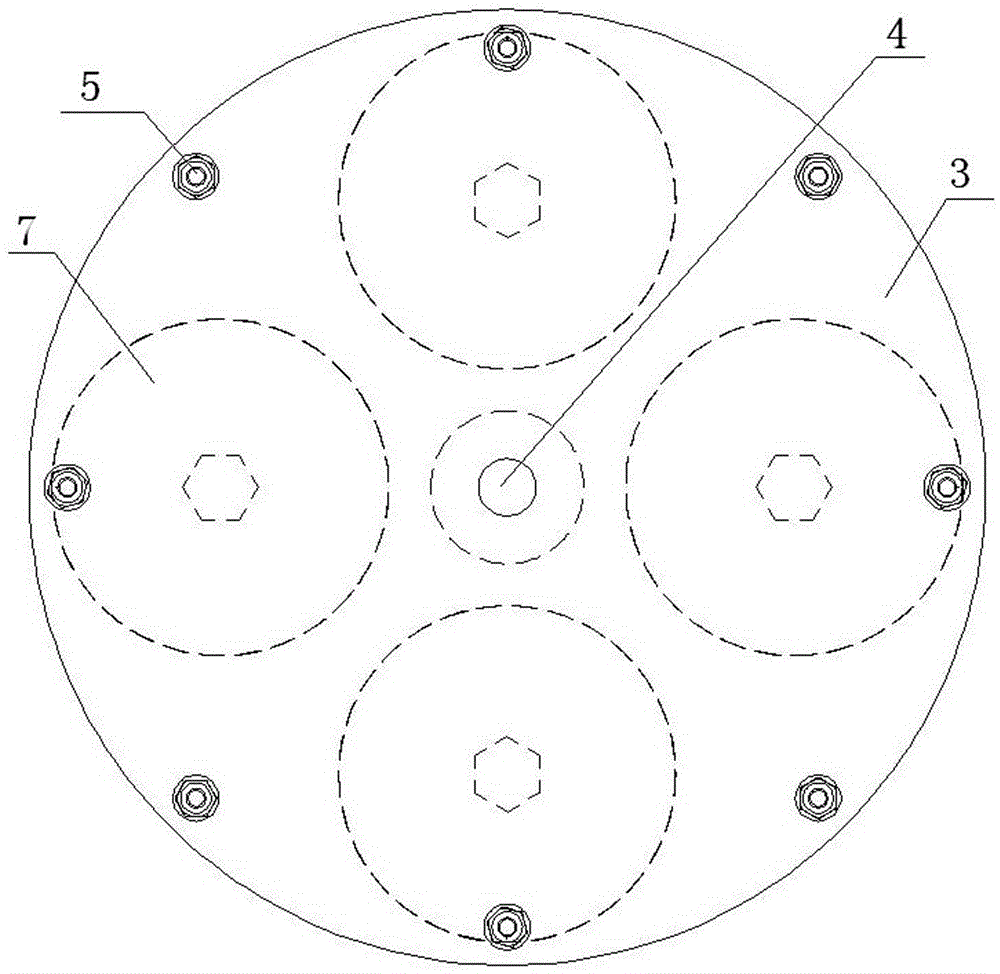

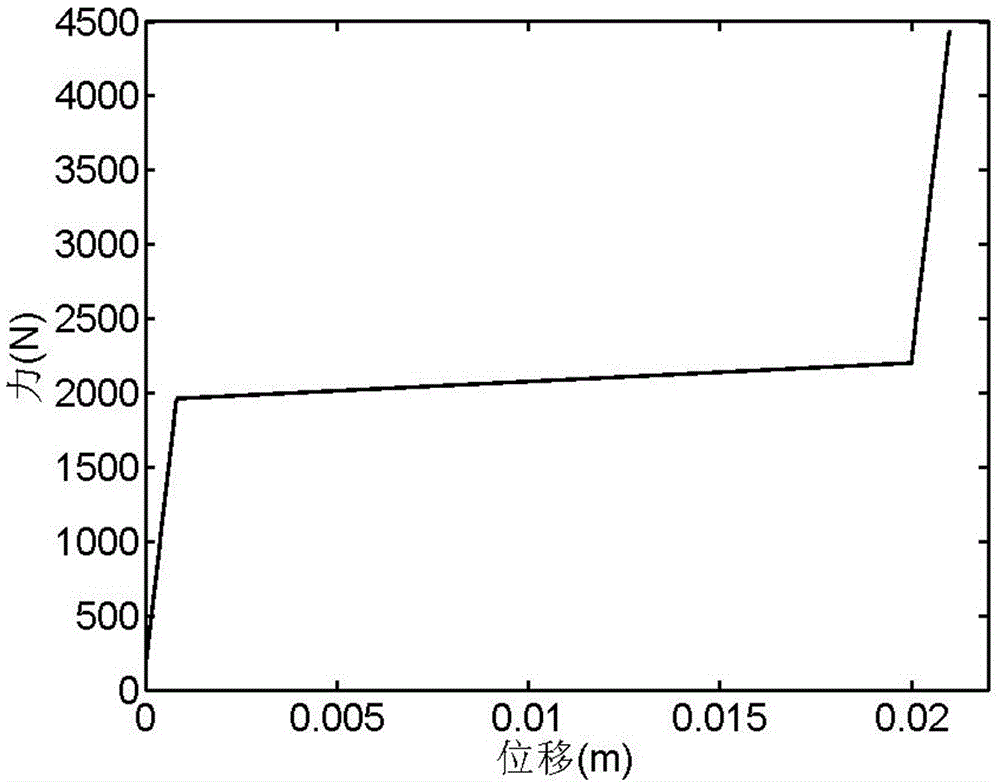

Mechanical molecular spring vibration isolation buffer device

ActiveCN106801716AAchieve high static and low dynamic stiffness characteristicsLow working water pressureSolid based dampersWorking pressureEngineering

The invention discloses a mechanical molecular spring vibration isolation buffer device. In a mechanical molecular spring vibration isolation buffer technology, water is used as a force transferring medium, and pistons and pre-compressed springs are used as force bearing components; a vibration isolation buffer designed on the basis of the mechanical molecular spring vibration isolation buffer technology mainly comprises a main piston, a plurality of secondary pistons, a cylinder body and an upper end cover; the main piston is used for carrying the mass; each secondary piston is connected with a pre-compressed spring with specific rigidity; the cylinder body is filled up with water. The mechanical molecular spring vibration isolation buffer has distinct piecewise linear rigidity, comprises a bearing section, a working section and a limiting section, can achieve high-static and low-dynamic rigidity characteristics, has the characteristics of low working pressure intensity, adjustable performance parameters and the like, and is especially applicable to the low-frequency overloading field.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

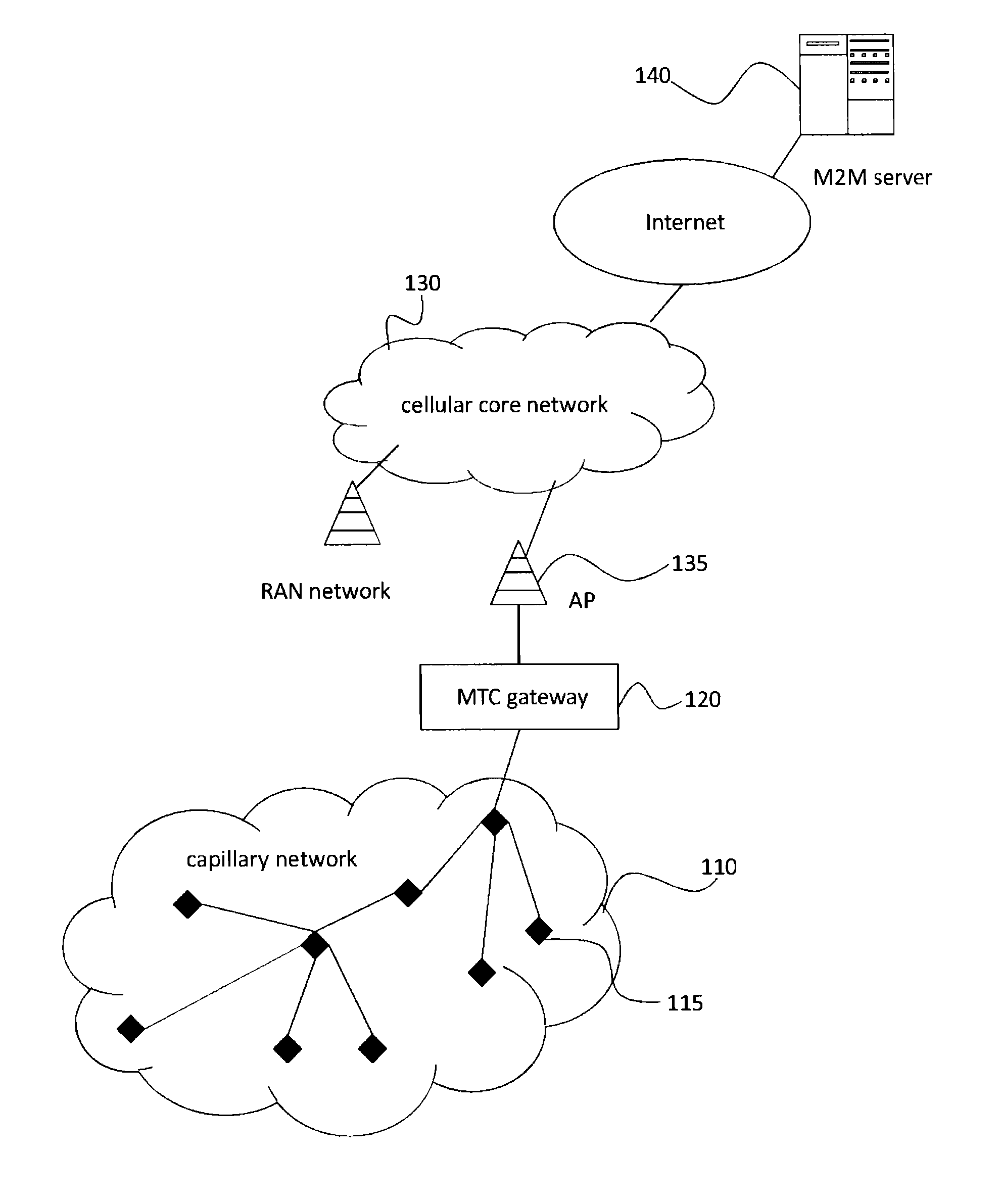

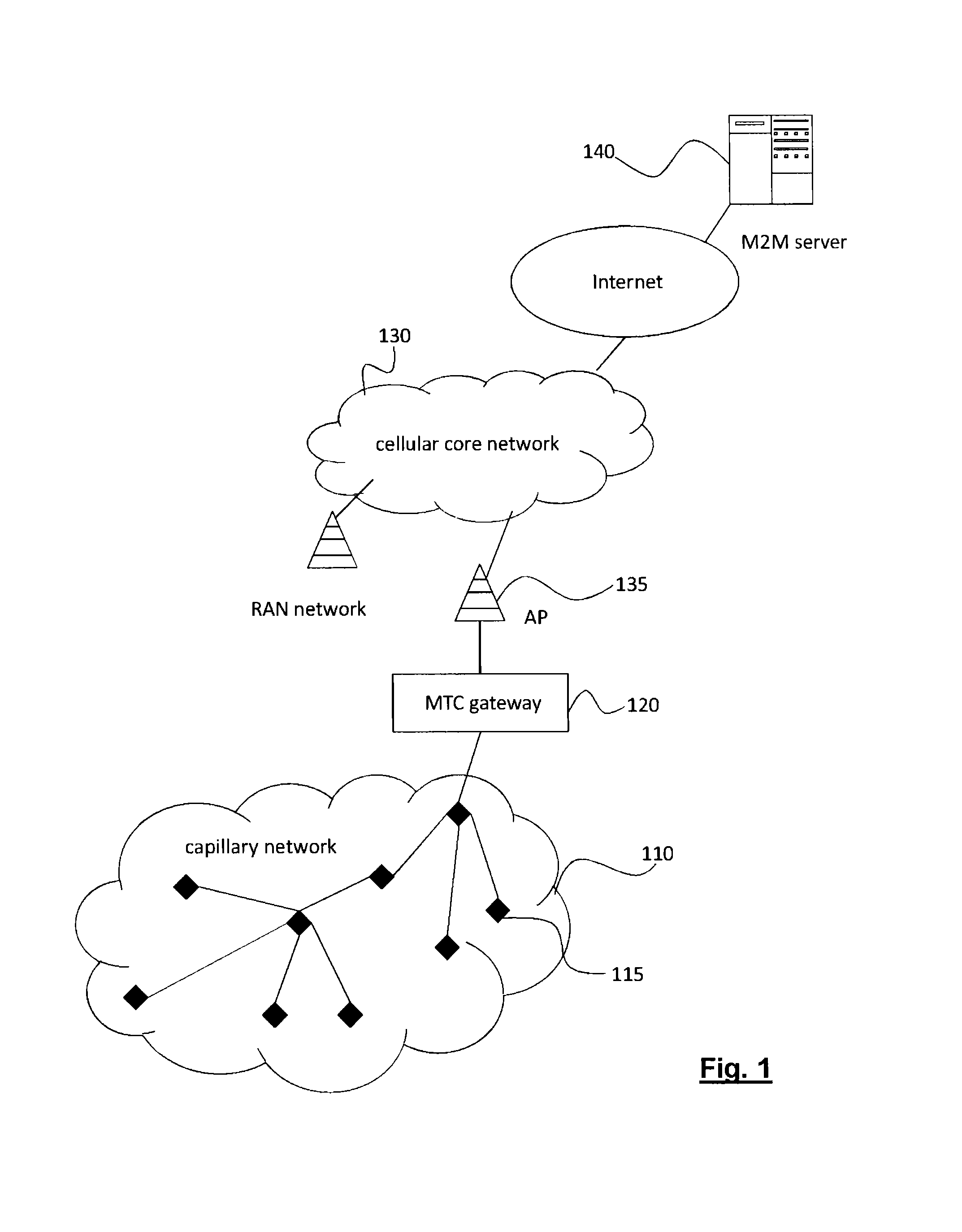

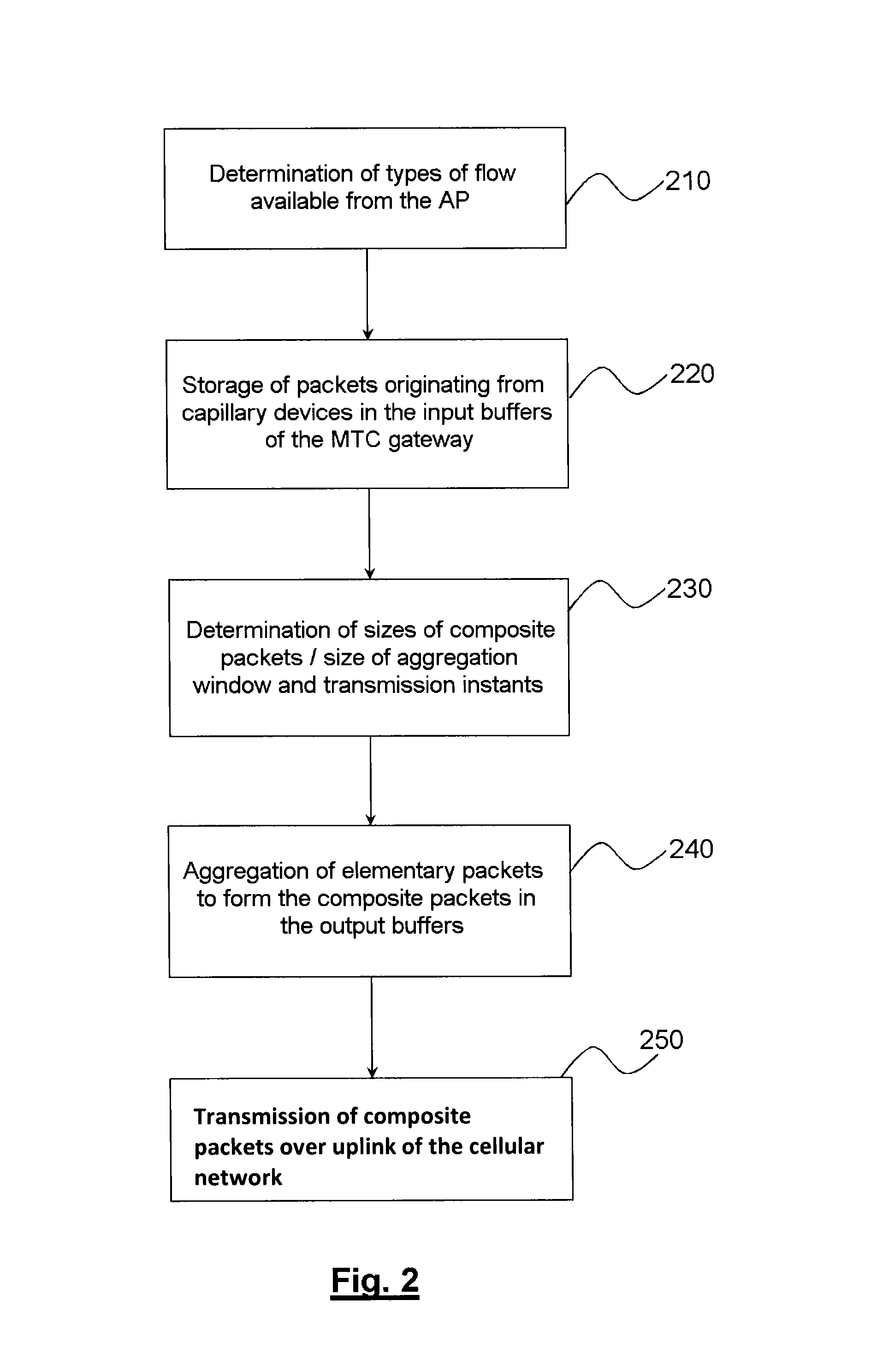

Traffic management gateway for machine-to-machine network

A gateway for interfacing a capillary network of communicating devices with an access point of a cellular network. The gateway includes a plurality of input buffers designed to store elementary packets. A plurality of output buffers store composite packets formed by aggregation of elementary packets, each output buffer being associated with a type of flow of the cellular network. A flow regulator determines for each output buffer, parameters of size and / or transmission times of the composite packets such that the flow of these packets is consistent with the type of flow of the cellular network associated with the output buffer. A multiplexing device transfers and aggregates elementary packets, stored in the input buffers, in the form of composite packets having the parameters determined by the flow regulator. A scheduling device for transmitting the composite packets by the transmission resources of the cellular network.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

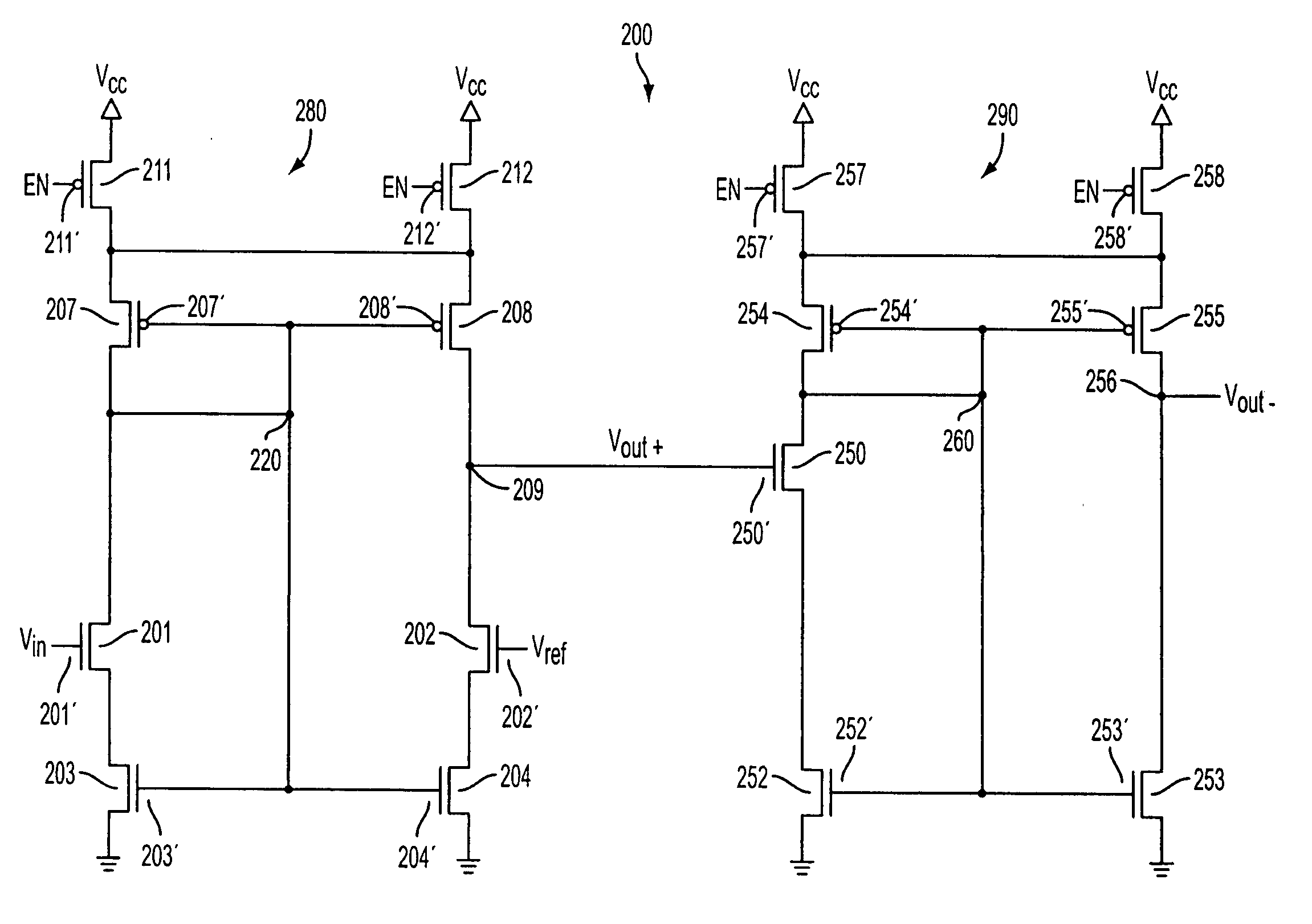

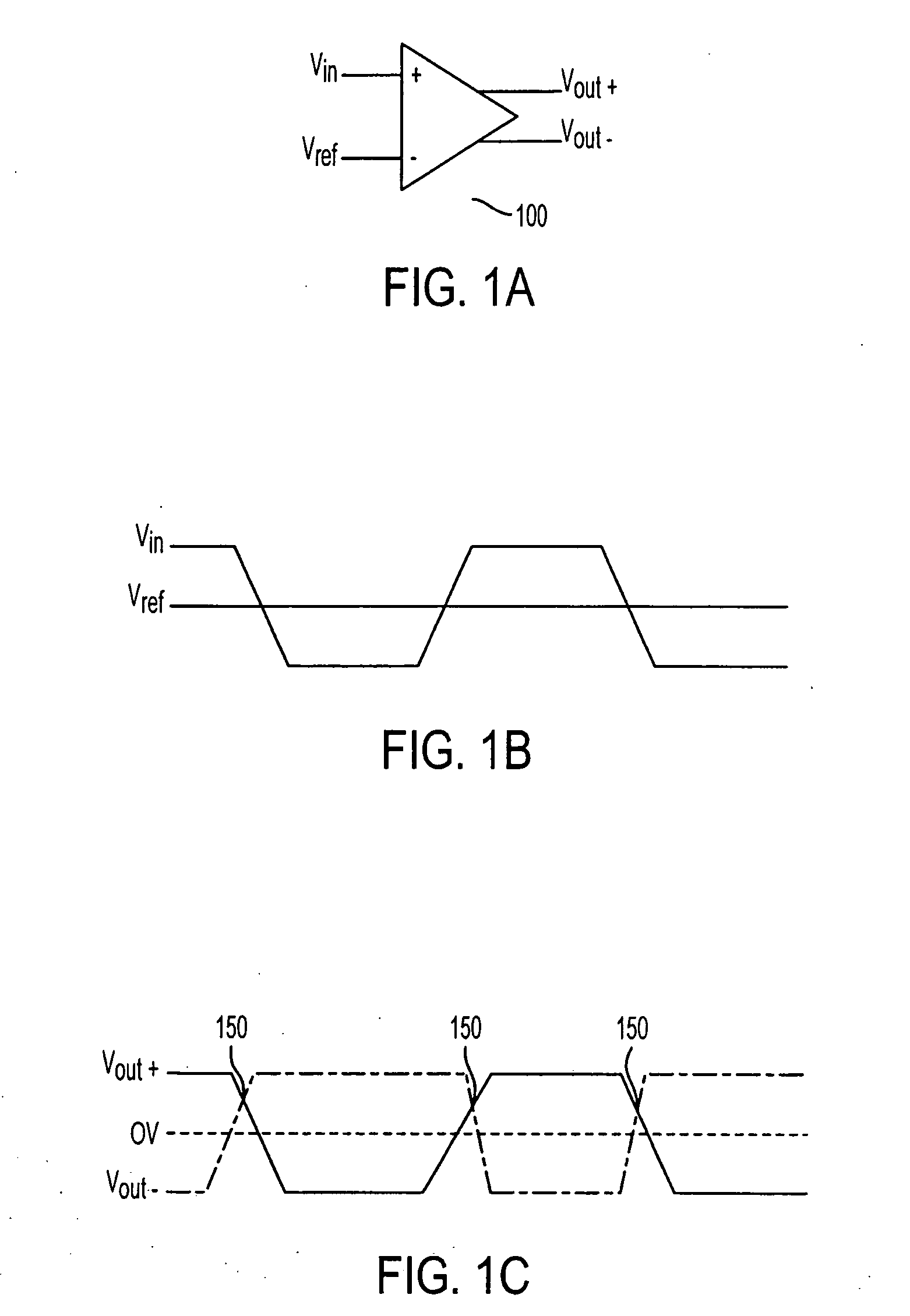

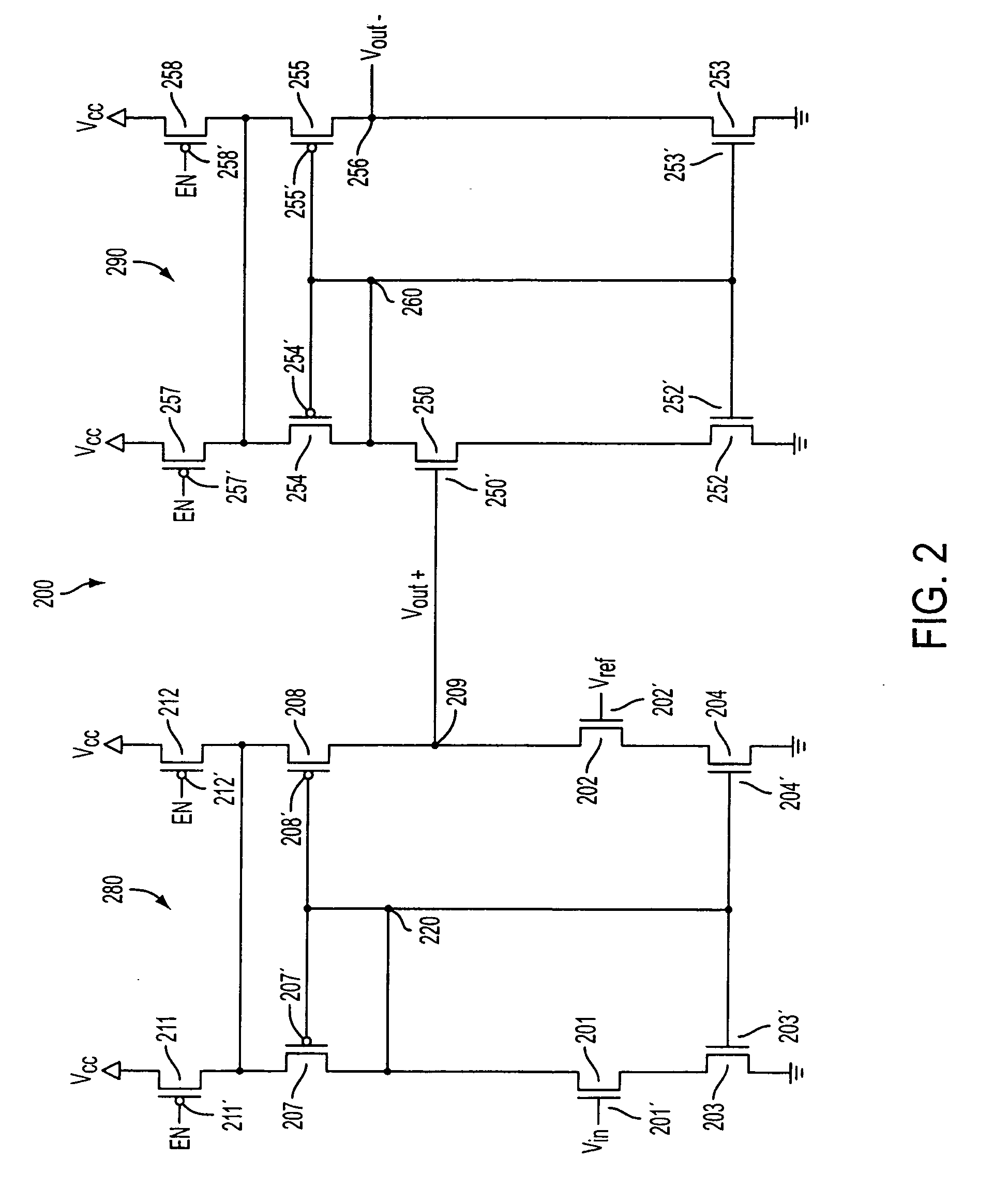

Input buffer design using common-mode feedback (CMFB)

ActiveUS20070046373A1Differential amplifiersDc-amplifiers with dc-coupled stagesEngineeringFeedback circuits

An input buffer includes a first stage for receiving an input signal and having a first pair of complementary output signals, the first stage including an input circuit for receiving the input signal, an output circuit for generating the first pair of complementary output signals based on the input signal, a resistance feedback circuit connected to the first pair of complementary output signals and generating a feedback signal, and a common mode circuit for balancing the complementary outputs based on the feedback signal.

Owner:MICRON TECH INC

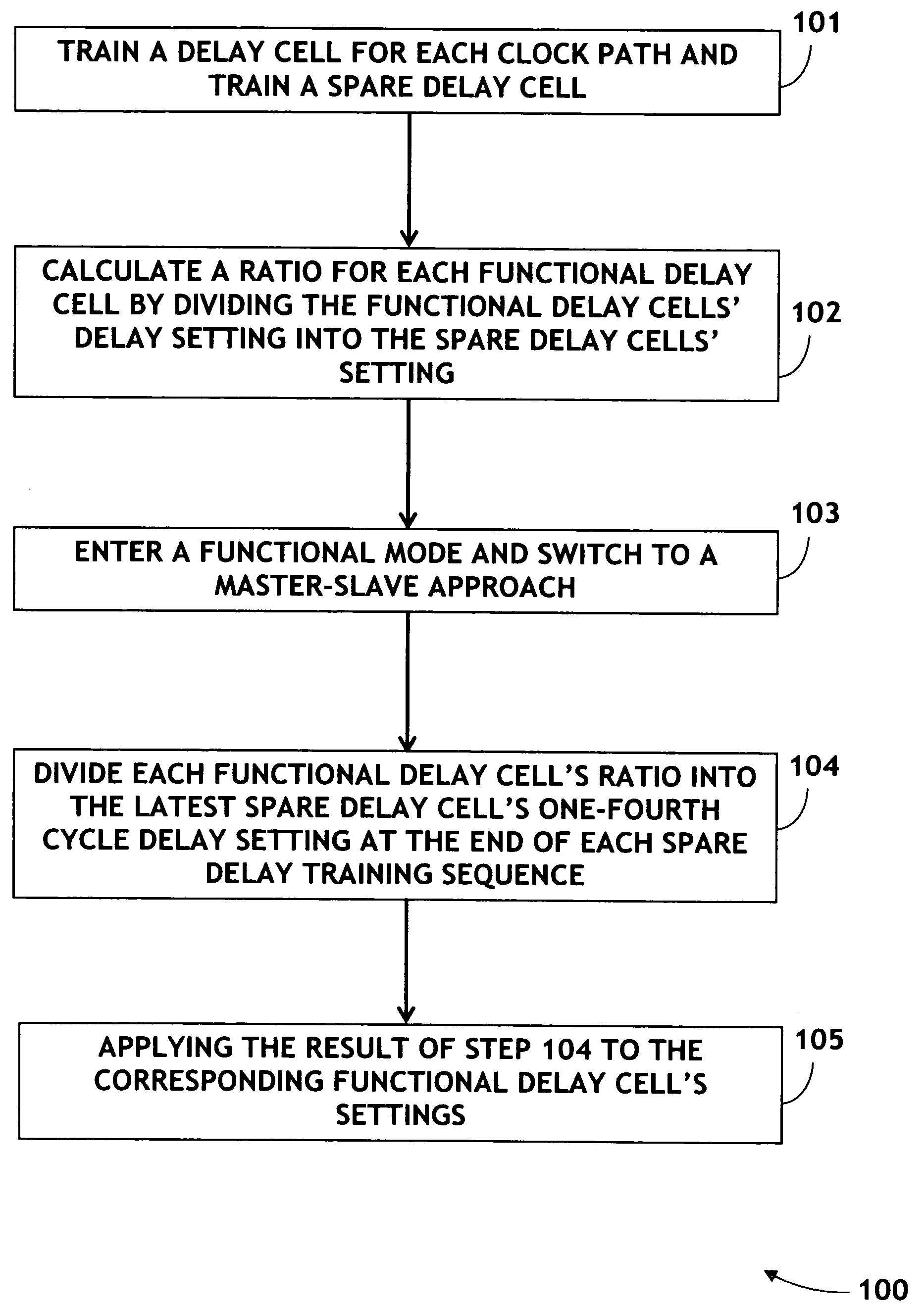

System and method for compensating for PVT variation effects on the delay line of a clock signal

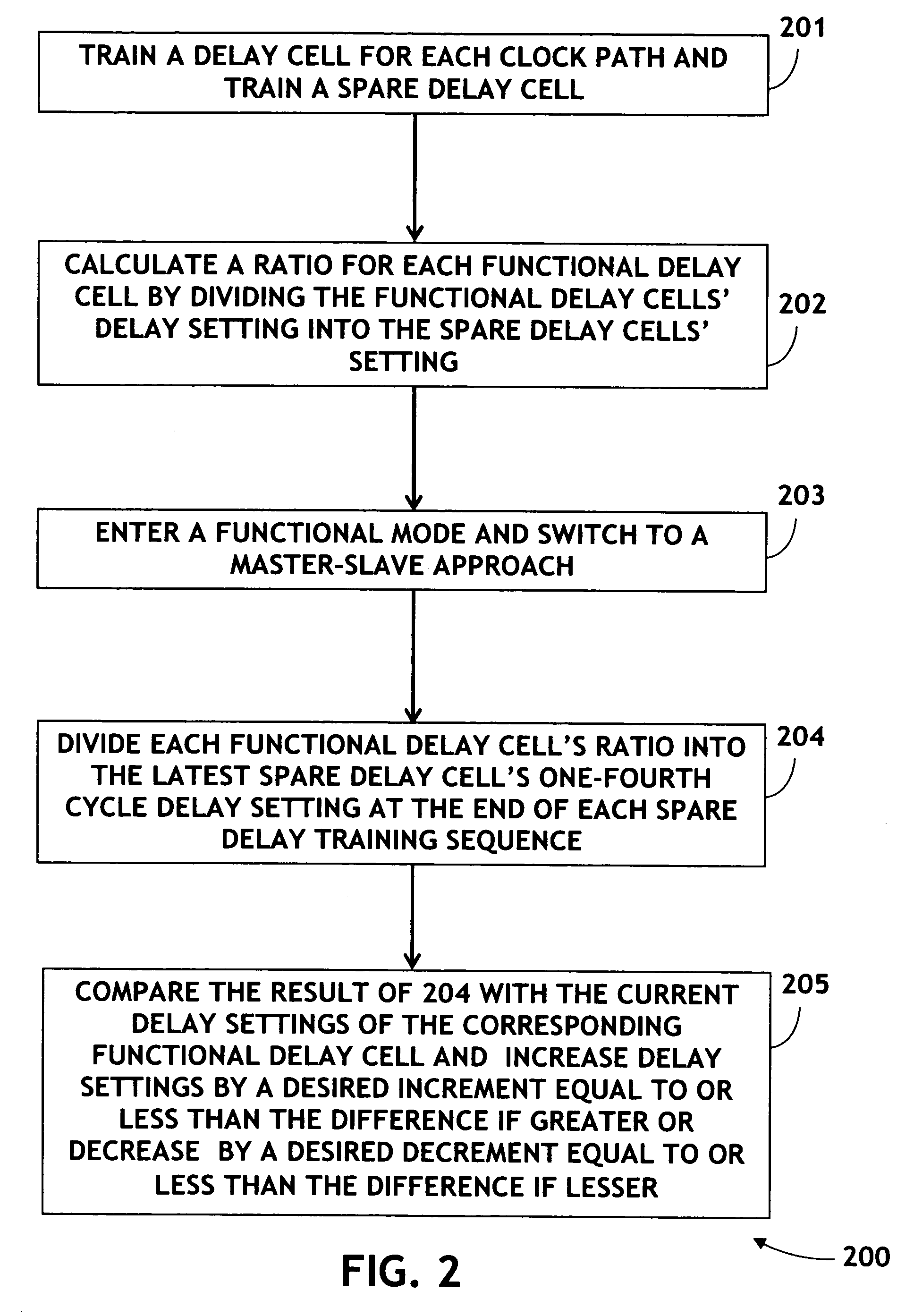

The present invention is directed to a method for compensating for process, voltage, and temperature variation without complex online / offline swapping of data paths requiring a dedicated FIFO(First-in First-out) buffer design. Delay cells are trained for each clock path (namely a Functional delay) and a spare delay cell is trained. A ratio is calculated for each Functional delay cell by dividing the Functional delay cells' setting into the spare delay cells' one-fourth cycle setting. These ratios reflect any process variation. Functional mode is then entered and a Master-Slave approach switched to, during which the spare delay cell repeats the training sequence continuously while the Functional delay cells delay the clocks from the RAM(Random Access Memory). Each Functional delay cell is updated at the end of each training sequence of the spare delay cell, compensating for voltage and temperature change, by dividing the ratio into the new spare delay cell one-fourth cycle setting.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

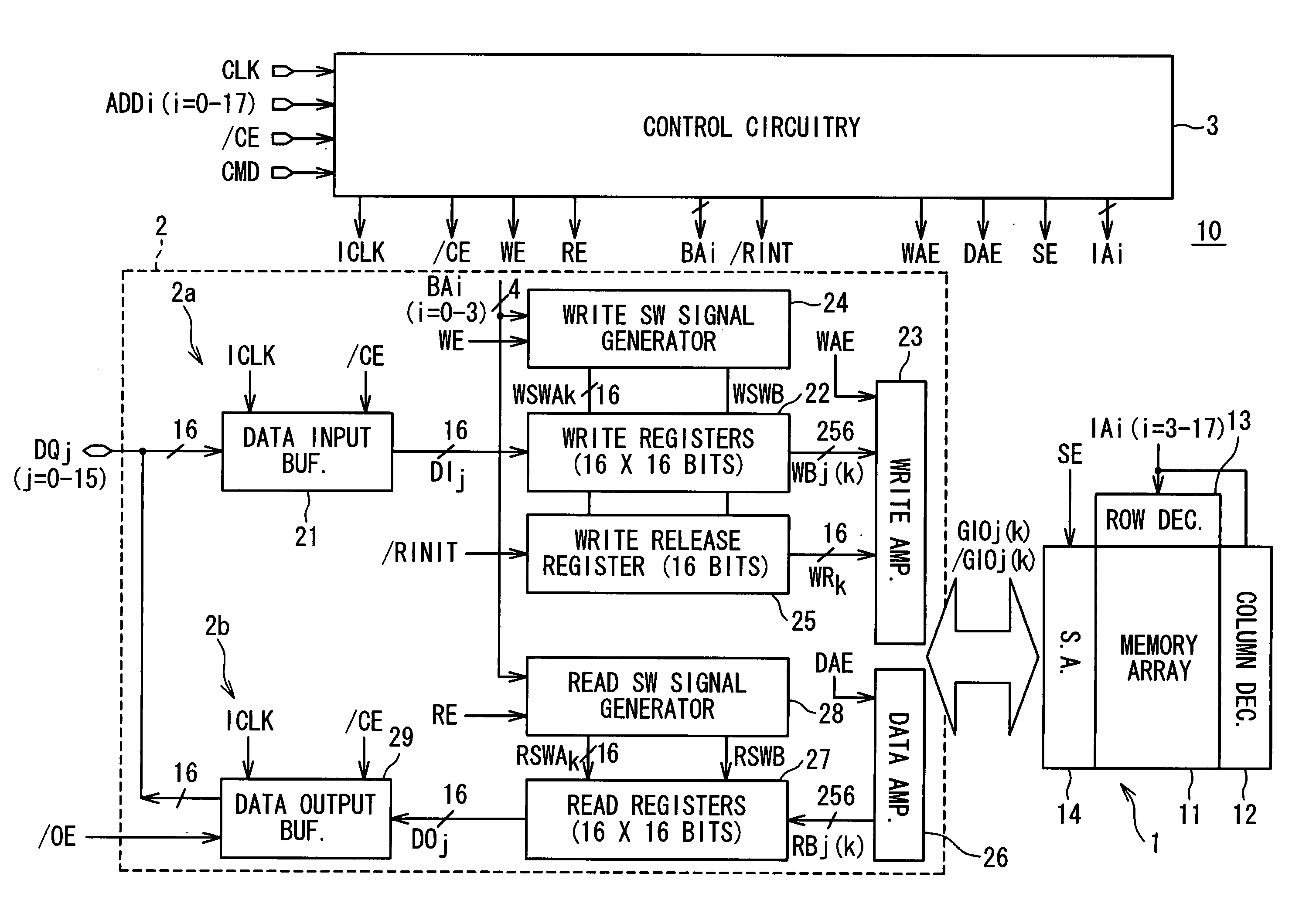

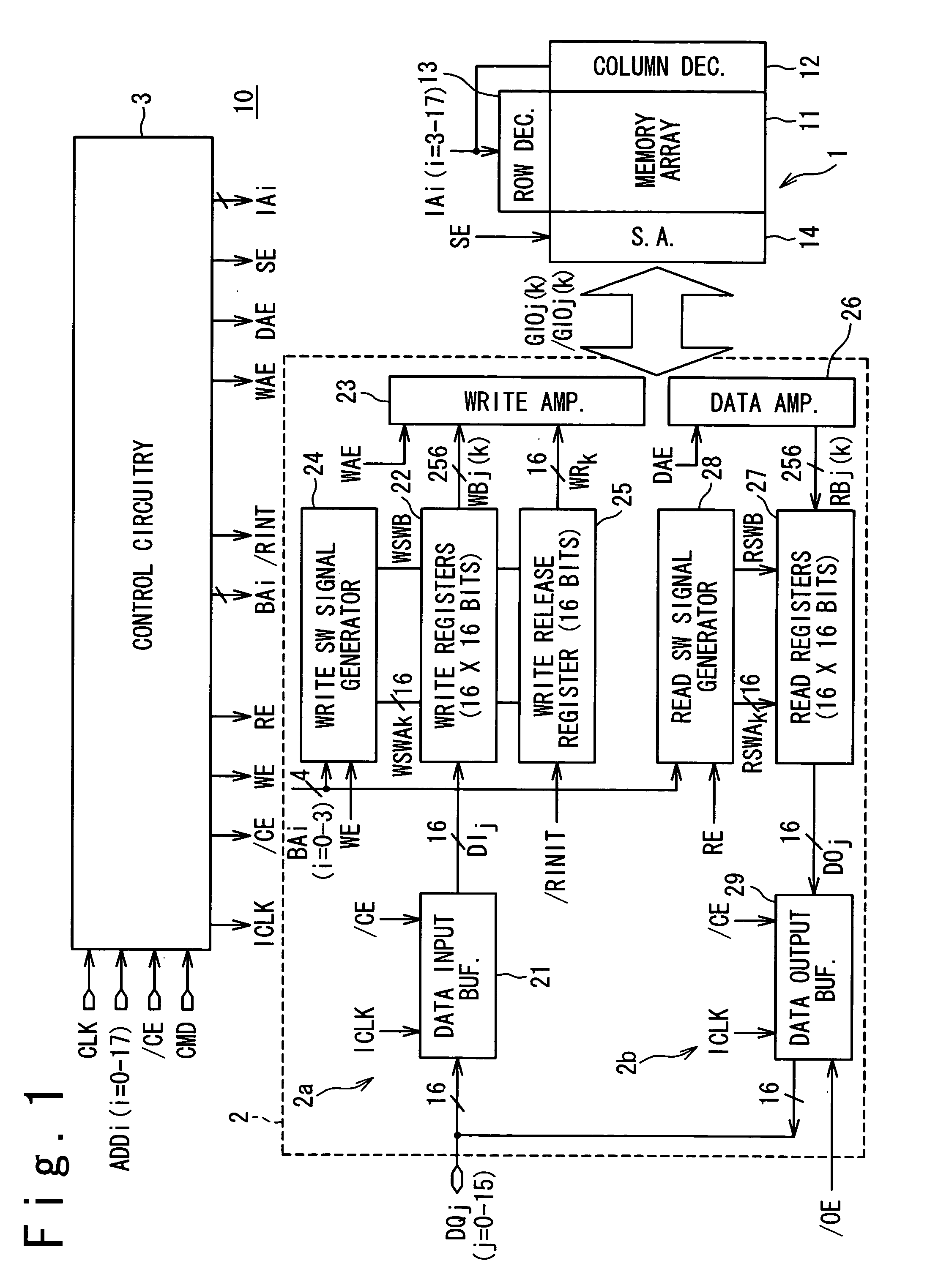

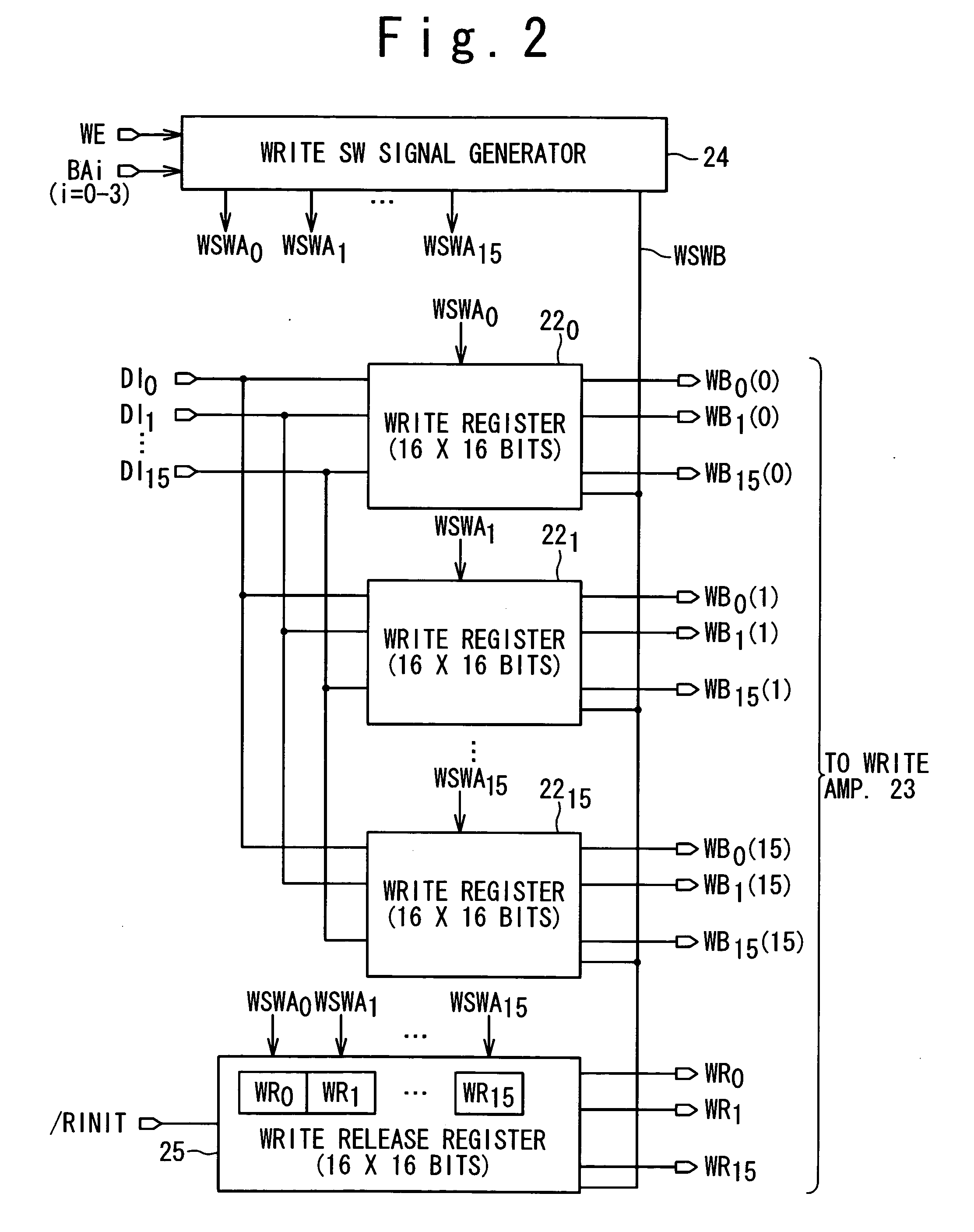

Semiconductor memory device and operating method of the same

InactiveUS20050265088A1Increase flexibilityDigital storageMemory systemsAudio power amplifierBurst transmission

A semiconductor memory device adapted to burst transmission is provided for improving flexibility of data write operation. The semiconductor memory device is composed of: a memory array; a set of write registers; an input buffer designed to sequentially receive a series of write data during a burst cycle, and to write said write data into associated ones of said write registers; a write release register containing a set of write release flags associated with said write registers, respectively; a write release register controller asserting associated ones of said write release flags in response to said write data being written into said associated ones of said write registers; and a write amplifier designed to concurrently write said write data contained in said write registers associated with asserted ones of said write release flags, selectively, when said burst cycle is aborted in response to a control signal.

Owner:RENESAS ELECTRONICS CORP

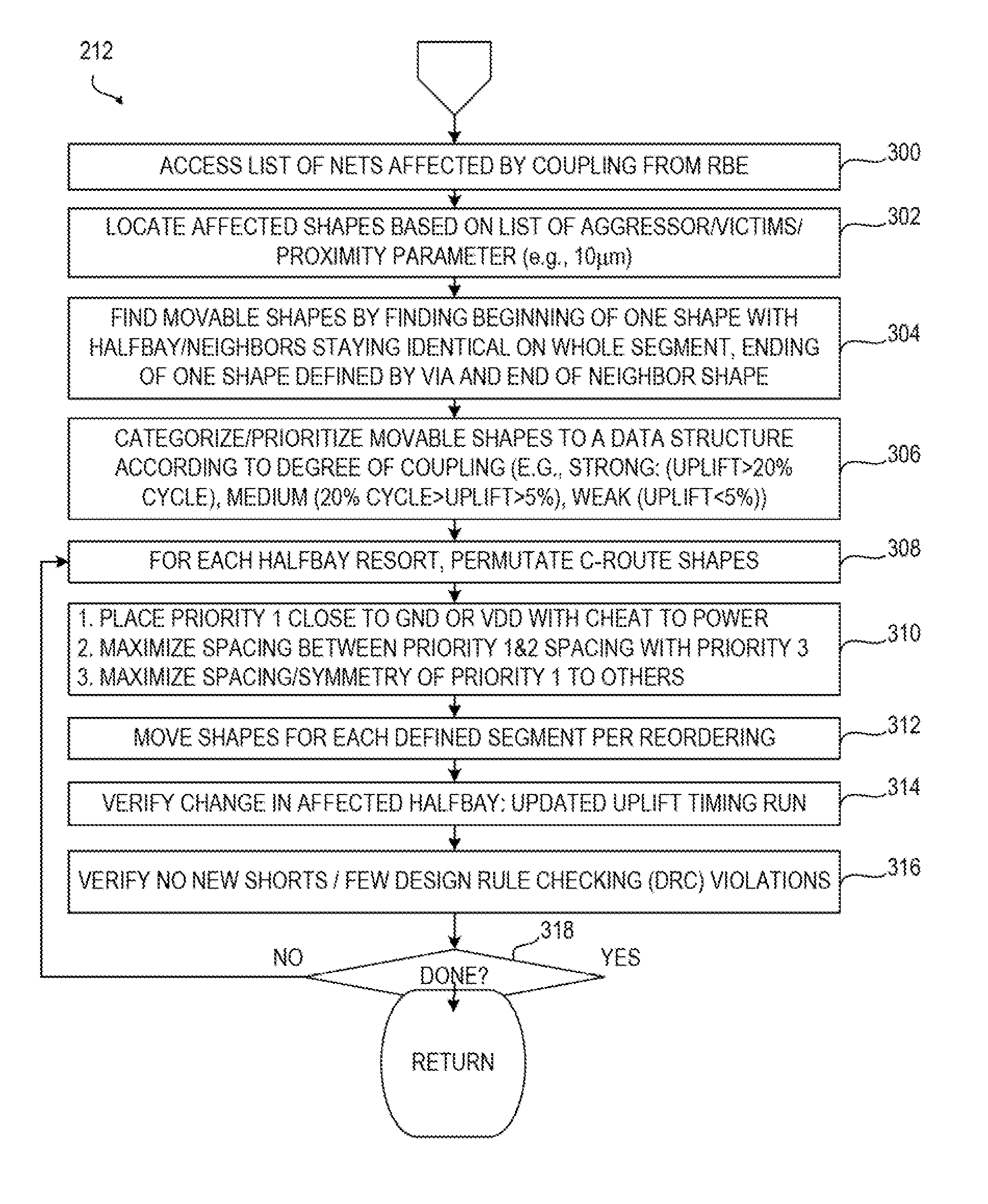

Early noise detection and noise aware routing in circuit design

InactiveUS20130047130A1Reduce noiseComputer programmed simultaneously with data introductionComputer aided designData processing systemCritical level

A computerized method, data processing system and computer program product reduce noise for a buffered design of an electronic circuit which was already placed and routed. For all areas between a power stripe and a ground stripe (half bay) in the design, the shapes are divided in different criticality levels. The shapes are rearranged based on their criticality level such that shapes with higher criticality level are placed closer to the stripes than those with lower criticality level.

Owner:GLOBALFOUNDRIES INC

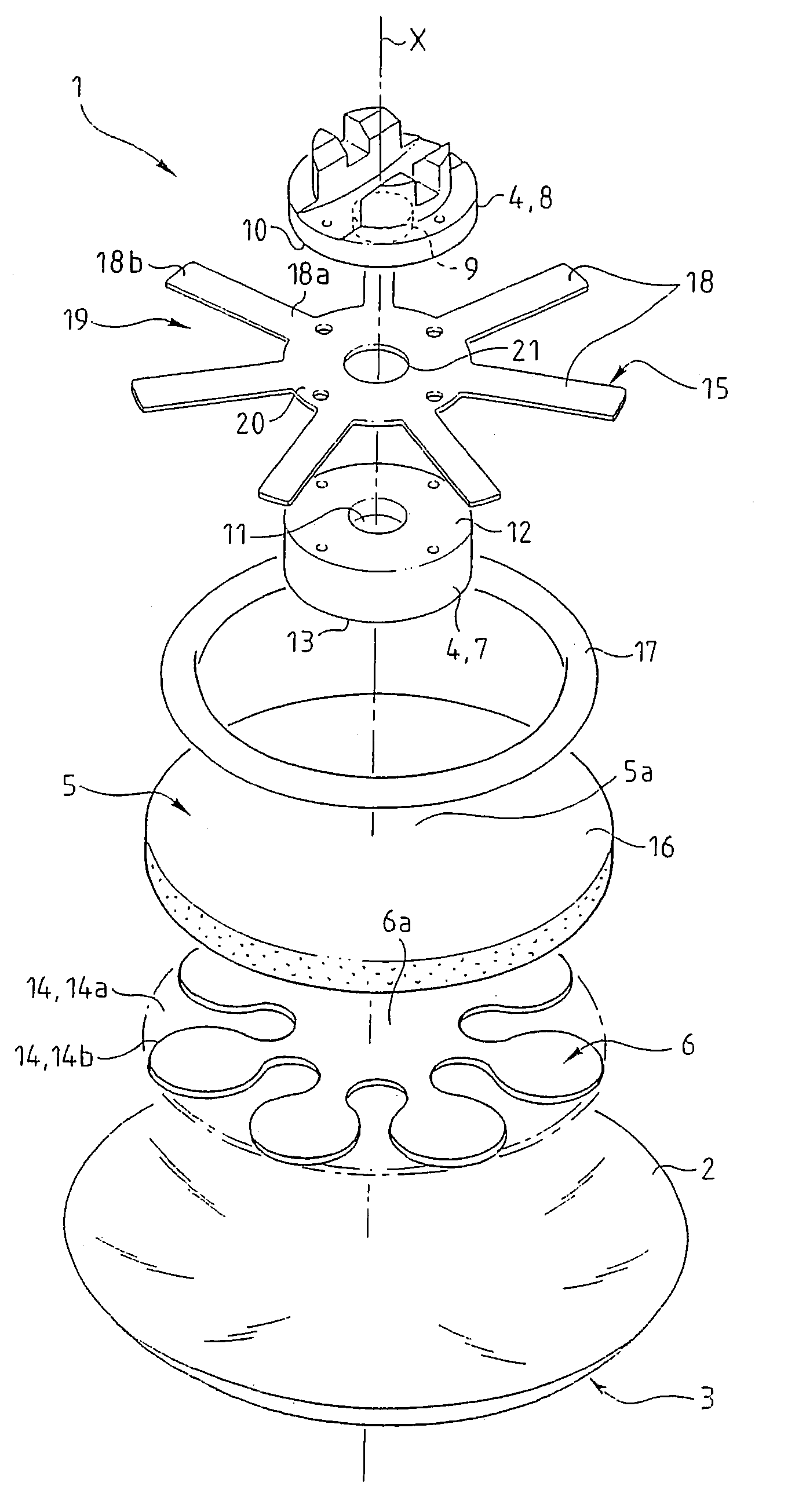

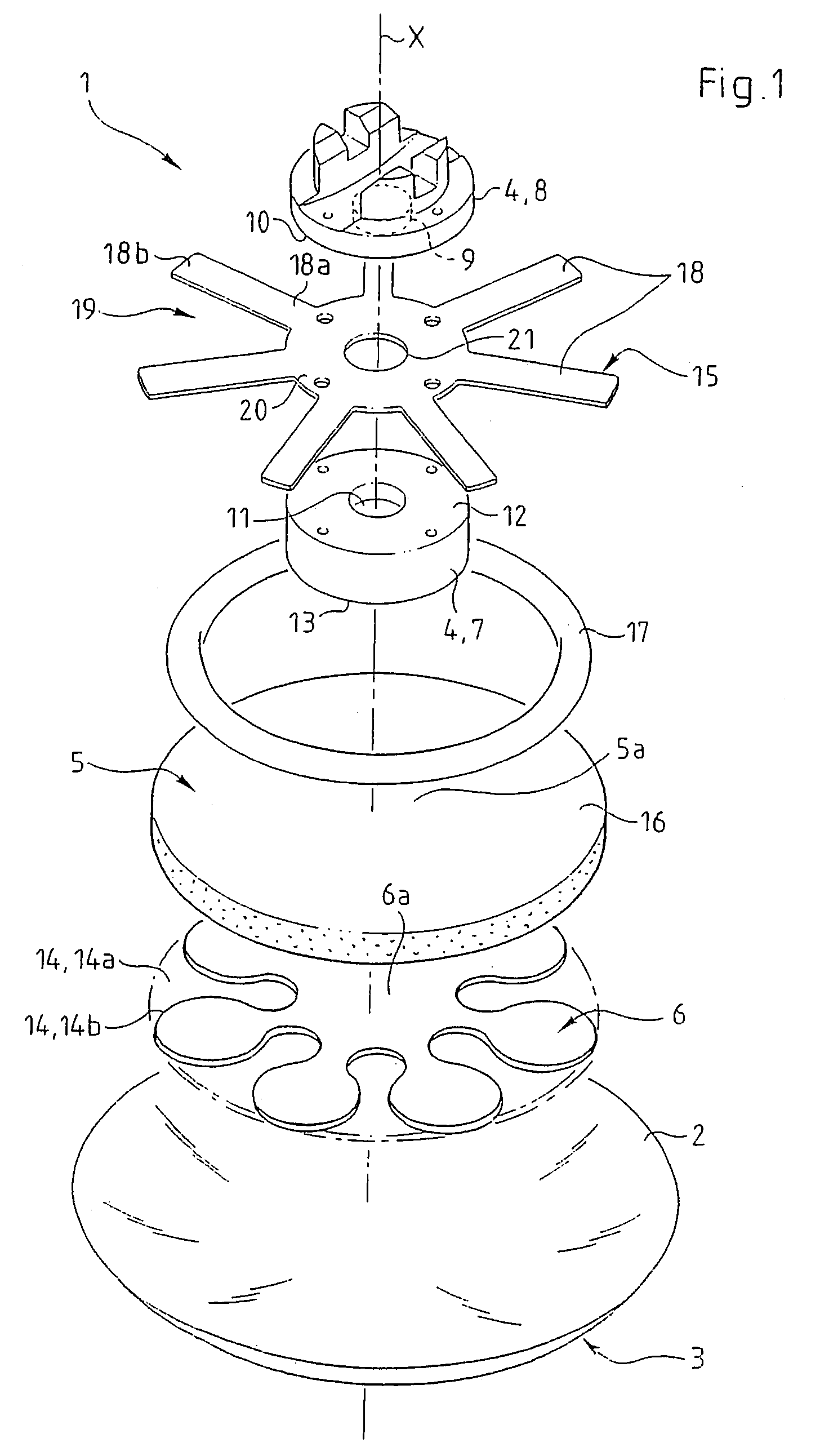

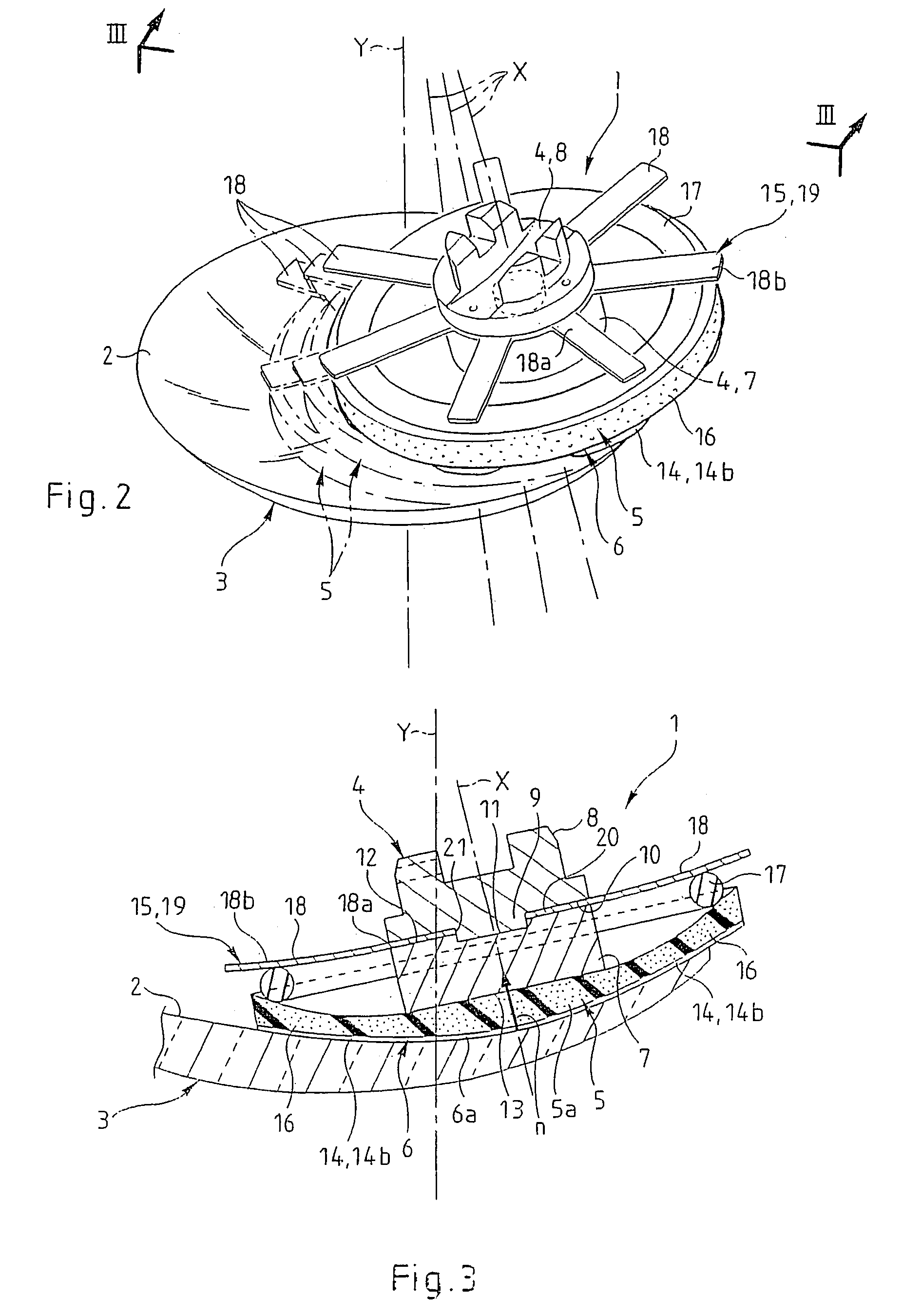

Tool for surface treatment of an optical surface

InactiveUS7033261B2Surface stabilizationReliable and fast surfacingEdge grinding machinesOptical surface grinding machinesEngineeringOptical surface

A tool for surface treatment of an optical surface, includes a rigid support having a transverse end surface, an elastically compressible interface which is applied against and overlaps the end surface, and a soft buffer designed to be applied against the optical surface and which is pressed against and overlaps at least partly the interface opposite and perpendicular to the end surface. The buffer includes a so-called central part which is located between the end surface and a so-called peripheral part which is located transversely beyond the end surface, elastic return elements connecting the peripheral part to the support.

Owner:ESSILOR INT CIE GEN DOPTIQUE

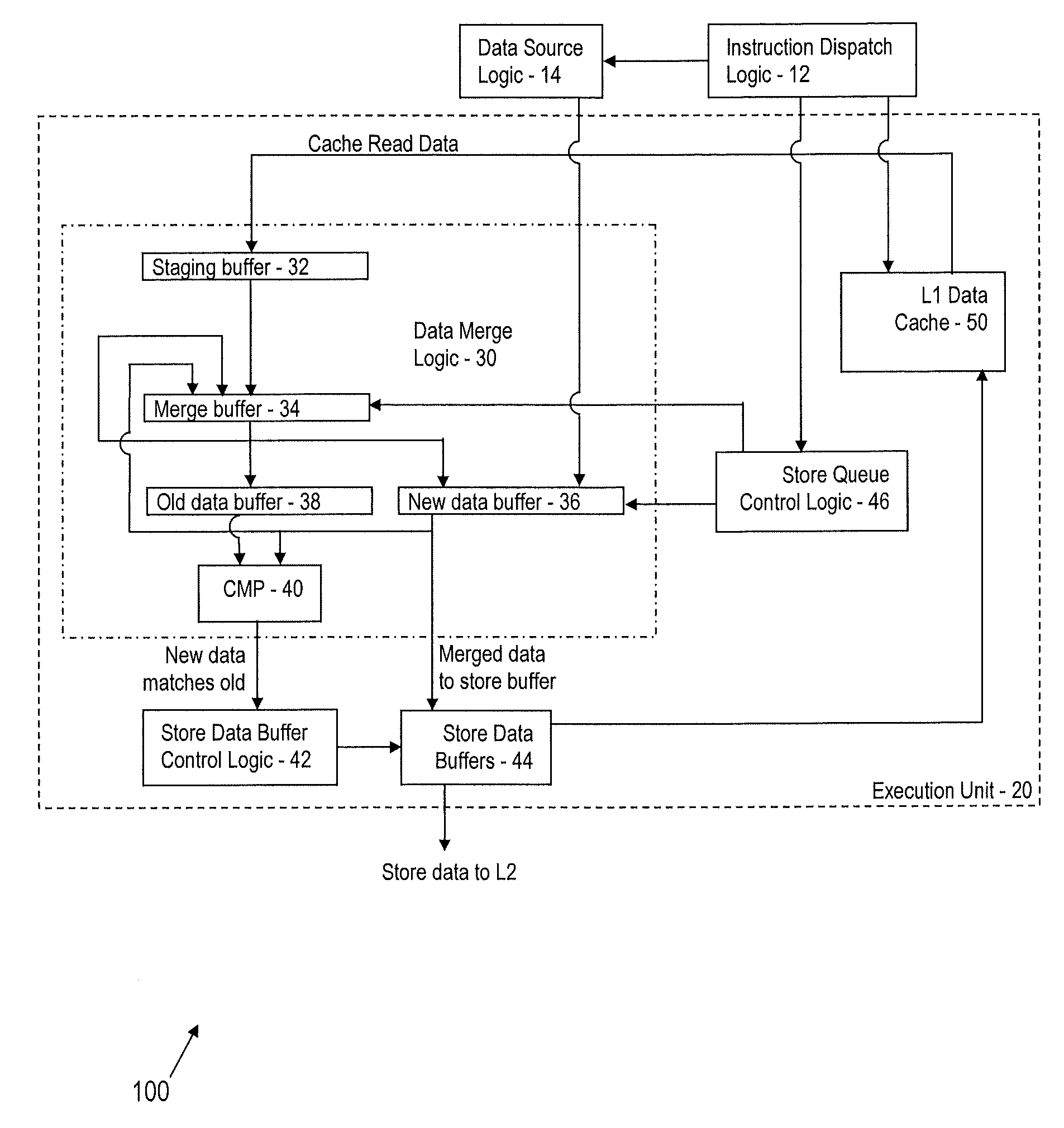

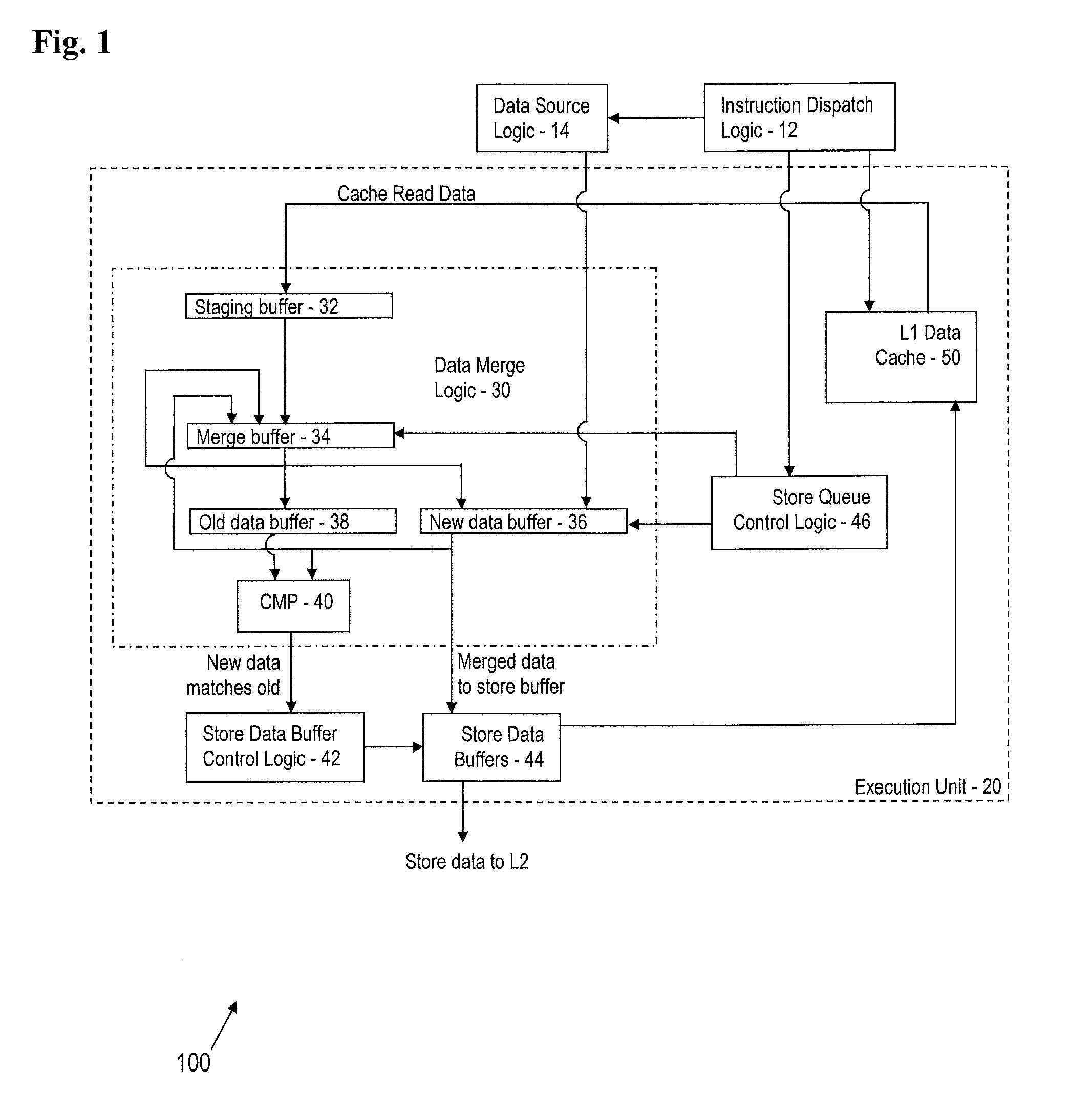

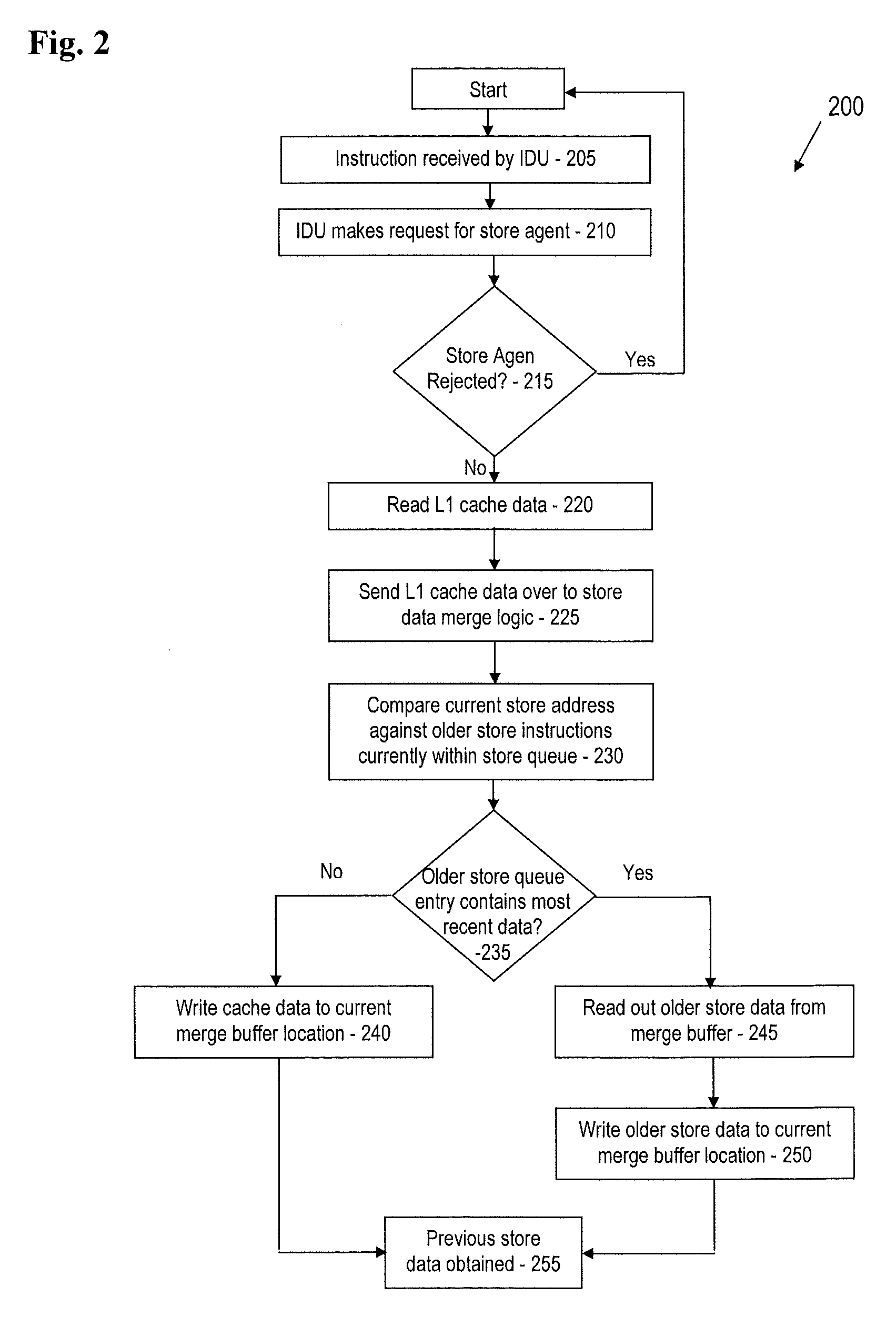

Processor, method and computer program product including specialized store queue and buffer design for silent store implementation

InactiveUS20090210655A1General purpose stored program computerProgram controlData controlData matching

A processor including an architecture for limiting store operations includes: a data input and a cache input as inputs to data merge logic; a merge buffer for providing an output to an old data buffer, holding a copy of a memory location and two way communication with a new data buffer; compare logic for receiving old data from the old data buffer and new data from the new data buffer and comparing if the old data matches the new data, and if there is a match determining an existence of a silent store; and store data control logic for limiting store operations while the silent store exists. A method and a computer program product are provided.

Owner:IBM CORP

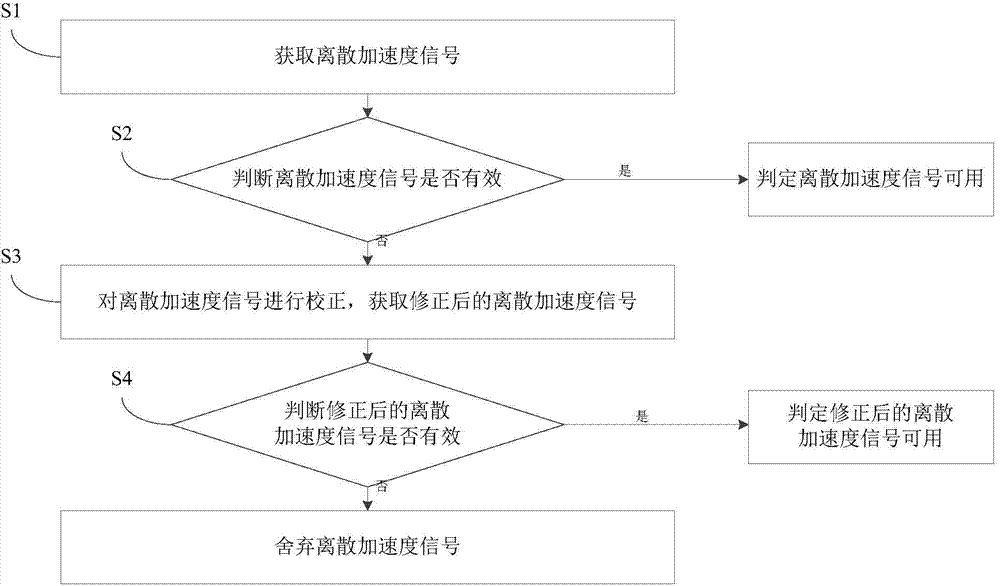

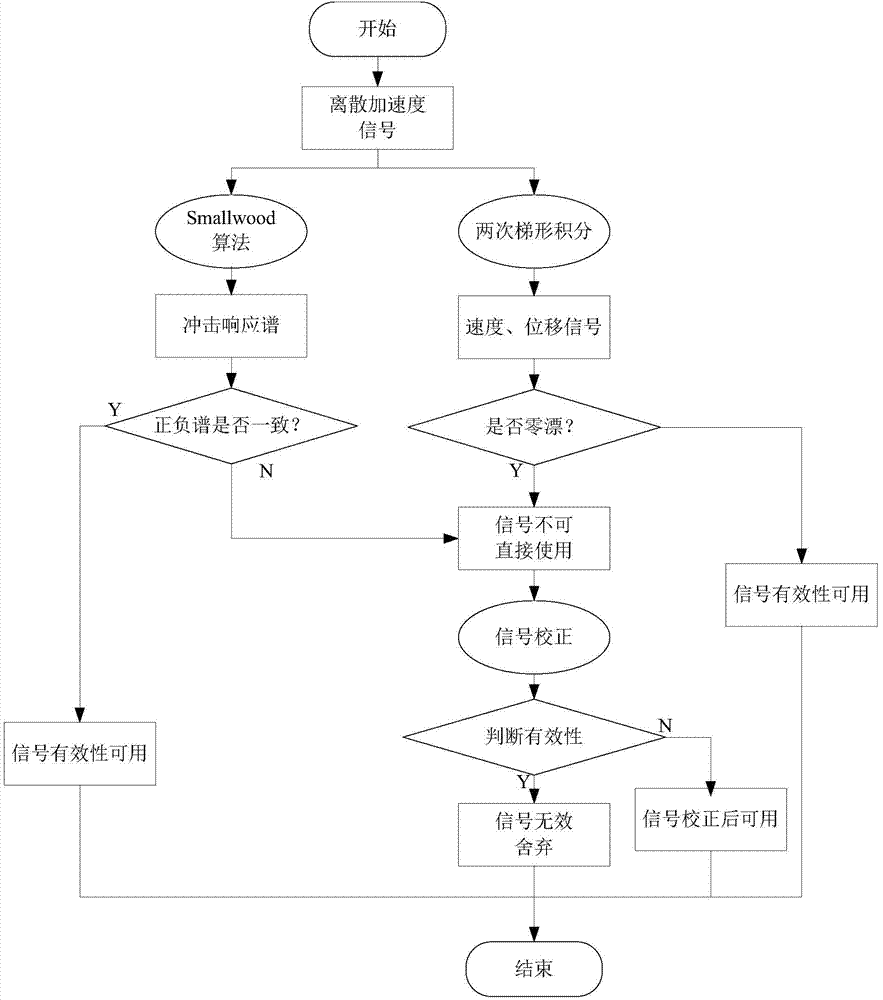

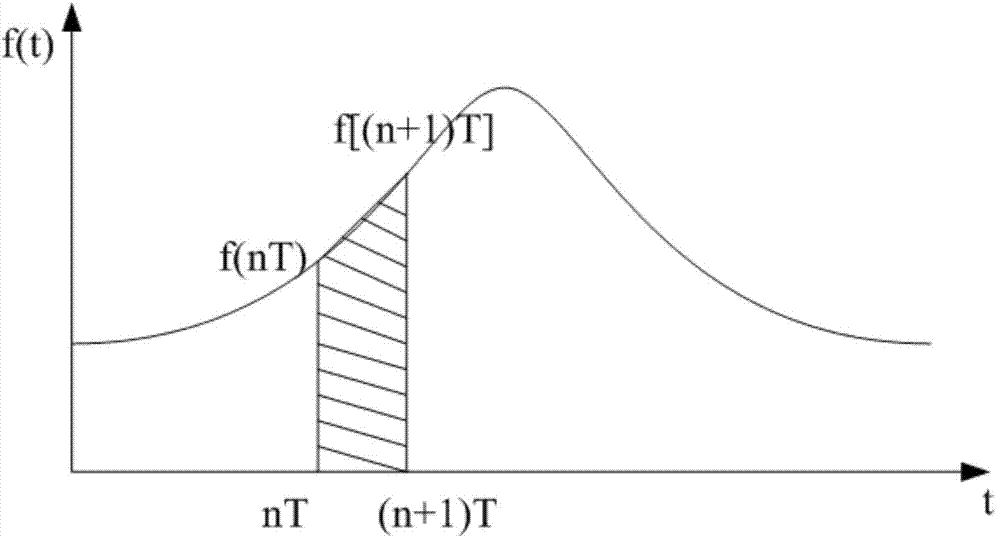

Fire work impact data preprocessing method and system

ActiveCN104778360AImprove accuracyIncrease authenticitySpecial data processing applicationsPretreatment methodComputer science

The invention discloses a fire work impact data preprocessing method which comprises the following steps: S1, acquiring a discrete acceleration signal; S2, judging whether the discrete acceleration signal is effective, deciding the discrete acceleration signal is available if yes, or executing the step S3; S3, correcting the discrete acceleration signal and acquiring a corrected discrete acceleration signal; S4, further judging whether the corrected discrete acceleration signal is effective, deciding the corrected discrete acceleration signal is available if yes, or abandoning the discrete acceleration signal. According to the method disclosed by the invention, correctness and truth of the fire work impact signal can be improved; the method has strong engineering background and has great referential significance for reducing the weight of an aircraft and making a buffer design and impact acceptance test standard. The invention also discloses a fire work impact data preprocessing system.

Owner:TSINGHUA UNIV

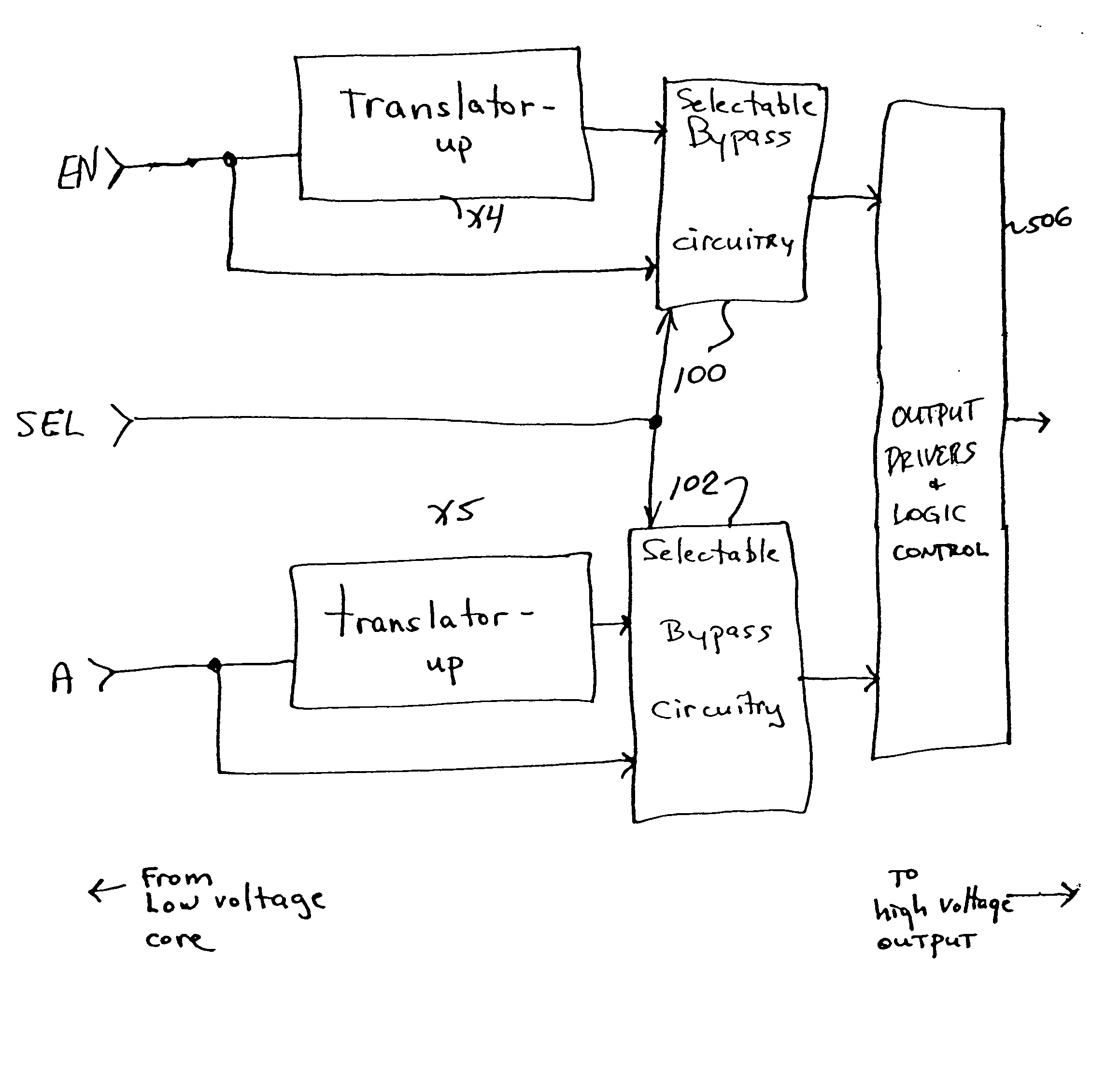

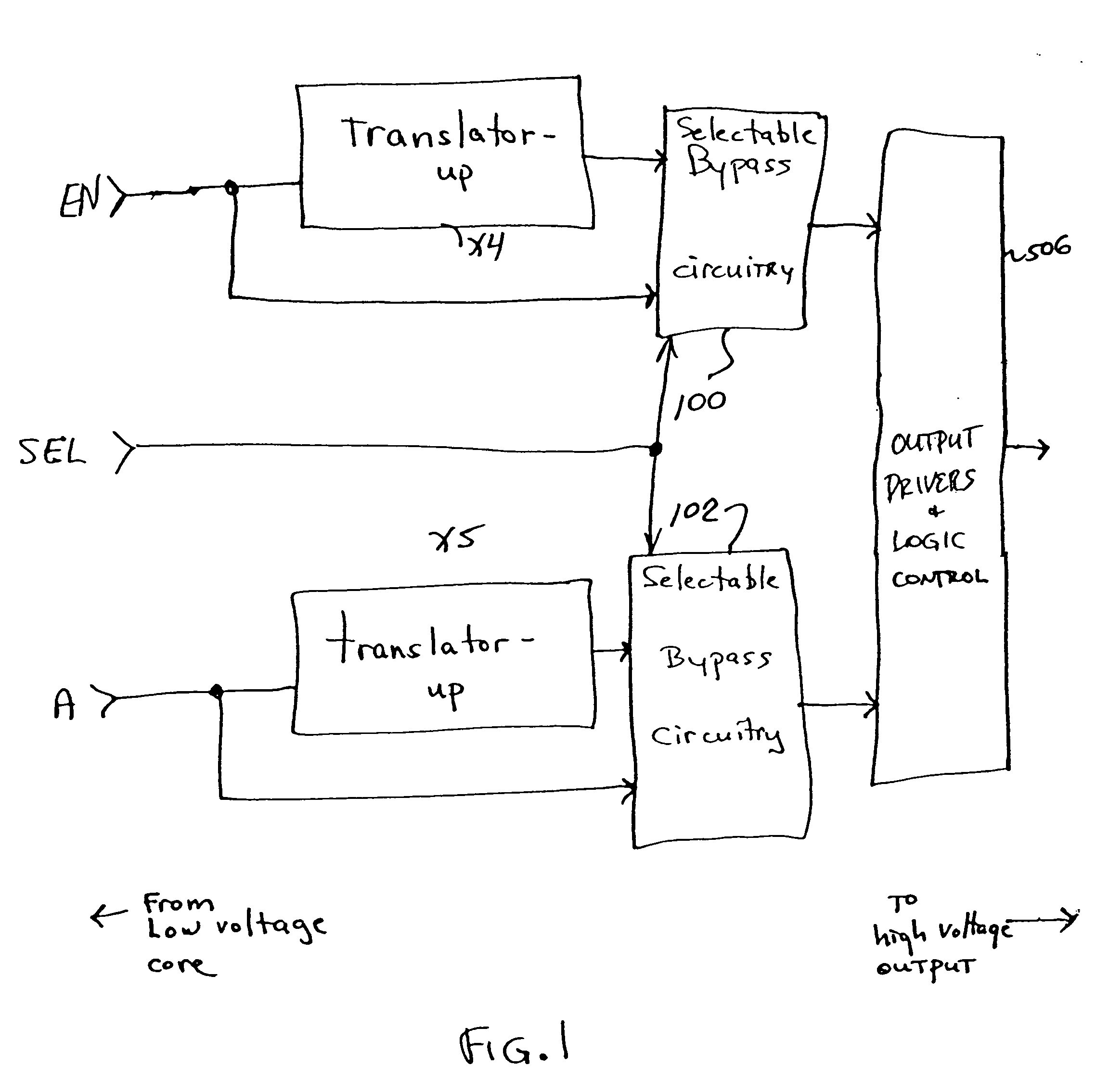

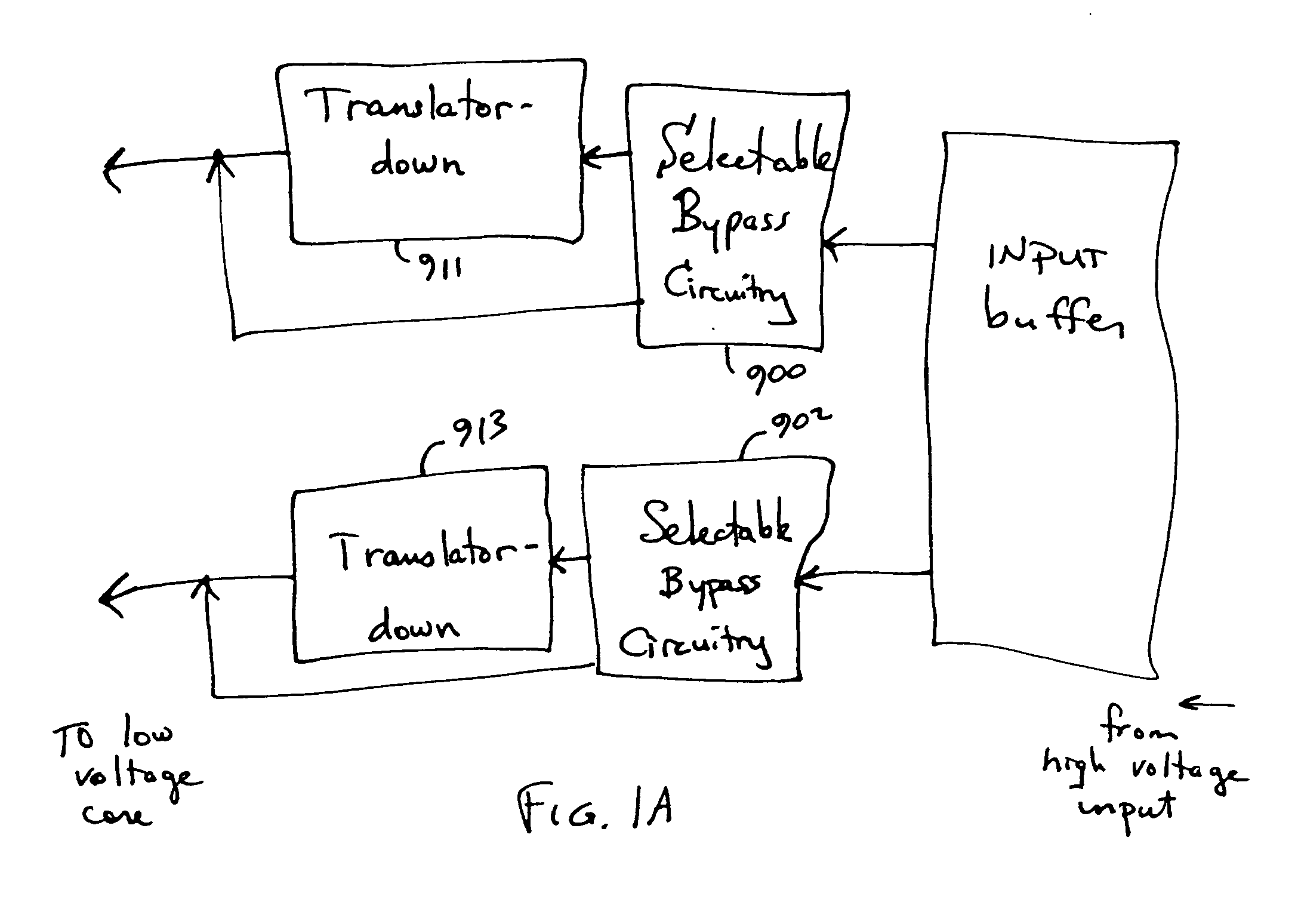

Coms buffer having higher and lower voltage operation

InactiveUS20050270065A1TransistorLogic circuits coupling/interface using field-effect transistorsLow voltageSnubber

A buffer design for an integrated circuit that not only recognizes, but improves upon the skew problem as described above that is particularly problematic in cases where the output buffer supply voltage is particularly close or the same as the voltage of the signals coming from the core of an IC. Translator-up circuits associated with output buffers are implemented in parallel with respective selective bypass circuits, allowing the translator-up circuit to be inserted into or removed from a signal path based on the voltage level of a signal received from the inner core and the voltage level required by the output buffer. When the voltage level of the “higher” voltage side is equal to the “lower” voltage signal level, the translator-up circuits are bypassed through selection by a selective bypass circuit. Thus, a selective bypass circuit is implemented together with a translator-up circuit to eliminate large signal skew, and to generally speed up circuit performance.

Owner:AGERE SYST INC

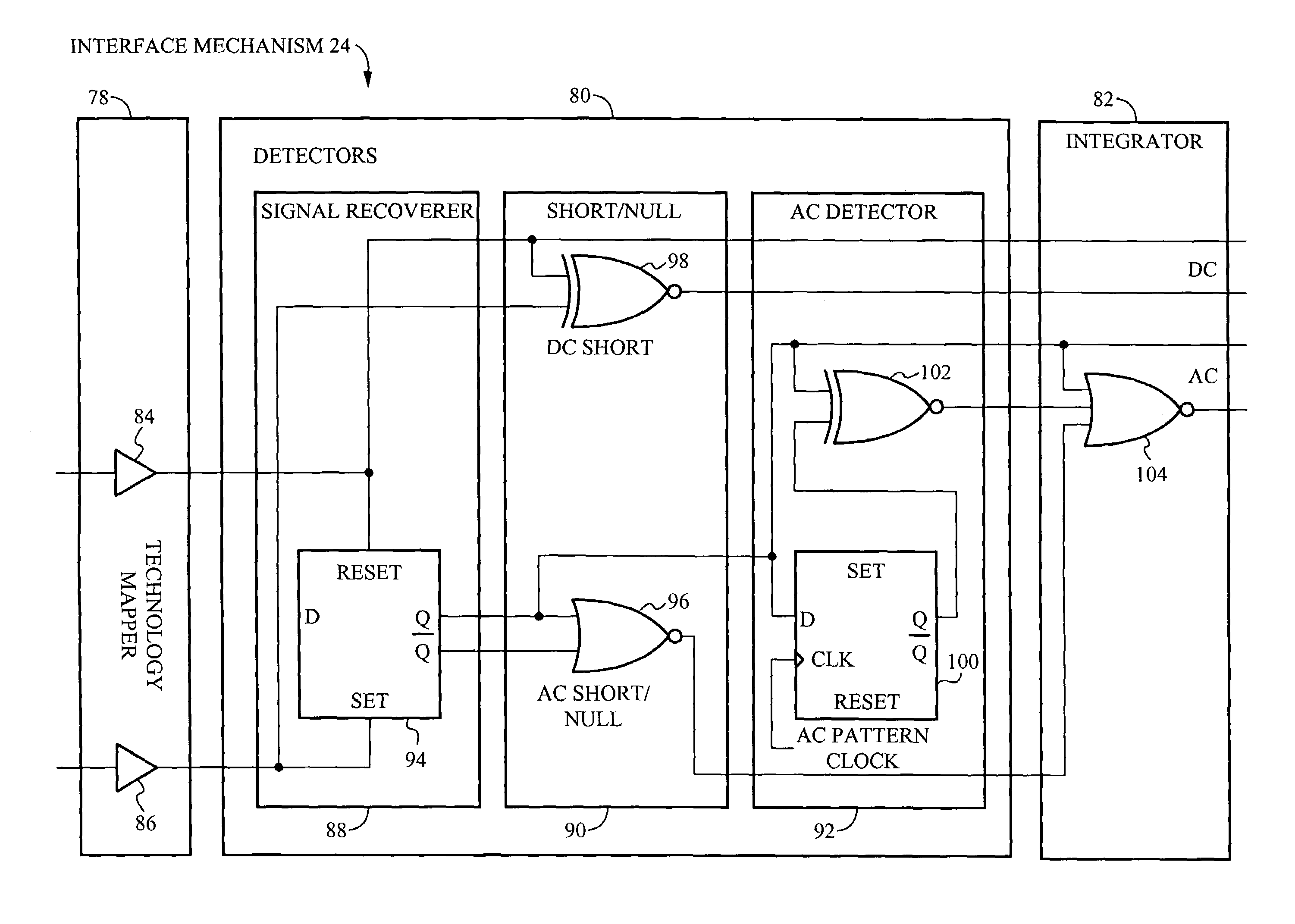

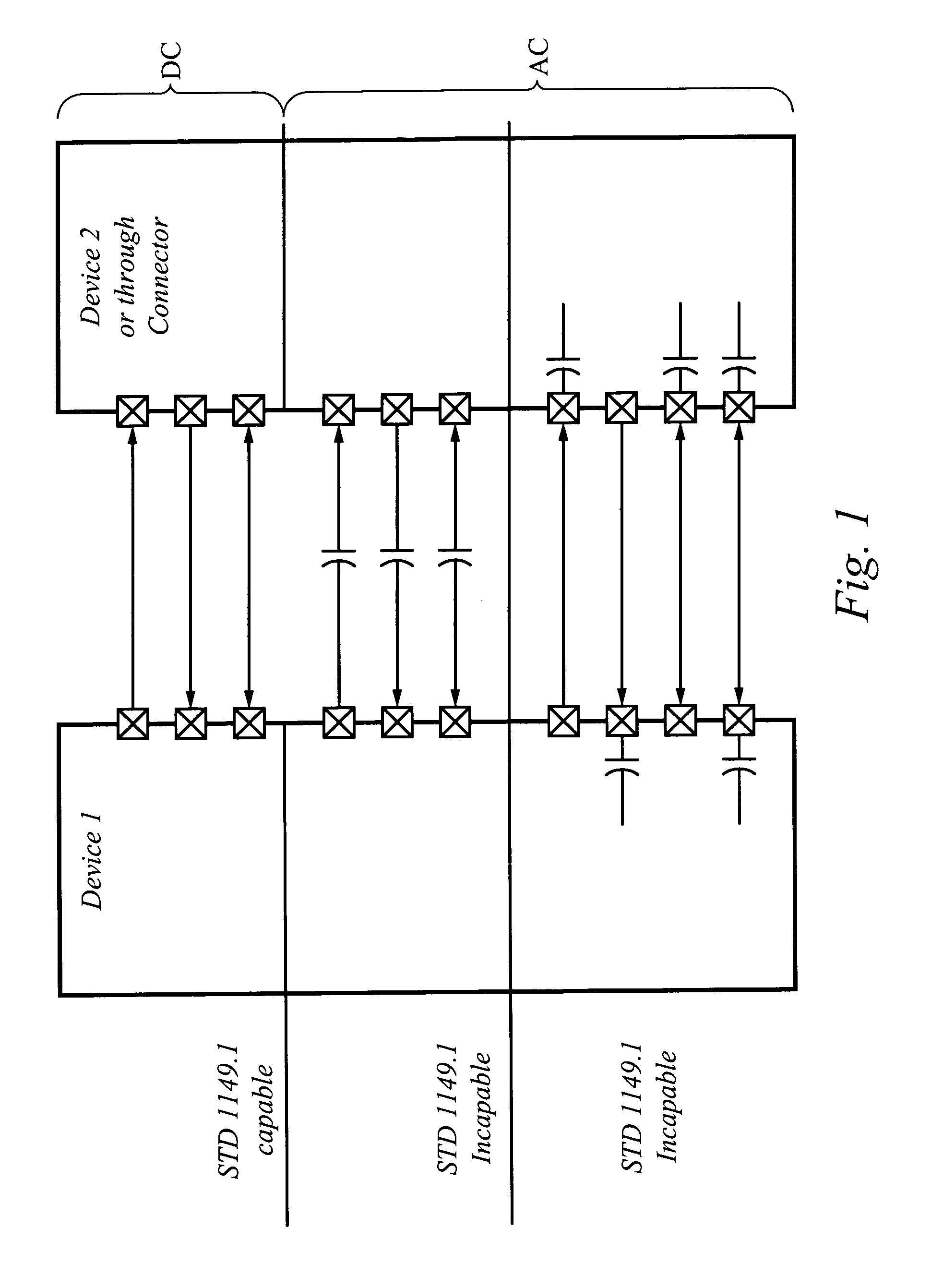

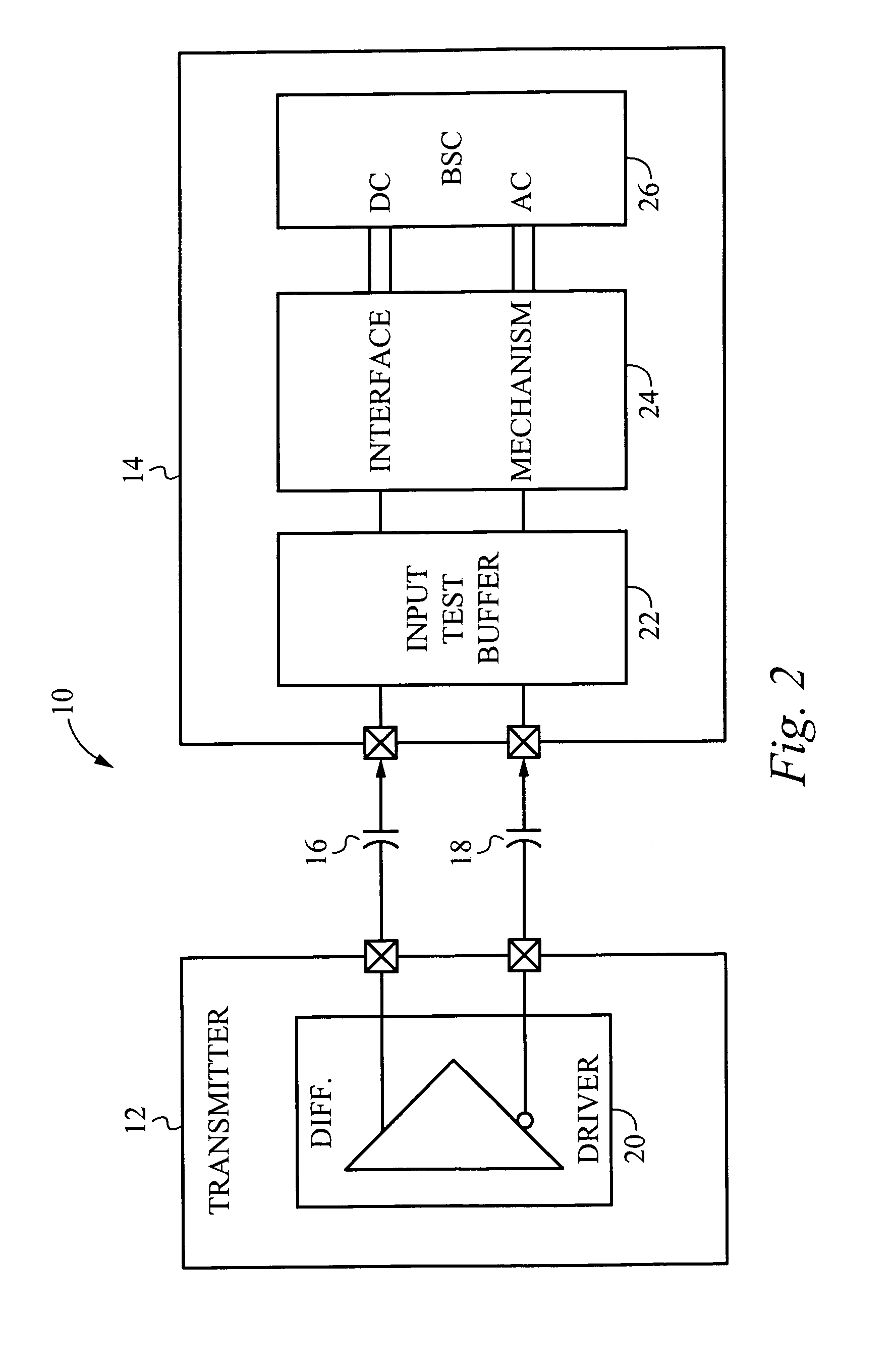

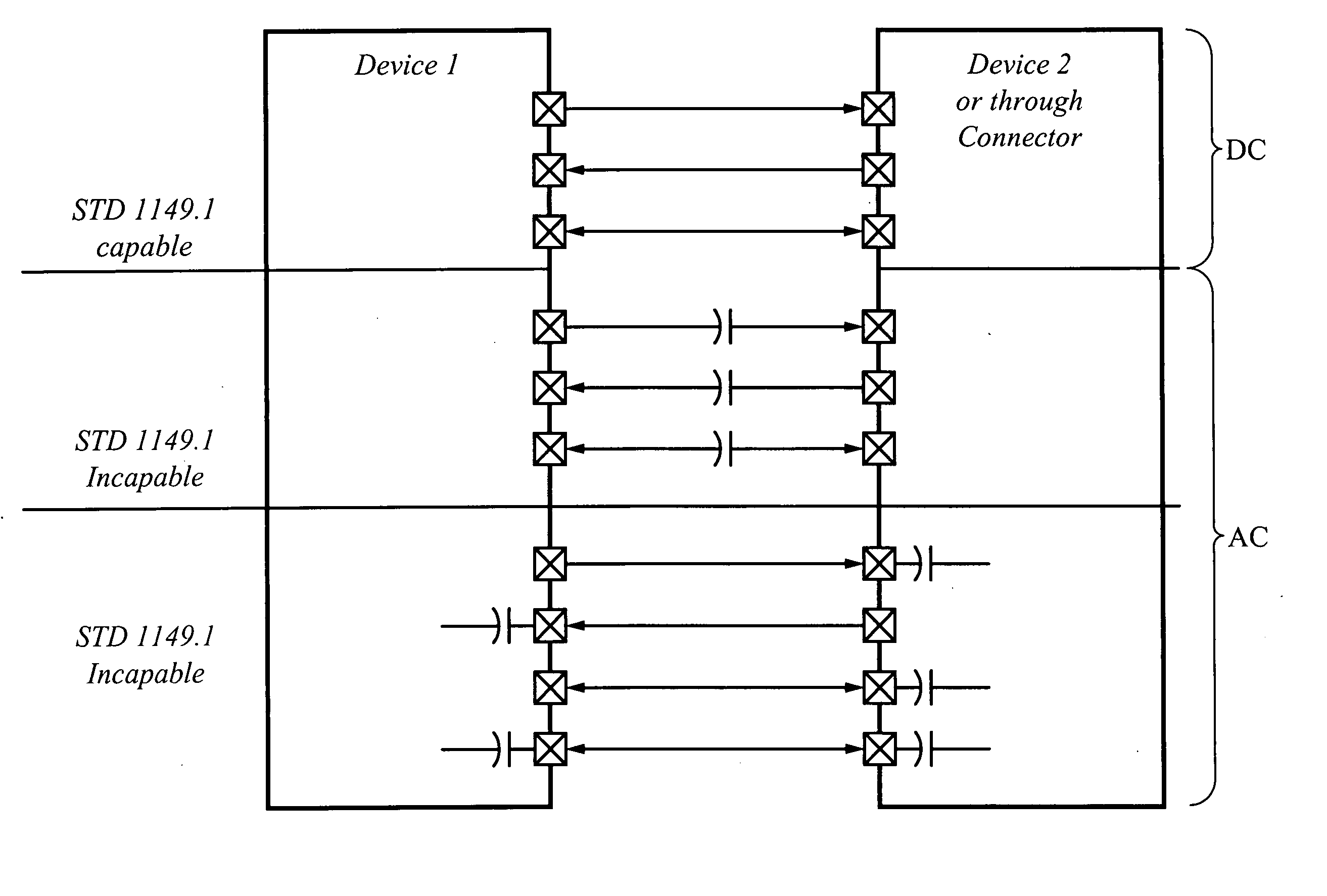

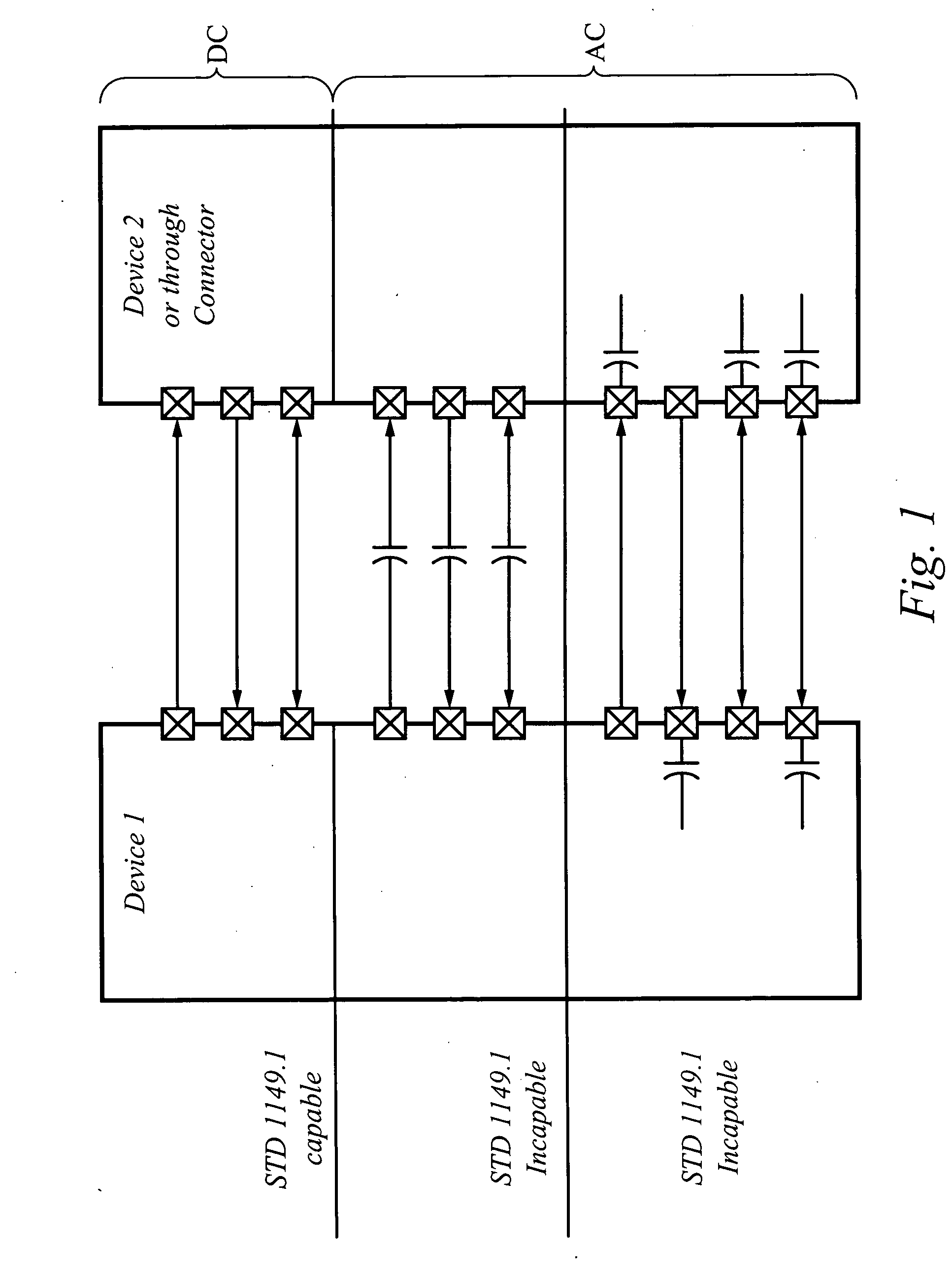

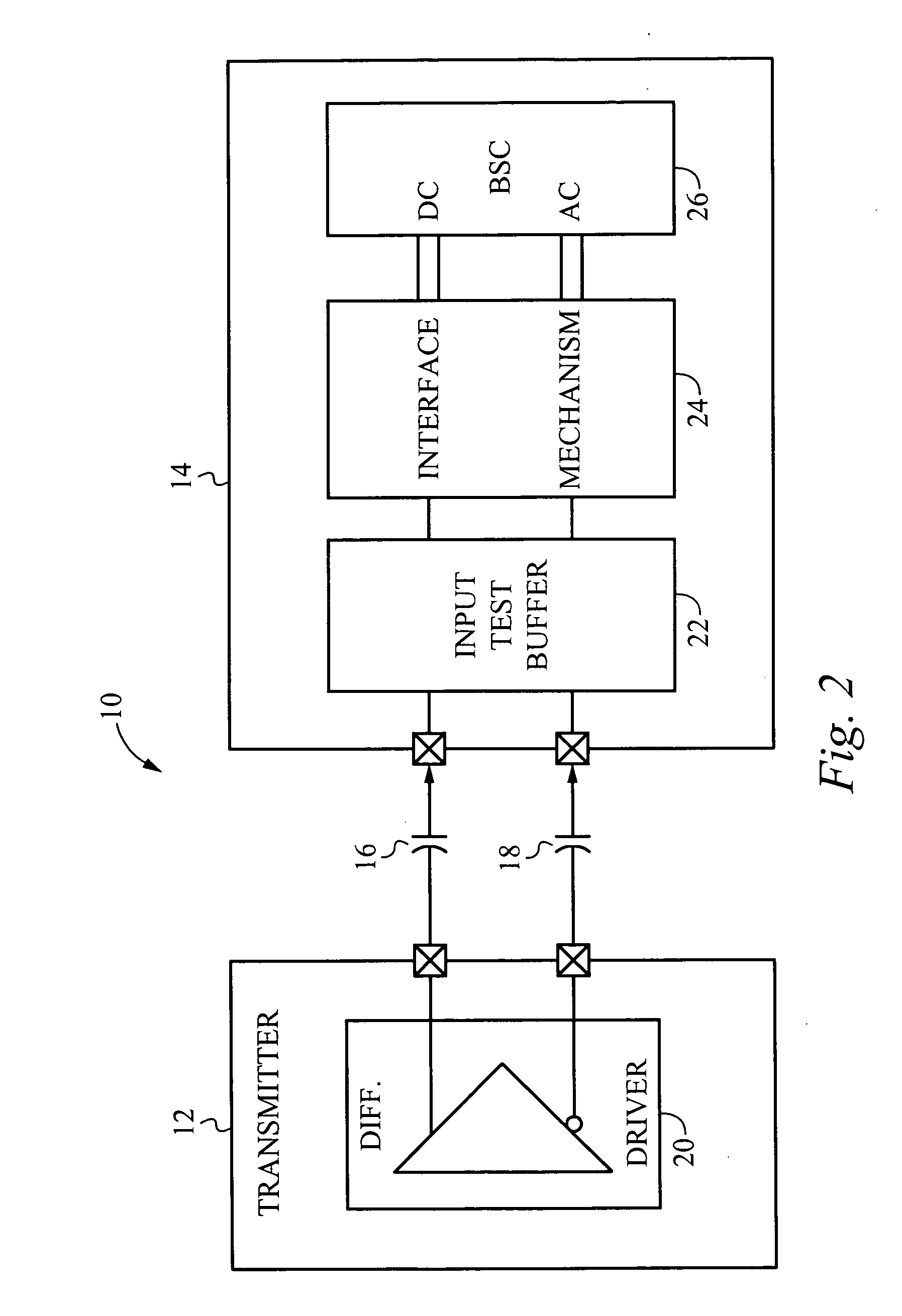

Test buffer design and interface mechanism for differential receiver AC/DC boundary scan test

A boundary scan test system including a transmitter and a receiver. The system performs DC and AC boundary scan testing of the interconnections between devices. The system addresses fault masking that can occur during testing. Of concern are AC coupled interconnections while providing IEEE 1149.1 DC test compatibility. The test receiver includes an input test buffer and an interface mechanism. The input test buffer has a built-in null detection capability. The interface mechanism includes a technology mapper, one or more detectors, and an integrator. The receiver provides at least partial, if not complete, coverage for at least one of five fault syndromes that can result from single defect conditions in the system.

Owner:CISCO TECH INC

Test buffer design and interface mechanism for differential receiver AC/DC boundary scan test

A boundary scan test system including a transmitter and a receiver. The system performs DC and AC boundary scan testing of the interconnections between devices. The system addresses fault masking that can occur during testing. Of concern are AC coupled interconnections while providing IEEE 1149.1 DC test compatibility. The test receiver includes an input test buffer and an interface mechanism. The input test buffer has a built-in null detection capability. The interface mechanism includes a technology mapper, one or more detectors, and an integrator. The receiver provides at least partial, if not complete, coverage for at least one of five fault syndromes that can result from single defect conditions in the system.

Owner:CISCO TECH INC

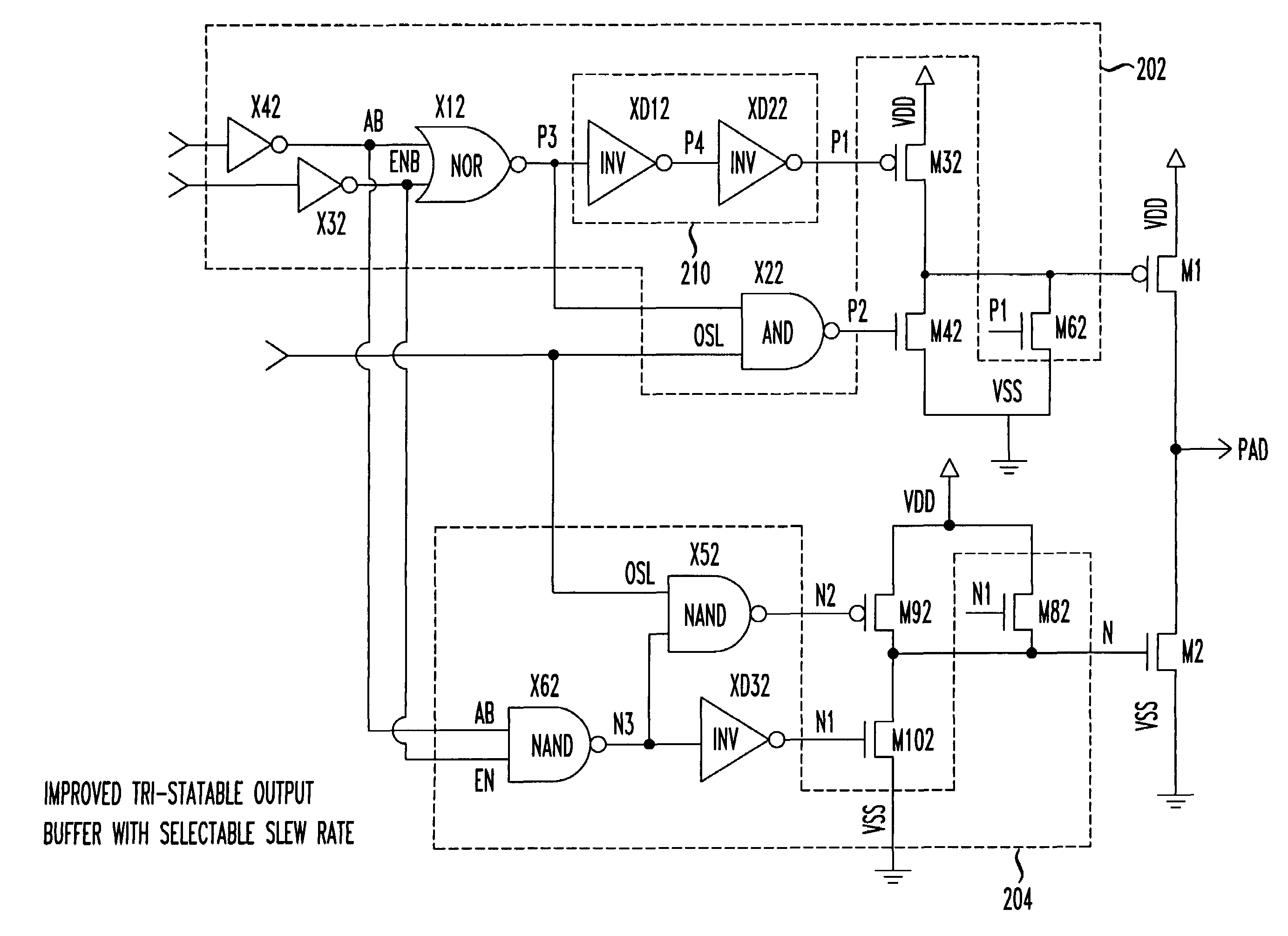

Output buffer with selectable slew rate

A buffer design for an integrated circuit that has adjustable slew rate control, yet requires significantly less space to fabricate than does a conventional buffer with slew rate control. A new slew rate control circuit design is added to a Complementary Metal Oxide Semiconductor CMOS buffer to implement slew rate control in the buffer (e.g., selection between a high slew rate and a low slew rate). The new slew rate control circuit requires significantly less space to fabricate, and when applied to each buffer in an given integrated circuit, e.g., input / output buffers that may be placed along the periphery of the integrated circuit, the savings can be extraordinary.

Owner:AVAGO TECH INT SALES PTE LTD

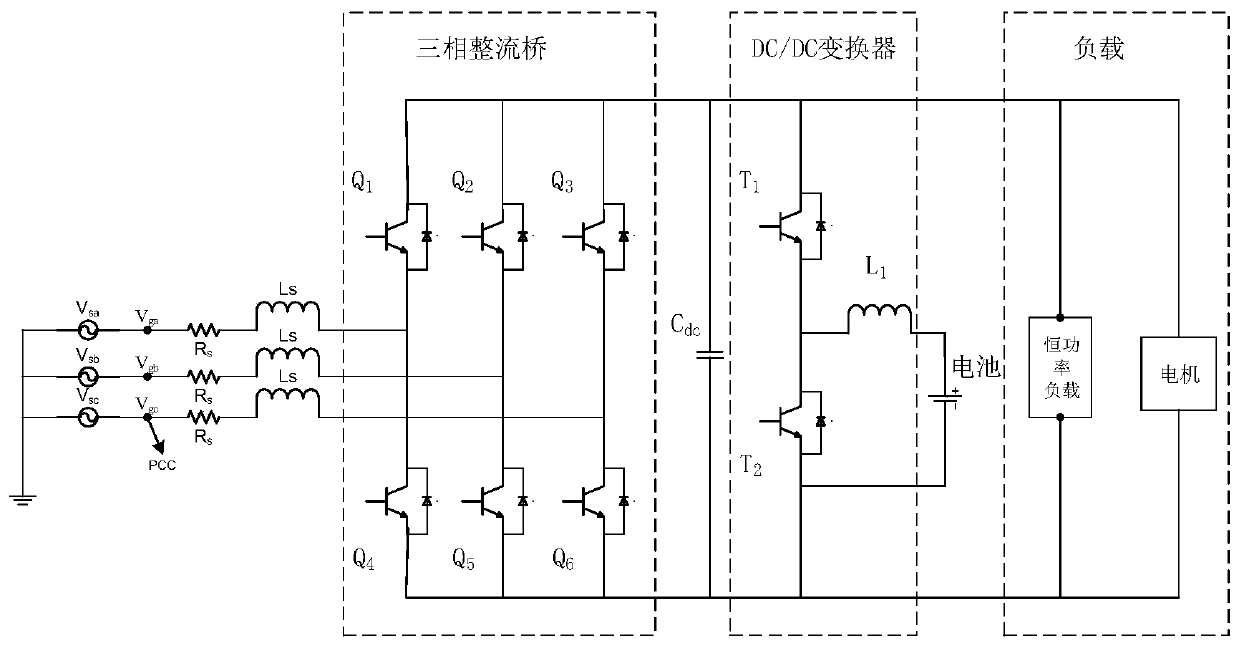

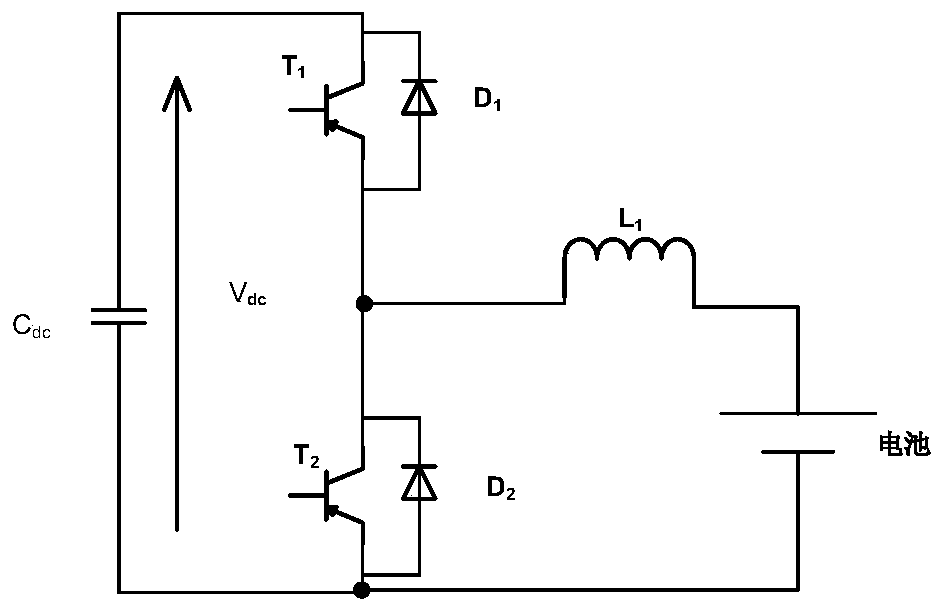

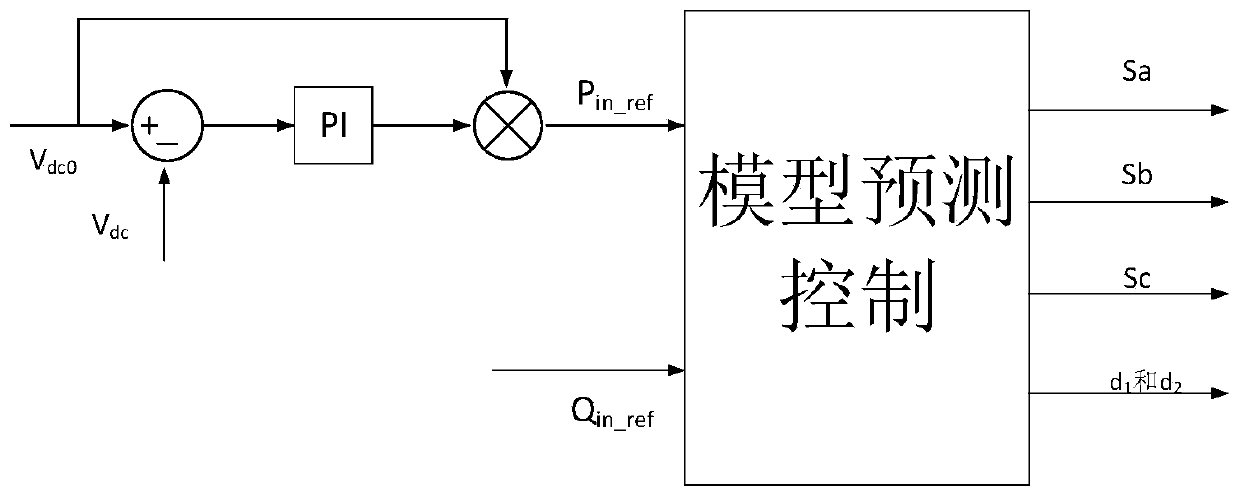

Power buffer design method based on model predictive control

ActiveCN109739107AMeet power quality requirementsRealize multi-objective optimal controlBatteries circuit arrangementsSimulator controlPower topologyElectric aircraft

The invention discloses a power buffer design method based on model predictive control. By utilizing a characteristic of multi-objective optimization of the model predictive control, a three-phase rectifier bridge and a DC / DC converter are controlled at the same time. A target optimization function is designed by adopting a finite set method; in combination with constraint conditions of differentenergy flow coupling, an overall control model is built; multi-objective optimization control can be realized by adopting the model predictive control method; and for a power supply system with an energy storage device, an active energy management mode is adopted, so that the energy optimization distribution of a more electric aircraft can be realized. Therefore, direct-current bus voltage is stable. The model performs buck-boost control on the bidirectional DC / DC converter according to the energy feedback condition of a motor, and direct-current bus power is stable through charging and discharging of a battery pack. The power topology of the power buffer converter is adopted; and the direct current bus power is compensated and absorbed through a storage battery, so that the weight of theaircraft can be effectively reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

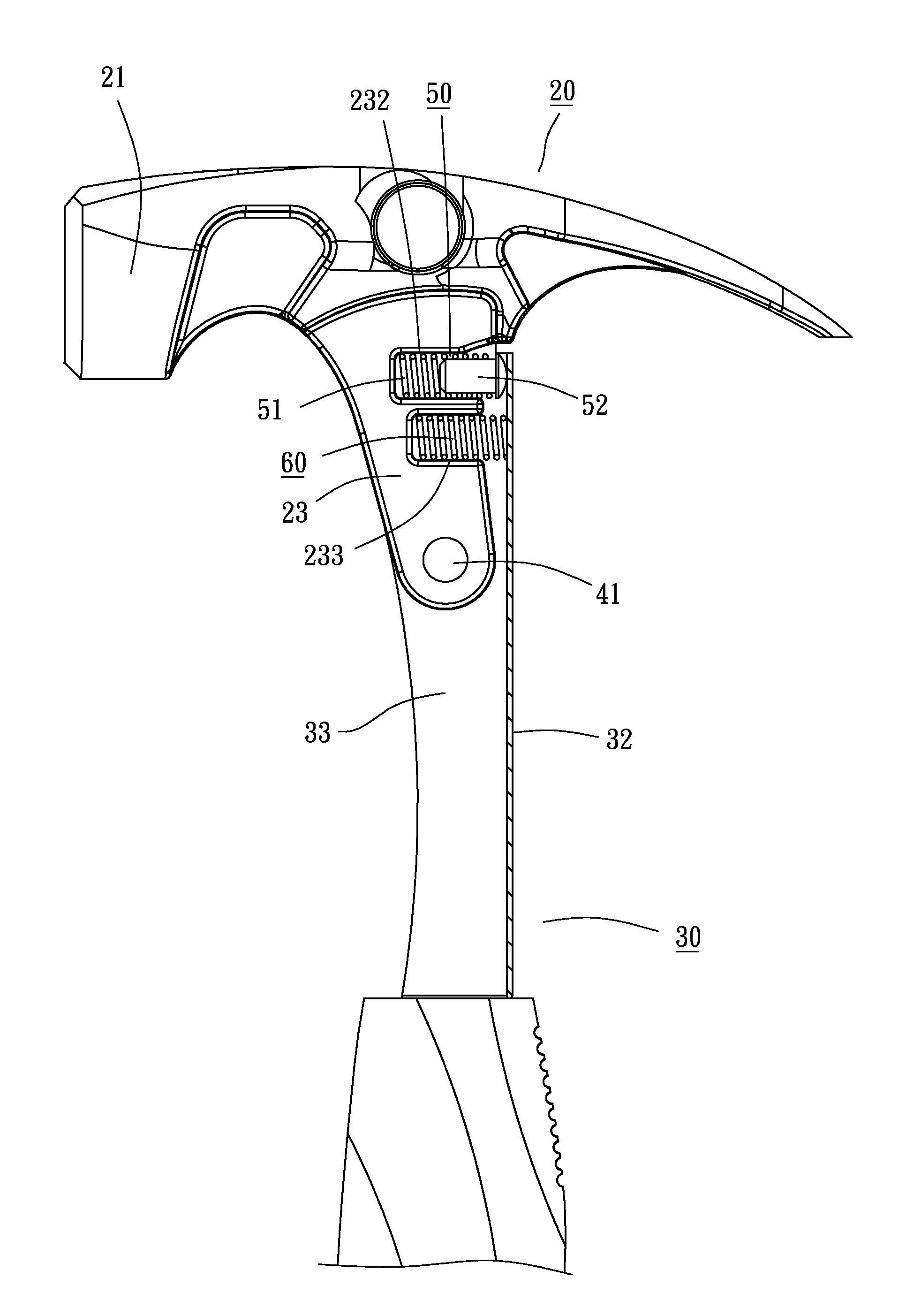

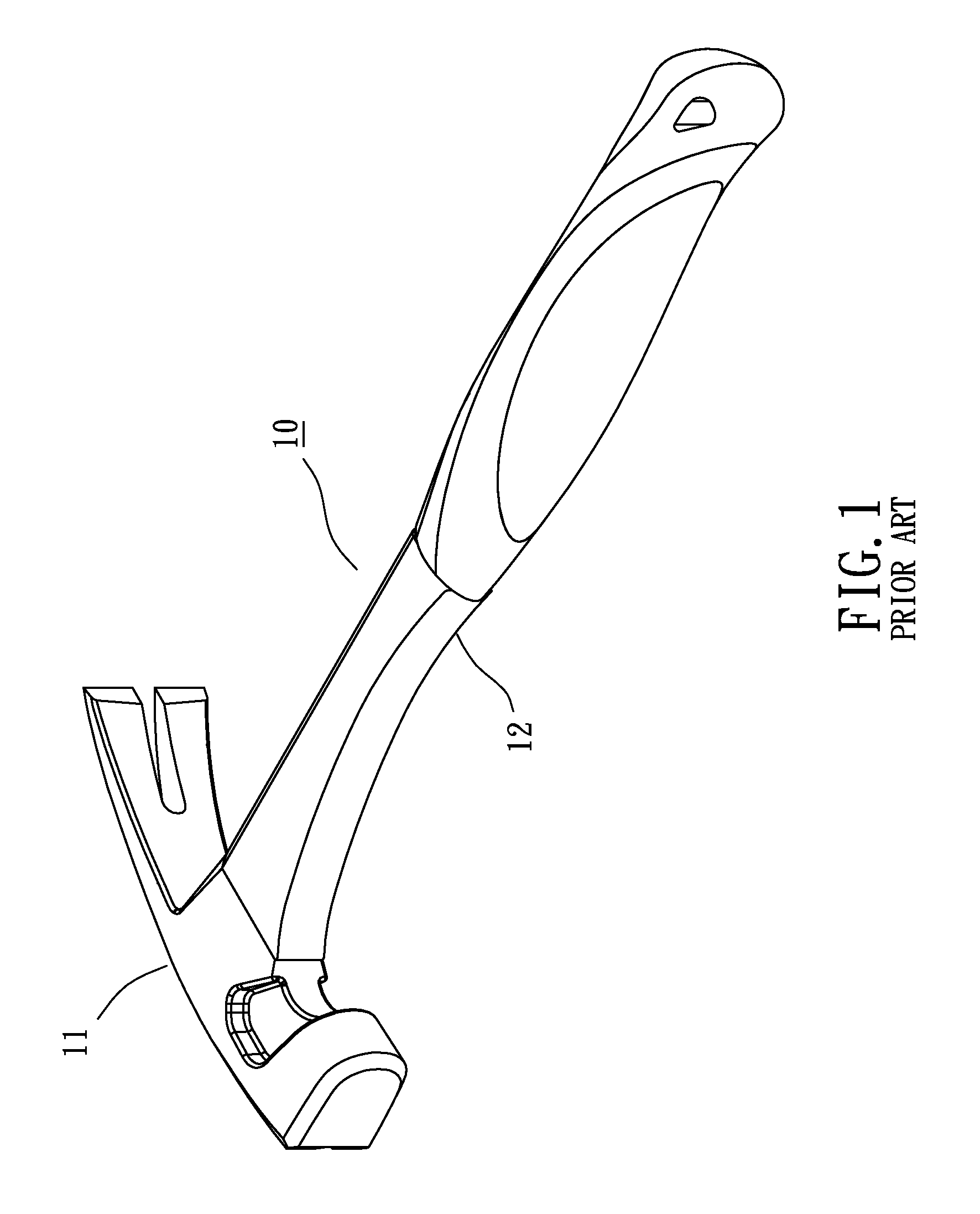

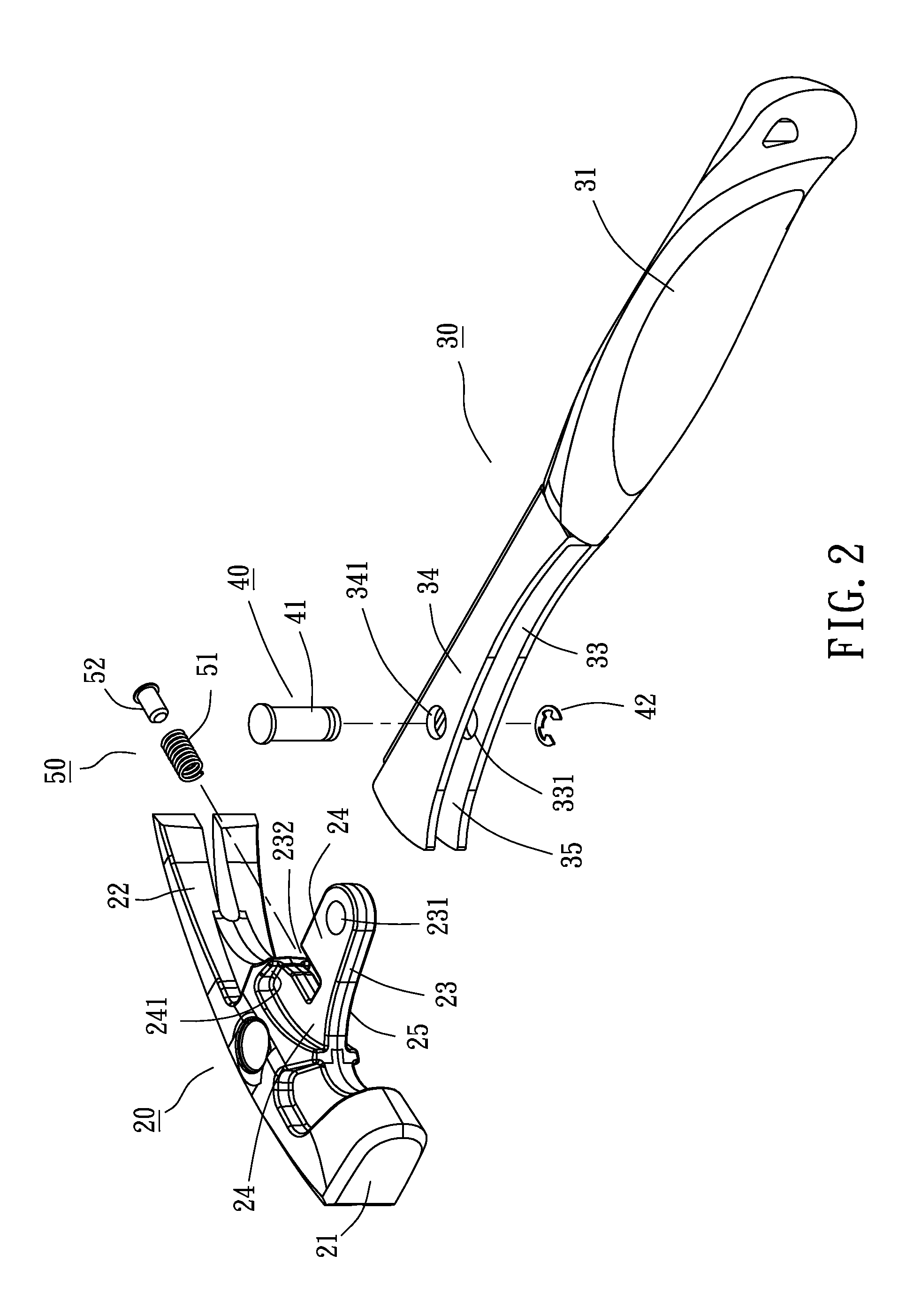

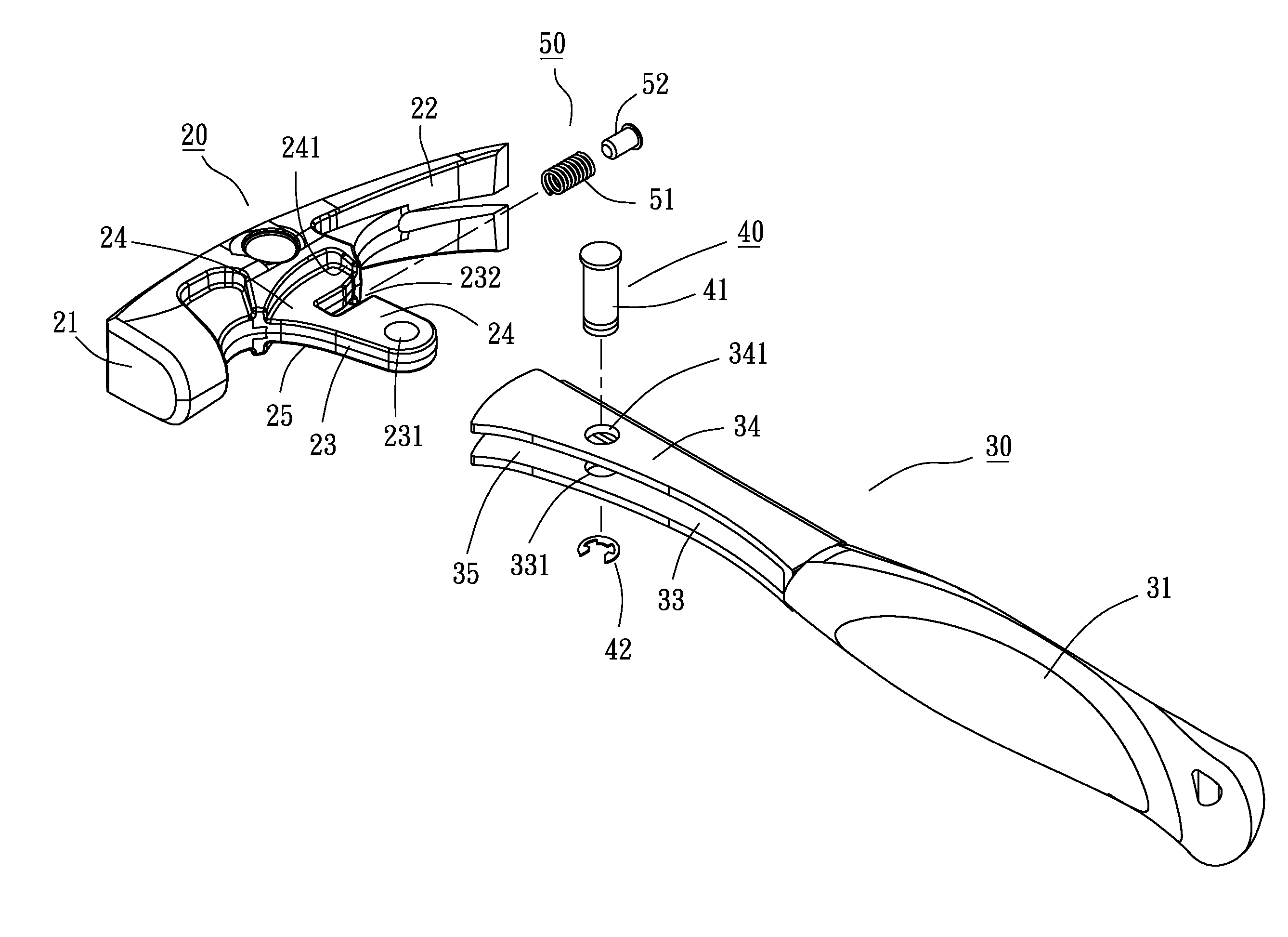

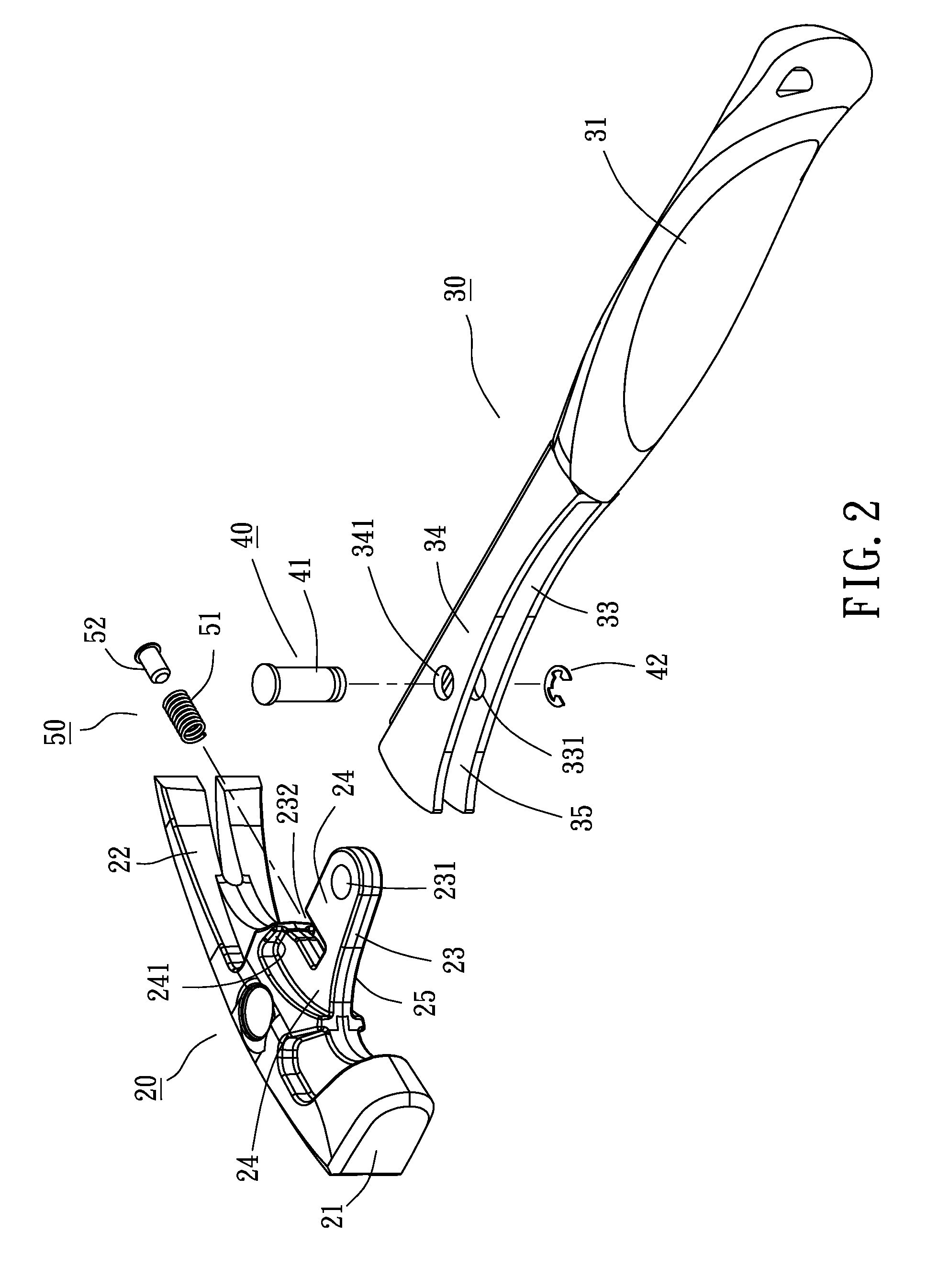

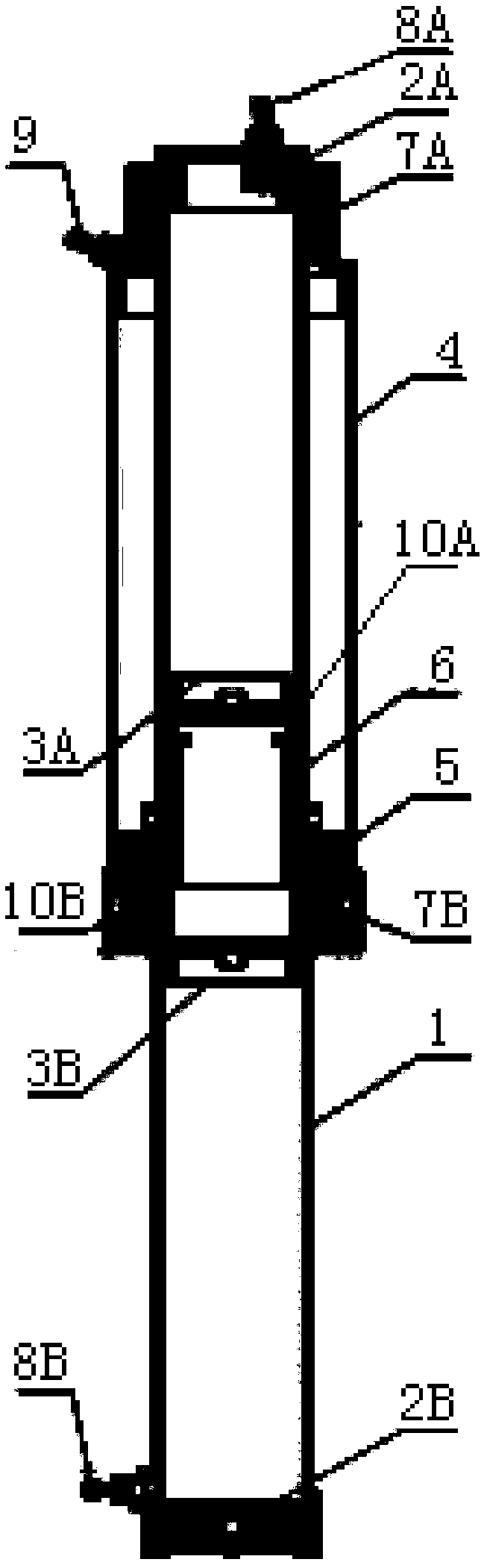

Hammering tool with buffer design

A hammering tool with buffer design includes: a hammering member, a protrusion block section extending from a lower side of the hammering member, a right side of upper section of the protrusion block section being notched to form a first receiving space; a handle member having a grip section, a first plate section, a second plate section and a third plate section being disposed at an upper end of the grip section to define a receiving chamber for inserting the protrusion block section therein; a pivot member for pivotally connecting the protrusion block section of the hammering member with the handle member; and a buffer assembly including a first compression spring received in the first receiving space. A right end face of the protrusion block section of the hammering member is spaced from a left face of the first plate section by a predetermined buffering distance.

Owner:CHEN KUAN WEI

Intelligent barricade safety anti-collision device

InactiveCN110241756APrevent forcible collision with barricadesSimple structureTraffic restrictionsEngineeringBuffer design

The invention discloses an intelligent barricade safety anti-collision device, mainly including a machine shell. A driving cavity, a first lifting cavity, a second lifting cavity, a driven cavity and an air pressure cavity are arranged in the machine shell, lifting mechanisms ejecting an automobile are arranged in the first lifting cavity and the second lifting cavity, the driving cavity is provided with a driving mechanism providing a power output for the device and further provided with a buffer mechanism slowing down a collision automobile, and a camera shooting mechanism is arranged in the driven cavity. According to the intelligent barricade safety anti-collision device, the automobile can be effectively prevented from forcibly colliding barricades, when the automobile forcibly collides the barricades, the advantage of double buffer design is used for protecting personnel present and the automobile to the greatest extent, in the process of the automobile colliding the barricades, the automobile is supported off the ground to cut off the power for continuously driving the automobile forwards, and the good damage reduction effect is achieved.

Owner:南京溧水高新产业股权投资有限公司

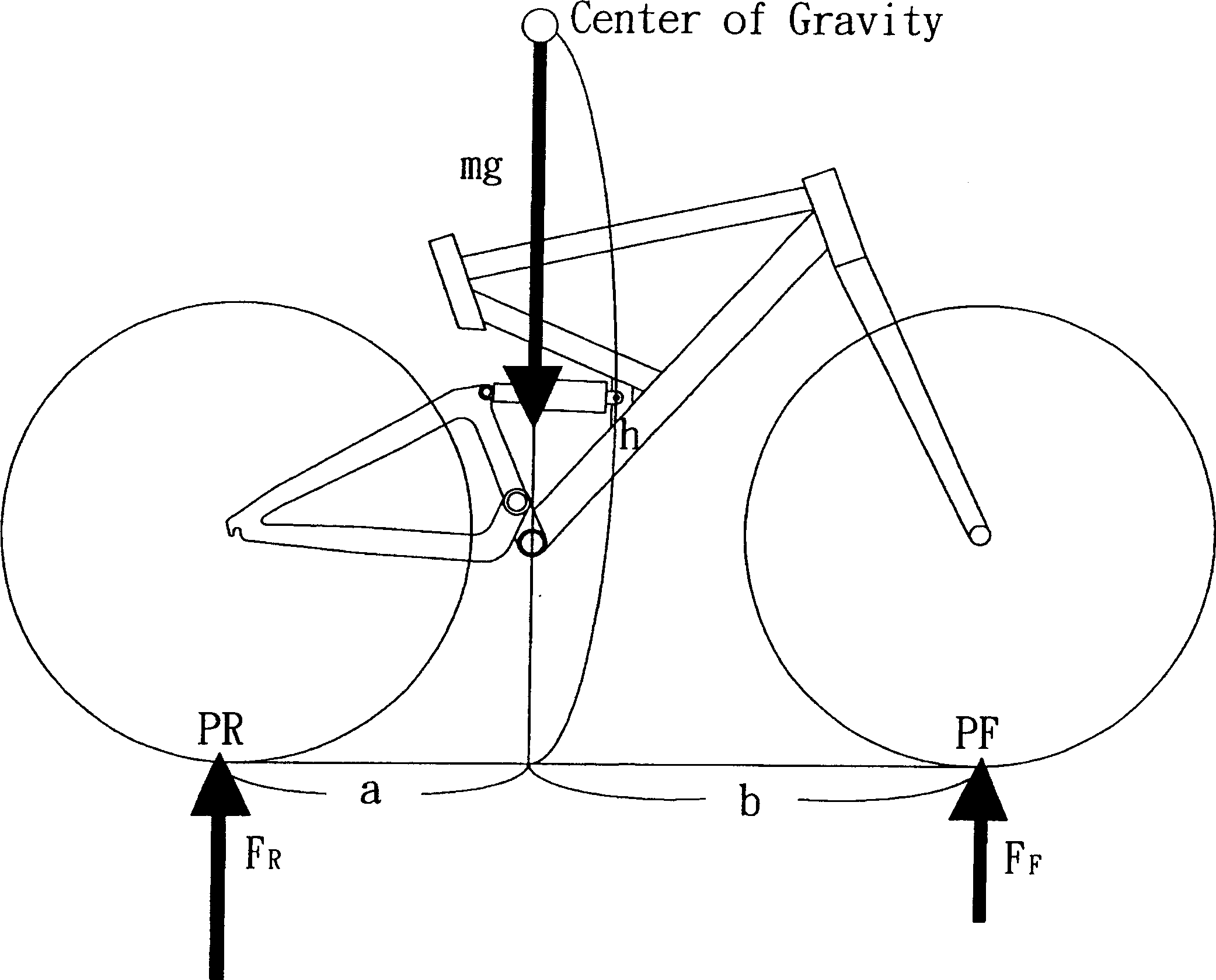

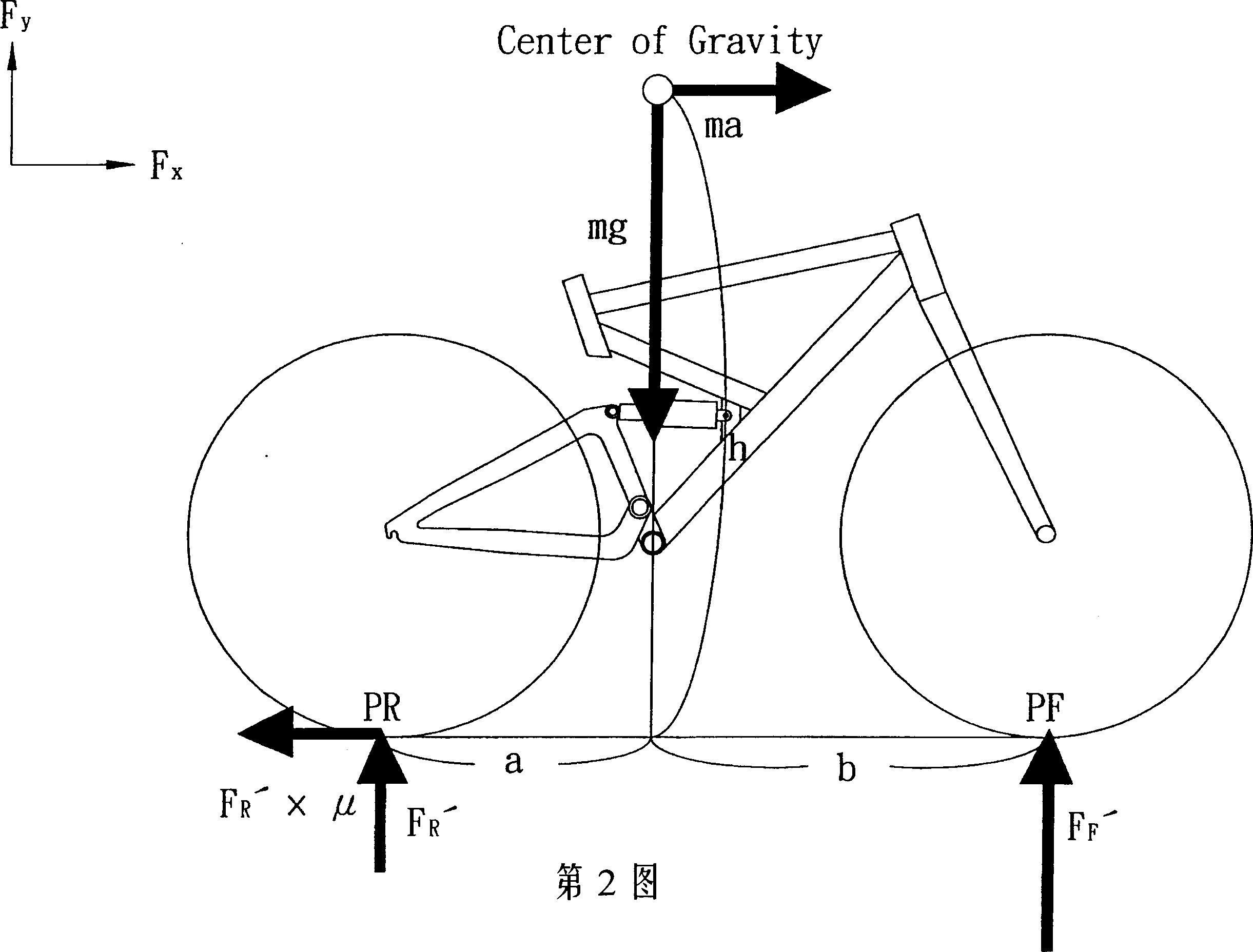

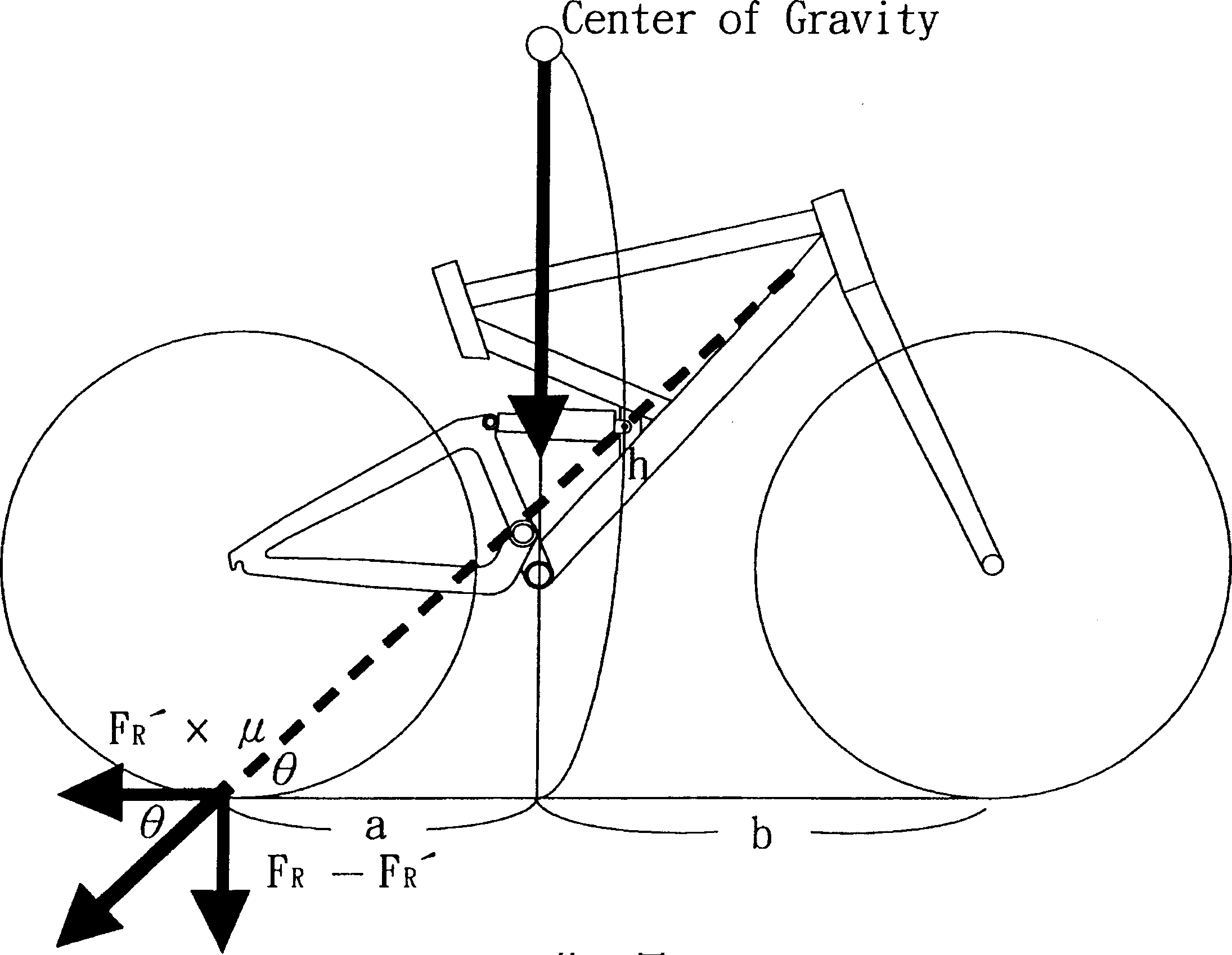

Bicycle with rear suspension avoiding vibration

ActiveCN1861466AAvoid damageReduce pedaling energy lossAxle suspensionsBicyclesControl theoryEnergy loss

A bike with suspended back vibration damper for low pedaling energy loss, low kickback or pedal feedback, and low braking affection is disclosed. The vibration damper features no sag setting and buffer design. The bike with suspended back vibration damper is characterized by having low pedaling energy loss, low braking affection, low kickback or pedal feedback, low energy loss, good comfort and long life of the shock absorber no matter what standing or sitting.

Owner:GIANT BICYCLES

Hammering tool with buffer design

A hammering tool with buffer design includes: a hammering member, a protrusion block section extending from a lower side of the hammering member, a right side of upper section of the protrusion block section being notched to form a first receiving space; a handle member having a grip section, a first plate section, a second plate section and a third plate section being disposed at an upper end of the grip section to define a receiving chamber for inserting the protrusion block section therein; a pivot member for pivotally connecting the protrusion block section of the hammering member with the handle member; and a buffer assembly including a first compression spring received in the first receiving space. A right end face of the protrusion block section of the hammering member is spaced from a left face of the first plate section by a predetermined buffering distance.

Owner:CHEN KUAN WEI

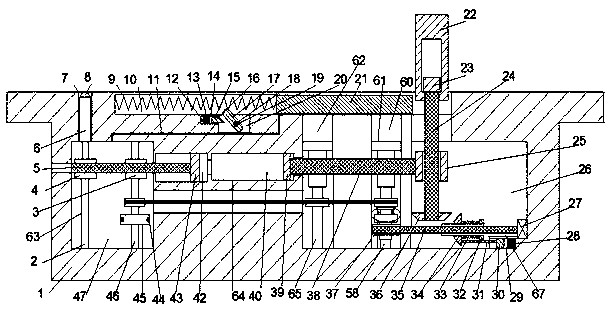

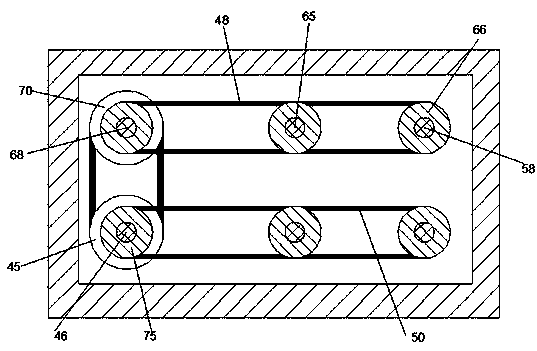

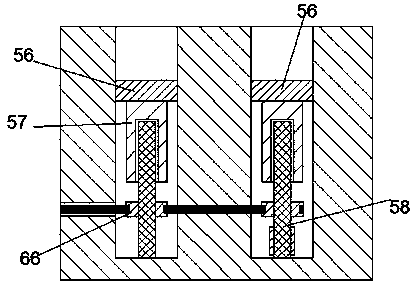

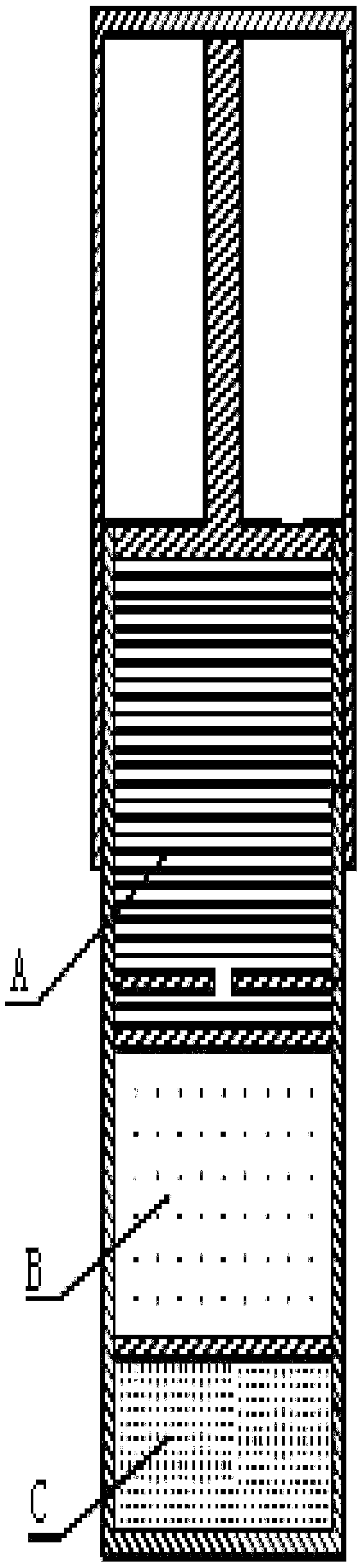

Double-cavity buffer

ActiveCN109296691AShorten the lengthCompact structureSpringsGas and liquid based dampersEngineeringAircraft landing

The invention belongs to the technical field of aircraft landing gear buffer design, particularly relates to a double-cavity buffer, and provides a double-cavity buffer. The double-cavity buffer comprises an inner cylinder, a first plug cap, a second plug cap, a first floating piston, a second floating piston, an outer cylinder and a spacer sleeve; two independent first oil cavities, a first air cavity and a second air cavity are formed in the inner cylinder; the outer side of the inner cylinder is sleeved with the outer cylinder; a second oil cavity is formed between the outer cylinder and the inner cylinder and communicates with the first oil cavity through a throttling hole; and the second oil cavity, the first air cavity and the second air cavity are arranged in parallel. Compared withthe prior art, the length of the double-cavity buffer can be effectively decreased, the structure is more compact, and the small mass can be obtained.

Owner:CHINA HELICOPTER RES & DEV INST

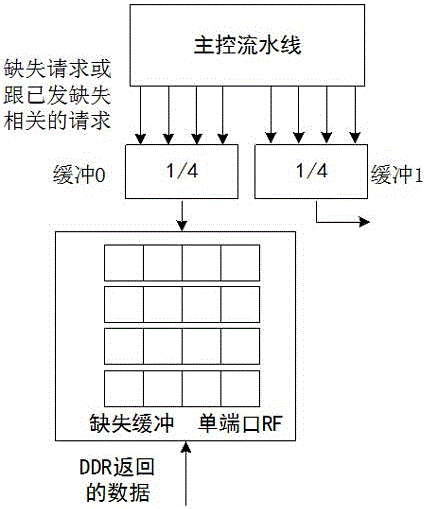

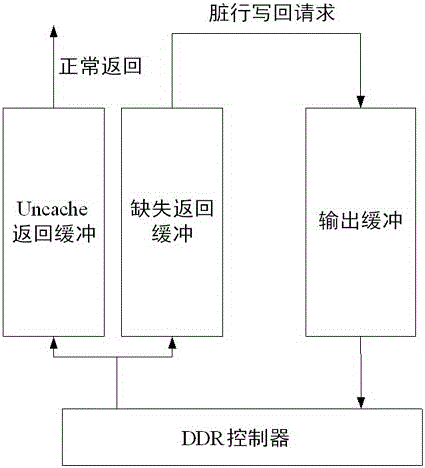

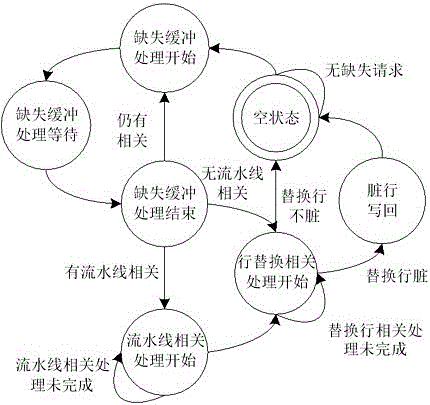

Buffering method capable of supporting non-blocking missing processing

InactiveCN105955711AImprove processing efficiencyReduce missing costConcurrent instruction executionAccess timeAssembly line

The invention discloses a buffering method supporting non-blocking missing processing. When a processor encounters missing requests, the method temporarily stores the missing requests in the missing instruction queue through buffering, allowing the pipeline to continue sending subsequent irrelevant requests. , hide the miss cost in the normal processing of irrelevant requests, and reduce the memory access latency by reducing the buffer miss cost. In the present invention, multiple missing requests are overlapped, multiple judgments can be made through the missing buffer, and multiple missing requests are stored uniformly, thereby further reducing the actual missing cost. The invention has wide applicability, can be applied to various multi-core chip buffer designs, and can improve the efficiency of pipeline processing.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

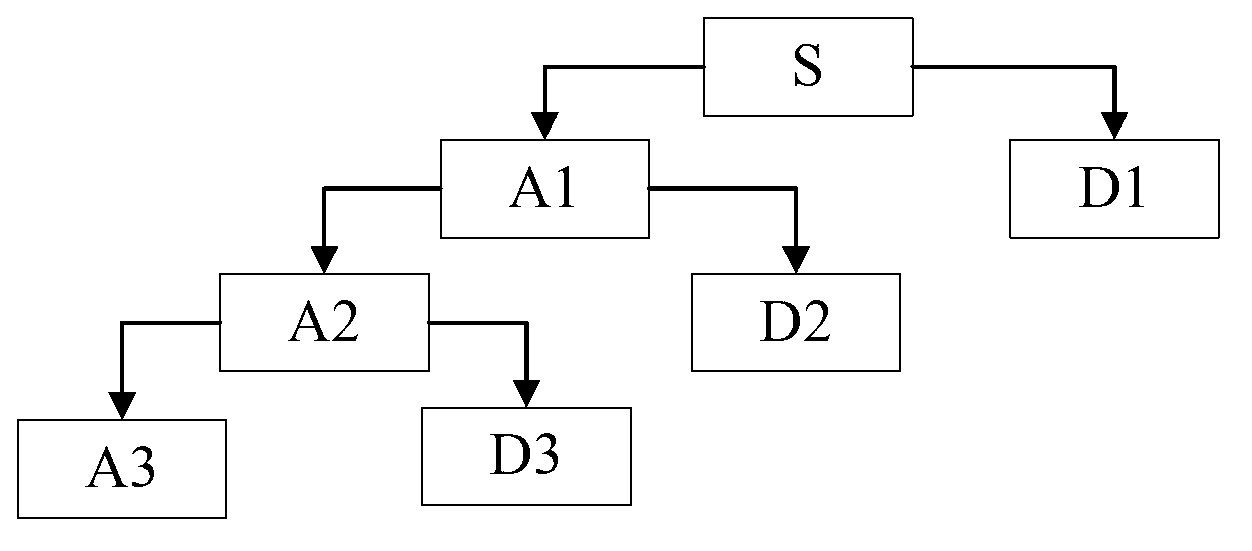

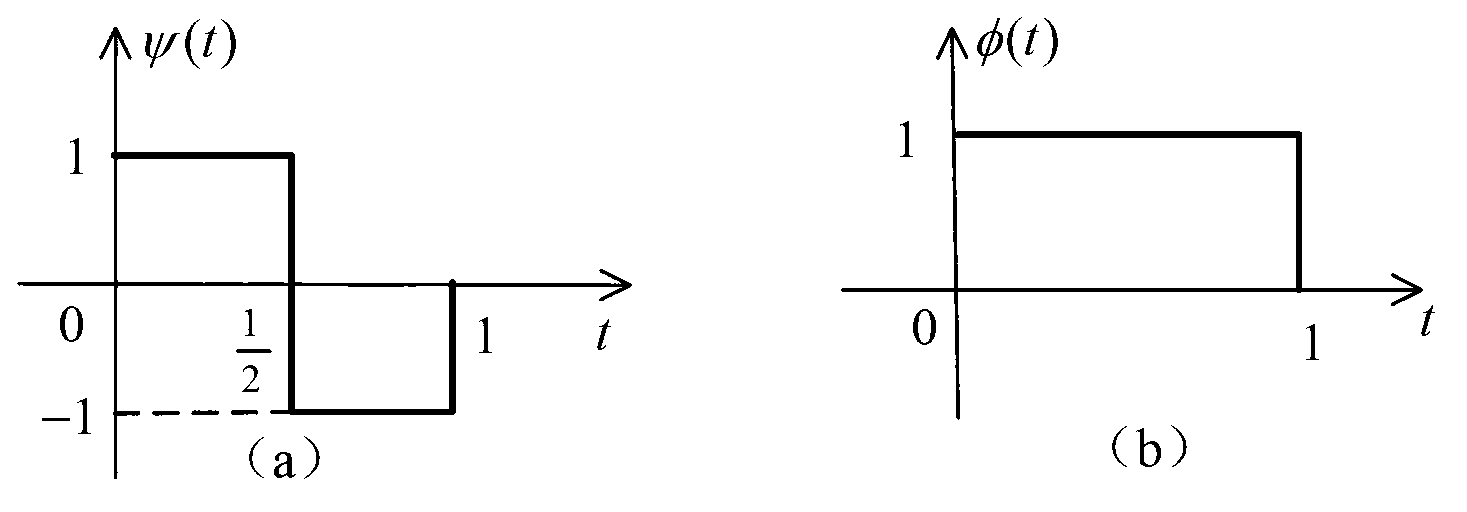

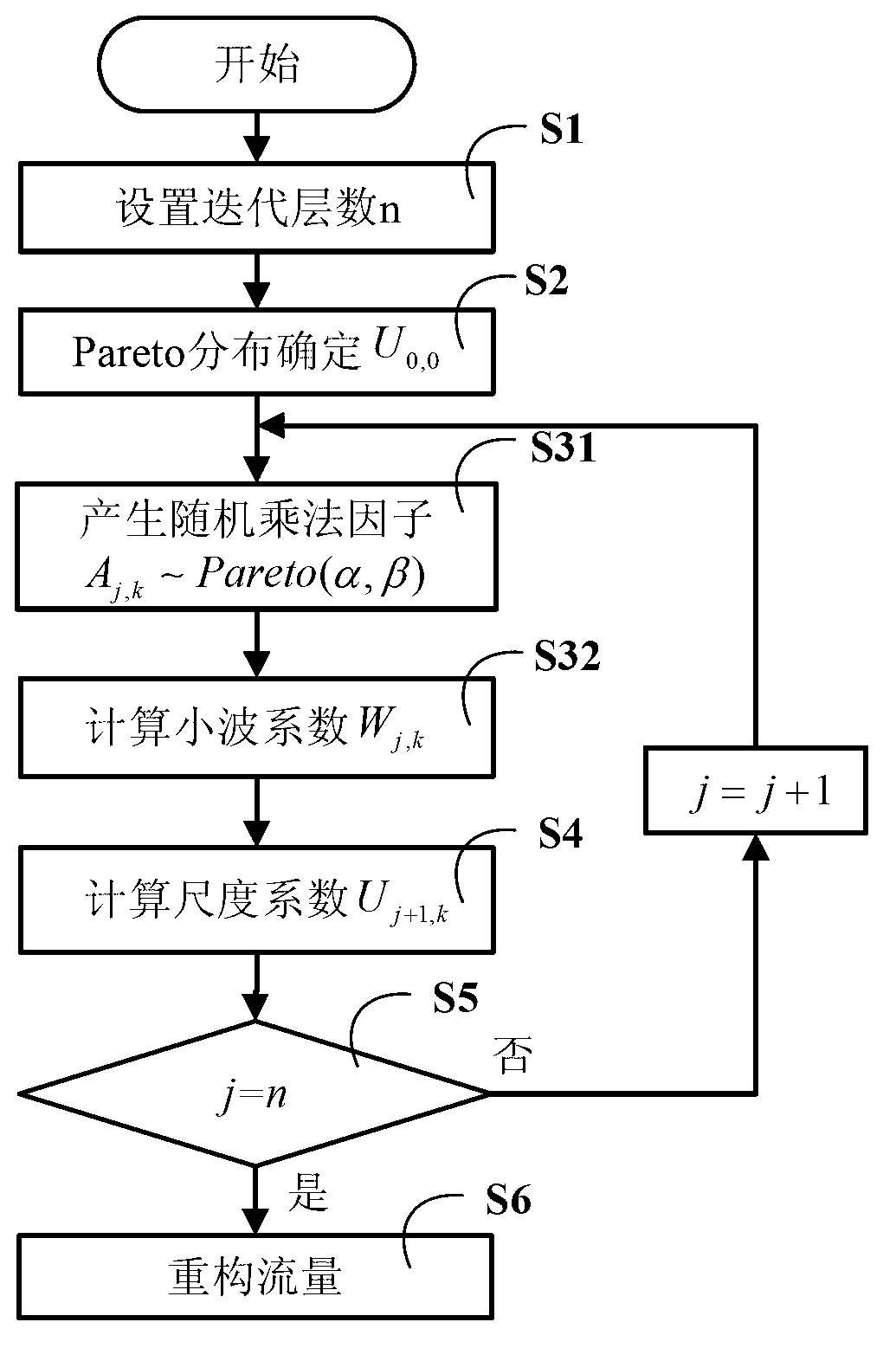

Multi-fractal network flow reconstruction method

ActiveCN103312538AFine refactoringAccurate reconstructionData switching networksDistribution characteristicReconstruction method

The invention discloses a multi-fractal network flow reconstruction method. According to the method, a roughest scale coefficient and a random multiplication factor are generated and determined by adopting pareto distribution of a heavy tail distribution characteristic, so that the non-negativity of scale coefficients and wavelet coefficients is ensured, the reconstructed flow is accordant with the heavy tail distribution characteristic of practical flow, and the network flow can be reconstructed more finely and accurately. Network flow signals reconstructed with the method disclosed by the invention is applied to network analysis and management activities such as network planning, load balance, blockage control, buffer design and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

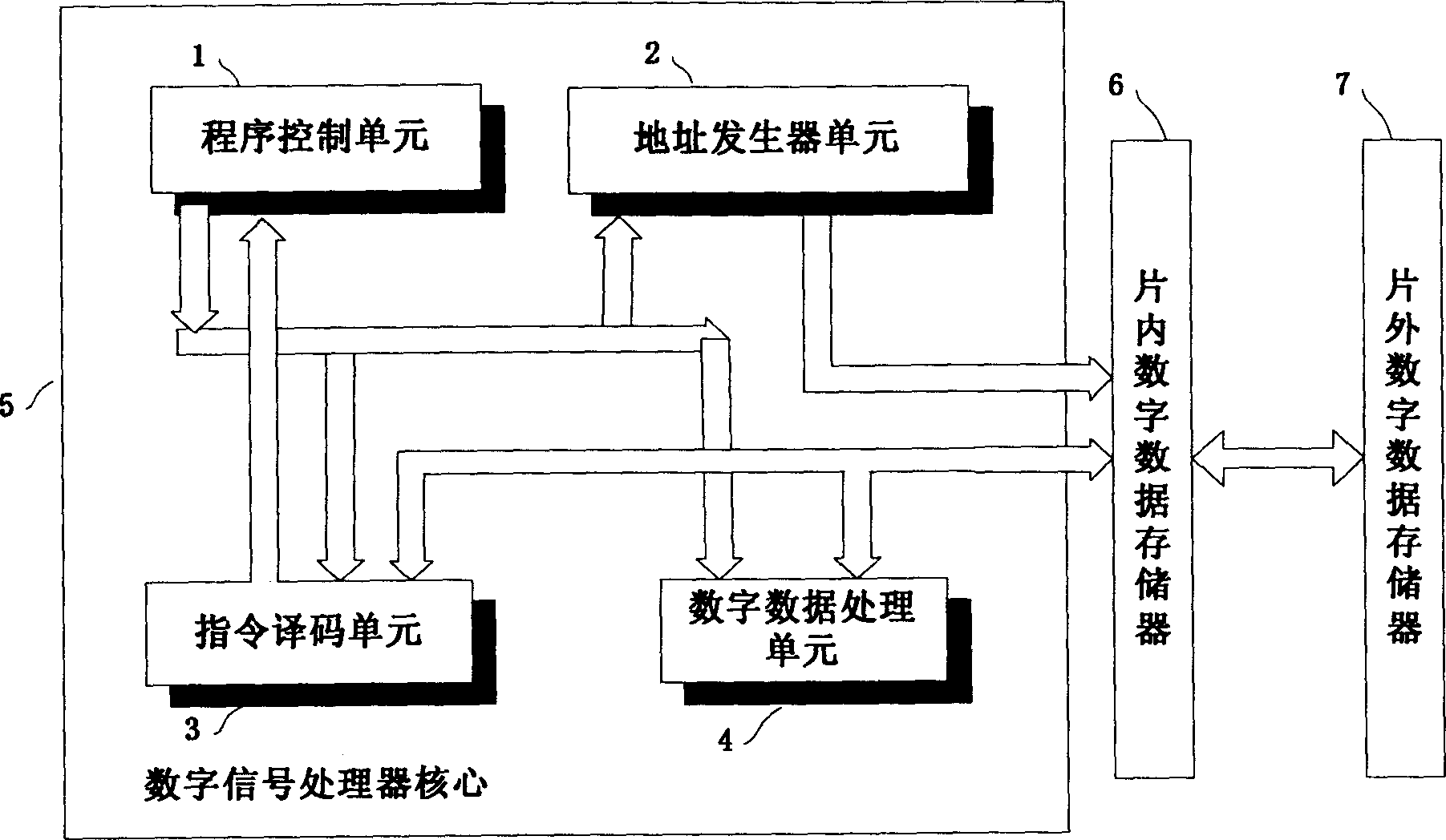

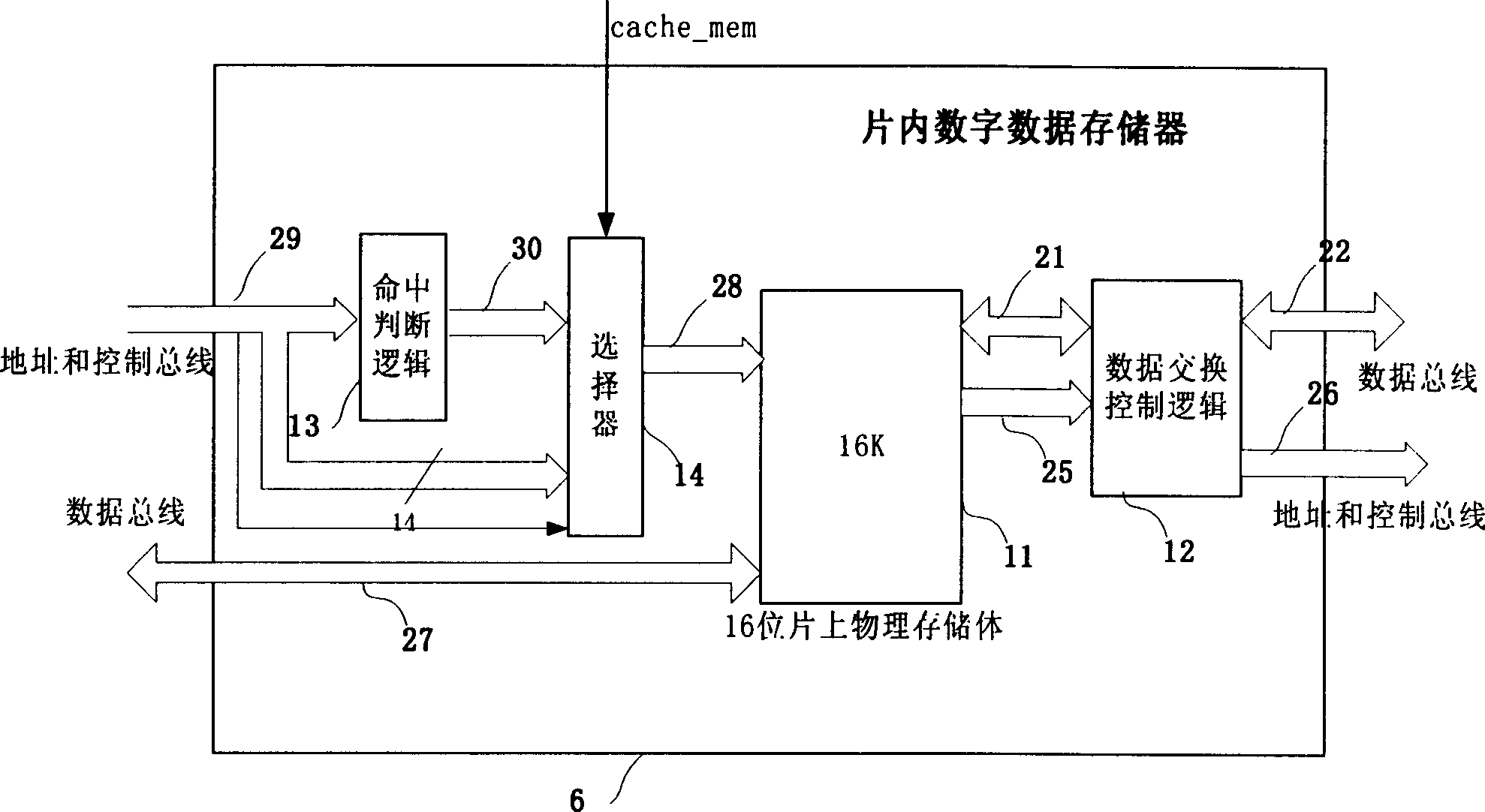

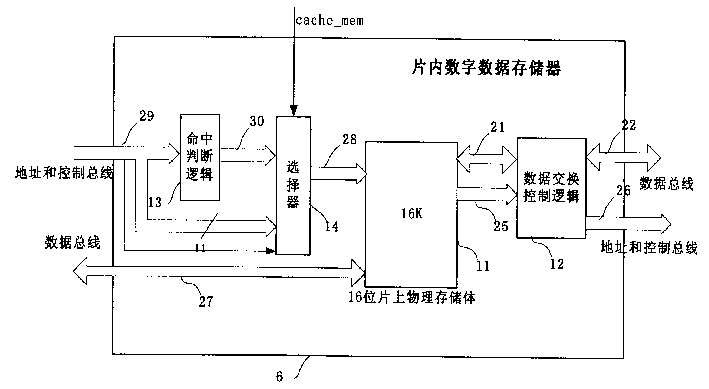

Digital signal processor with a repeatable switching buffer memory

InactiveCN1521631AIncrease flexibilityCost-effectiveMemory systemsMachine execution arrangementsDigital signal processingInternal memory

A digital signal processor with switching over buffers mainly comprises a program control unit, an address generator unit, an instruction decoding unit, a digital data processing unit, an inner-chip digital data storage device, an outer-chip digital data storage device, a selector and a hit judgment logic equipment. The invention improves the existing buffer design, only by a the arrangement of a port, the buffer on the chip can be modified into conventional on chip internal memory, which enables accurate and efficient internal memory access operation when executing small programs.

Owner:上海领微科技有限公司 +1

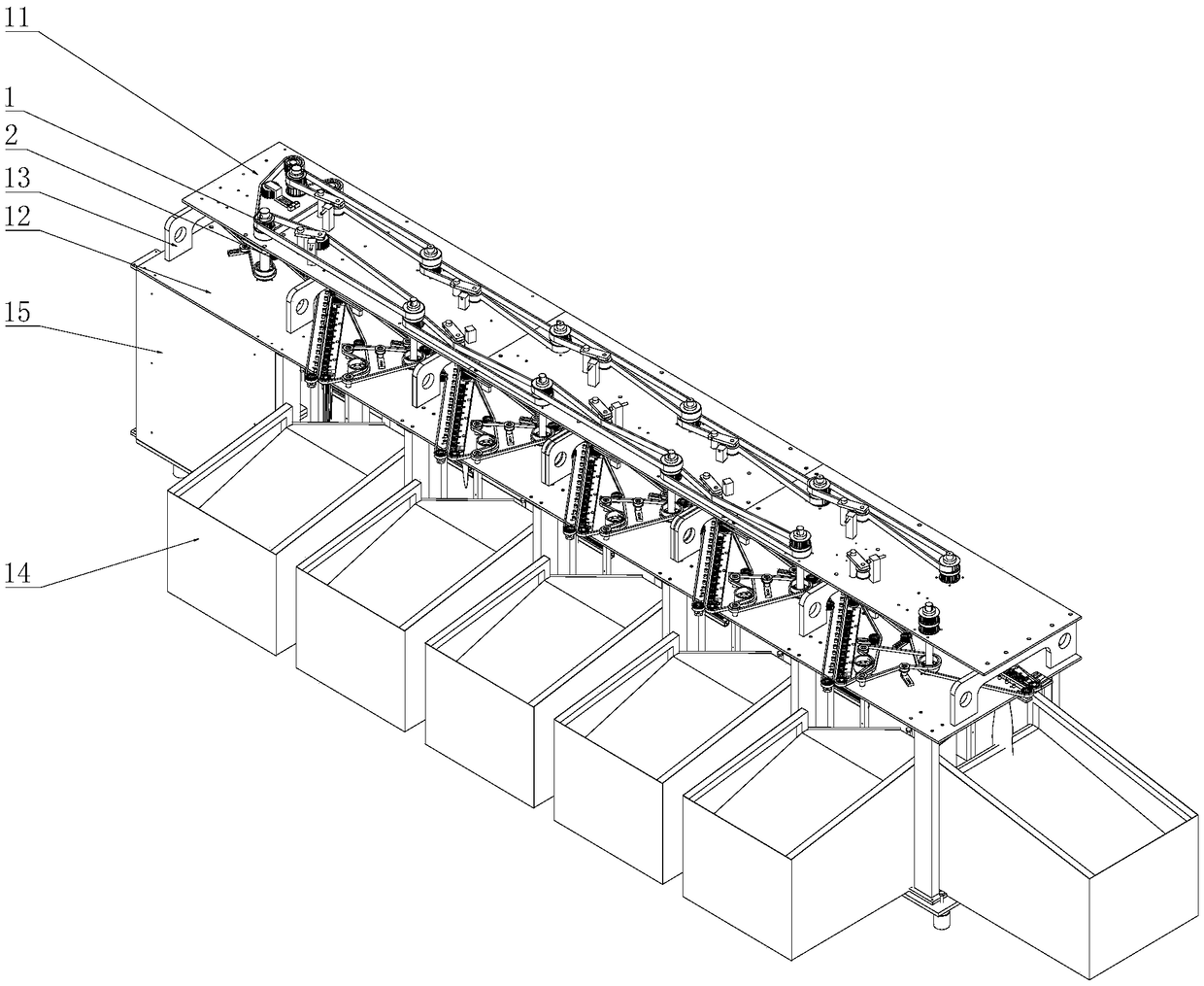

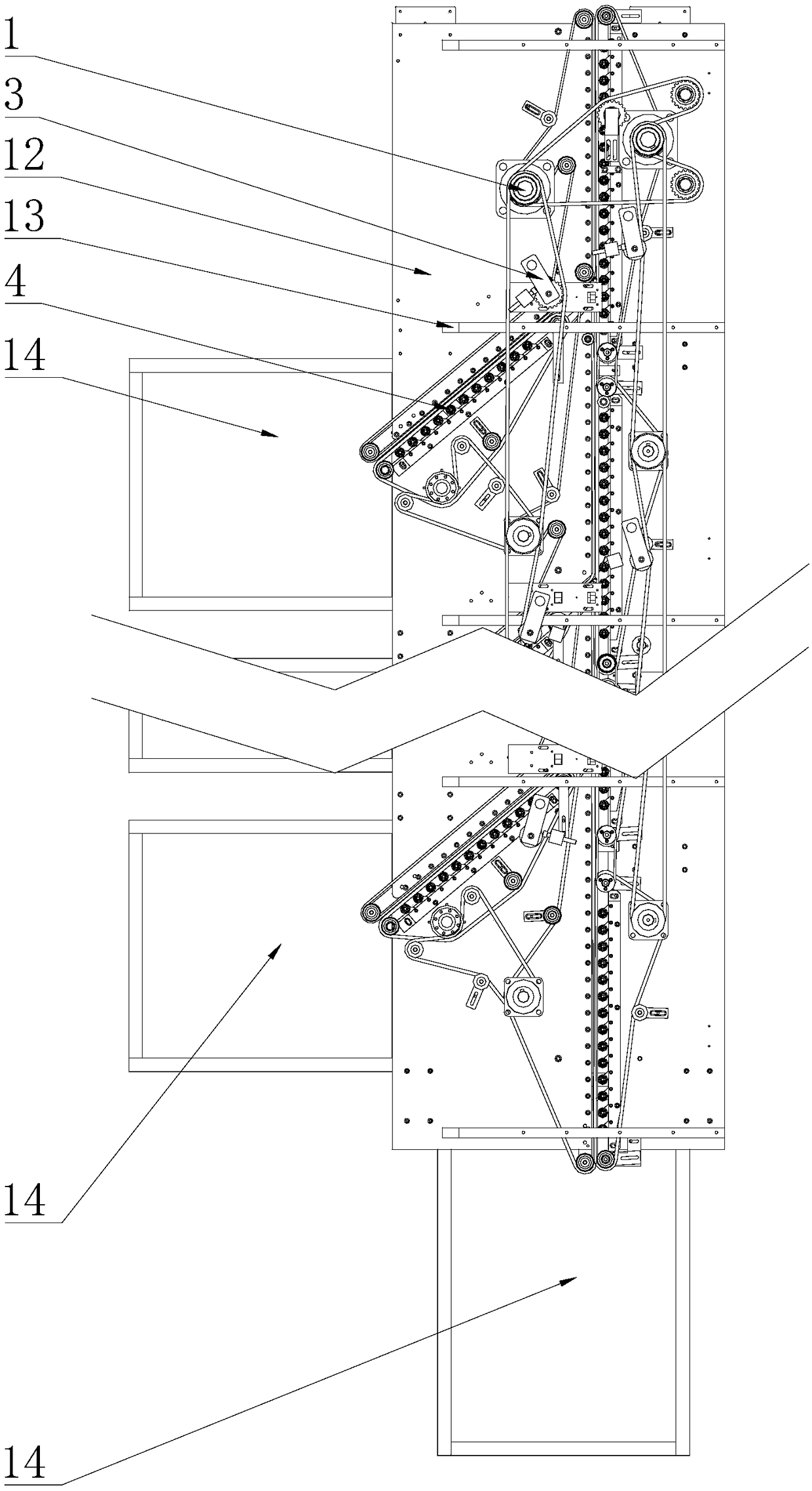

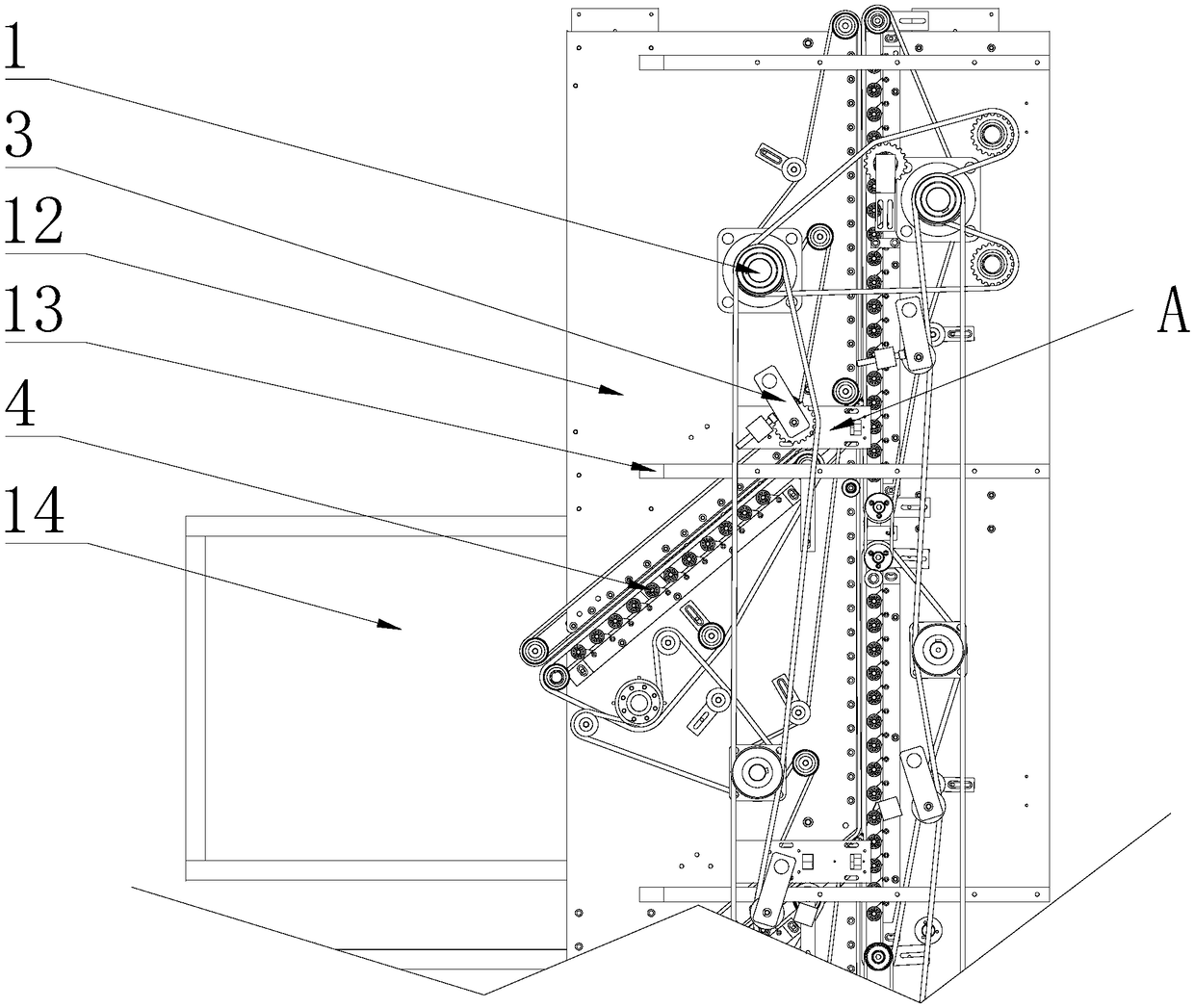

Binning device used after tobacco leaf sorting

The invention relates to a binning device, in particular to a binning device used after tobacco leaf sorting. In order to solve the problem of excessive cylinder stroke and loud sound of the binning mechanism in the existing tobacco leaf binning device, the invention provides the binning device used after the tobacco leaf sorting. The binning device comprises a power mechanism and at least one binning station; the binning station comprises a transmission mechanism, a conveying mechanism and a binning mechanism, wherein the power mechanism drives the transmission mechanism to move, the transmission mechanism and the conveying mechanism are in a co-movement relation, and the binning mechanism performs the binning process on tobacco leaves transported by the conveying mechanism. By adopting the binning device, the cylinder movement stroke is reduced, and the speed of the binning is improved, so that the 10 pieces / s production capacity requirement of equipment is satisfied; a limiting buffer design can effectively reduce the impact and reduce the noise of the impact when binning; whole screws are fixed by adopting an anti-loose design, thereby meeting the frequent movement of the mechanism; and the binning device also has the characteristics of durability, stability and firmness.

Owner:BEIJING FOCUSIGHT TECH

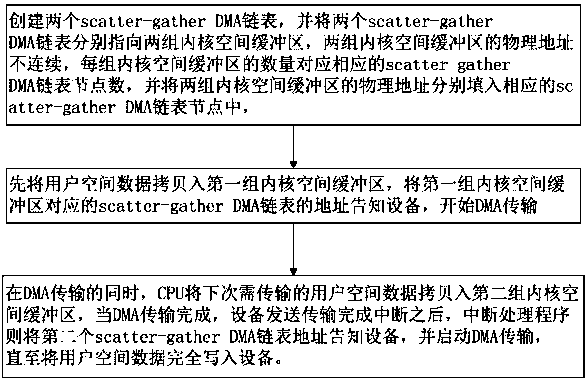

A data transfer buffer design method of Scatter-Gather DMA

InactiveCN109189702AImprove efficiencyElectric digital data processingInterrupt handlerData transmission

The invention provides a data transfer buffer design method of Scatter-Gather DMA and relates to the technical field of data transmission. When scatter-gather DMA is used for transferring data, two scatter-gather DMA linked lists are created, and the two scatters-gather DMA linked lists point to two sets of kernel space buffers, and the number of each set of kernel space buffers corresponds to thenumber of nodes of the corresponding scatter-gather DMA linked list; while user space data is copied into a set of kernel space buffers for DMA transfer, the next user space data to be transferred iscopied into another set of kernel space buffers by the CPU. When the last DMA transfer is completed, the next DMA transfer is initiated by the interrupt handler until the user space data is completely written to the device.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD