Digital signal processor with a repeatable switching buffer memory

A digital signal and processor technology, applied in the field of digital signal processors, can solve the problems of waste, singleness, and inability to know the exact content of the cache, and achieve the effect of increasing flexibility and improving cost performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

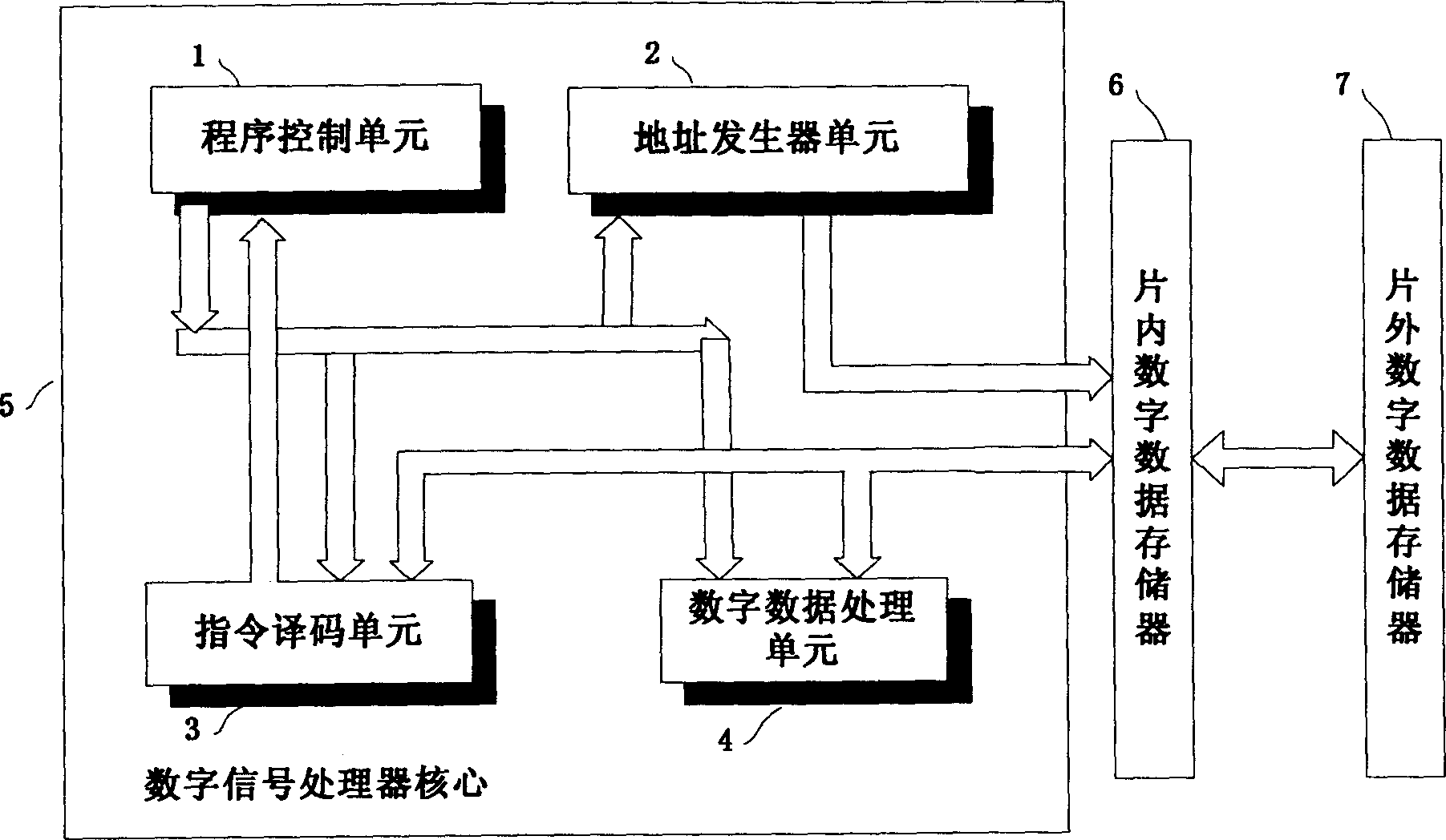

[0010] figure 1 It is a block diagram of the digital signal processor involved in the present invention, which mainly describes the connection relationship of each component module of the overall digital signal processor. Such as figure 1 As shown, the digital signal processor core 5 has a program control unit 1, an address generator unit 2, an instruction decoding unit 3, and a digital data processing unit 4, and the digital data memory 6 and the digital signal processor core 5 constitute the entire digital signal processing unit. device. The instruction decoding unit 3 translates the instruction code into the control signal representing the meaning of the instruction inside the digital signal processor core 5, and these described control signals are connected to the program control unit 1, and the program control unit 1 sends the address generation unit 2, the instruction translation The code unit 3 and the digital data processing unit 4 send out the control signals needed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More