FPGA device with power-on reset signal waveform adjustable function

A technology of reset signal and signal waveform, applied in the field of FPGA, can solve the problems of not being able to reach the working voltage immediately, poor flexibility, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

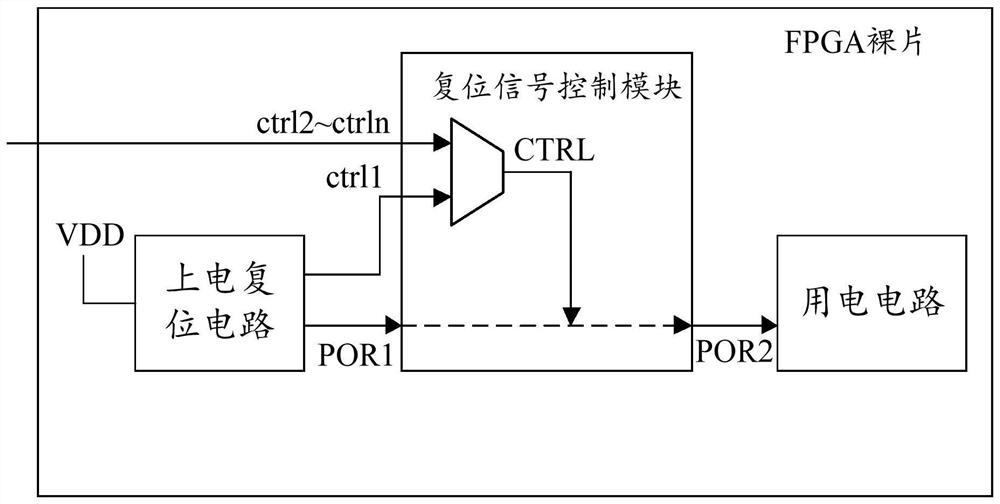

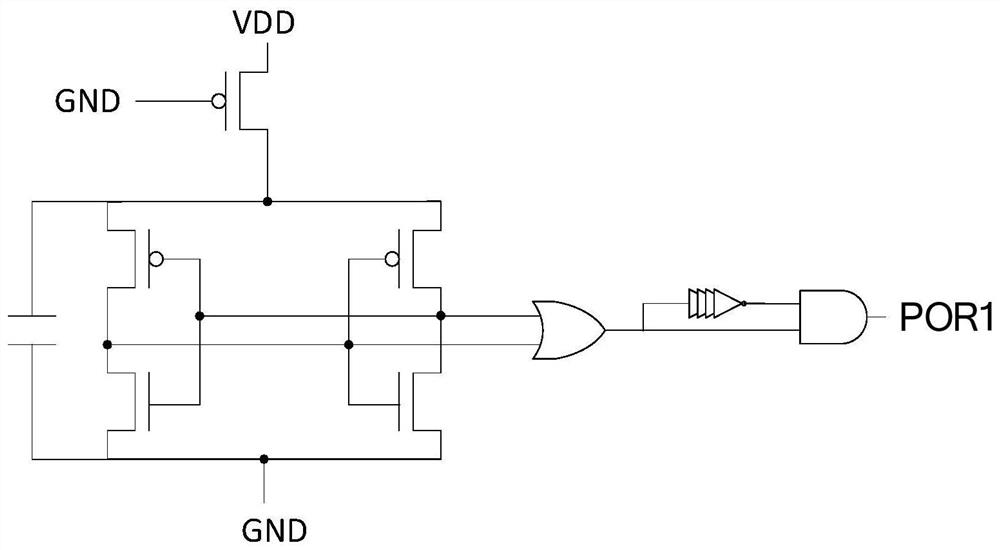

[0018] This application discloses an FPGA device with a power-on reset signal waveform adjustable function. The FPGA device includes an FPGA die. Please refer to figure 1 , the FPGA die includes a power-on reset circuit, a power-using circuit, and a reset signal control module. The input terminal of the power-on reset circuit is connected to the power supply VDD, and the output terminal outputs the first power-on reset pulse signal POR1. The power-on reset circuit can detect The power-on action of the internal power supply VDD and the output of the first power-on reset pulse signal POR1 are used for reset and restart of the power circuit in the FPGA die and other power-on procedures. The power-on reset circuit is an existing conventional circuit, and its specific circuit structure can be refer to figure 2 , this application does not introd...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More