FPGA device of network-on-chip is formed using silicon connection layer

An on-chip network and connection layer technology, applied in the FPGA field, can solve problems such as difficult promotion, difficult production, and chip area occupation, and achieve the effect of efficient interconnection and communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

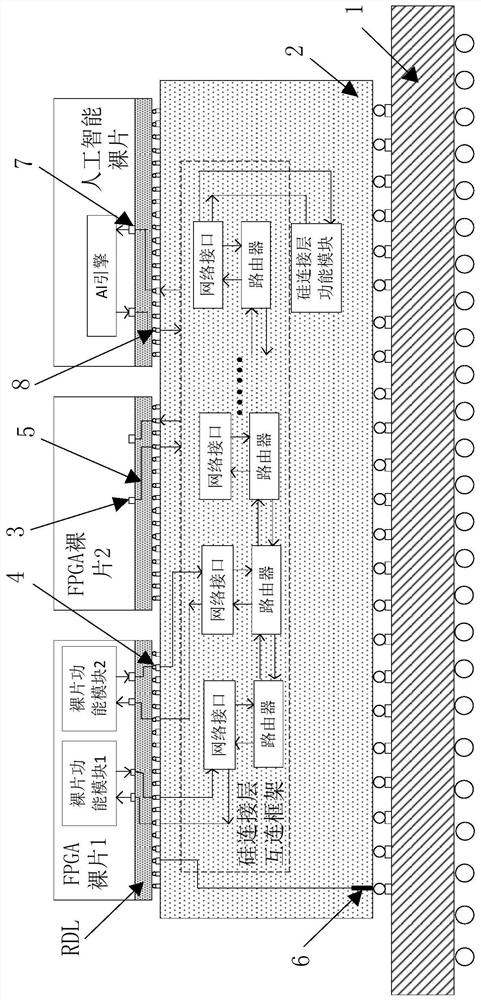

[0027] This application discloses an FPGA device that uses a silicon connection layer to form an on-chip network. Please refer to figure 1 , the FPGA device includes a substrate 1, a silicon connection layer 2, and an FPGA die that are sequentially stacked from bottom to top. Protect the packaging shell of each component, and also include the pins connected to the substrate for signal extraction, etc., figure 1 These conventional structures are not shown in detail.

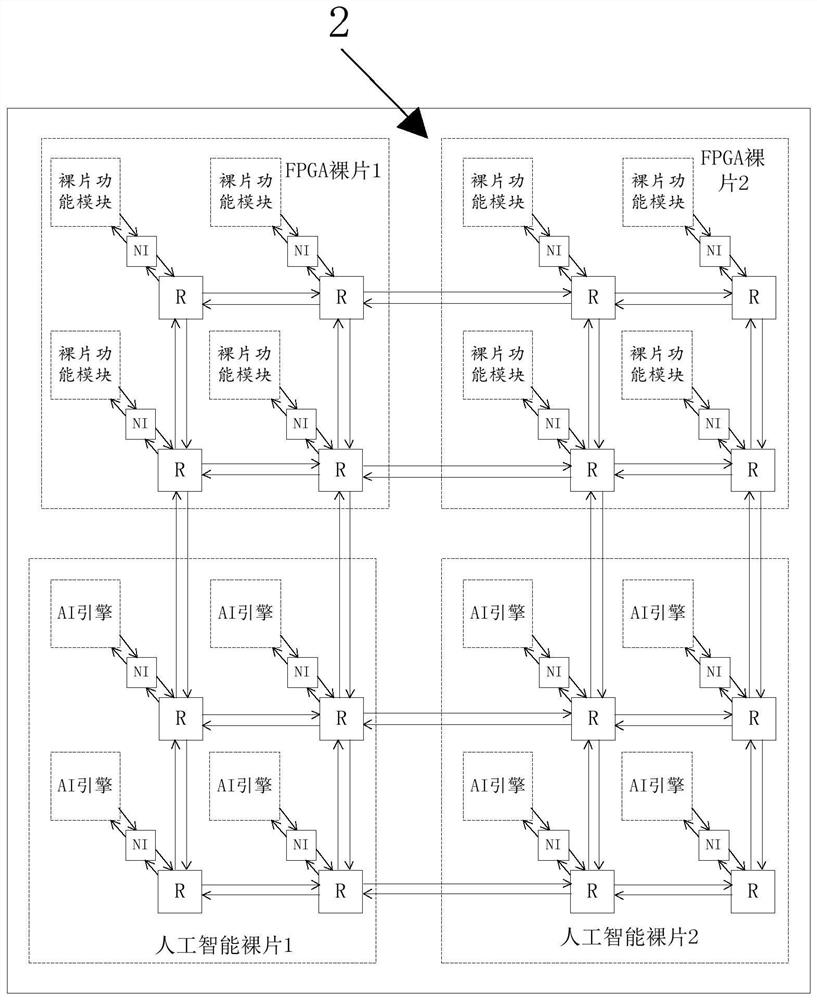

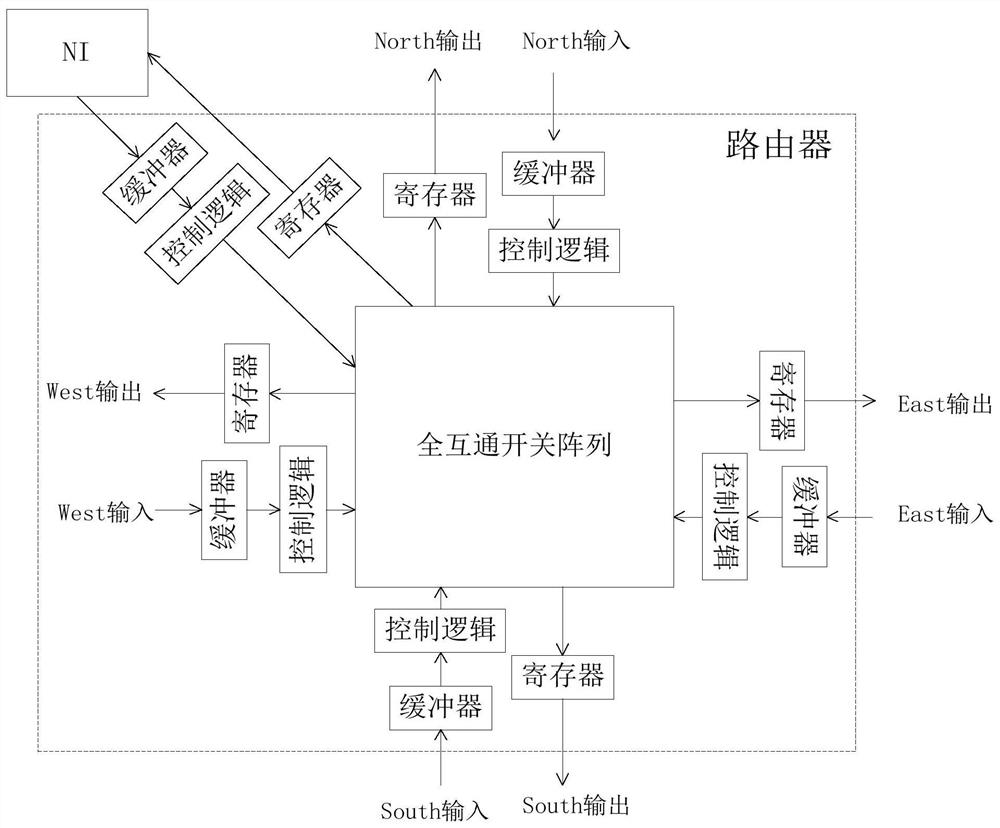

[0028] The FPGA bare chip in this application is different from the conventional FPGA bare chip. The conventional FPGA bare chip mainly includes CLB, PLBs, BRAM, DSP, PC, IOB and other bare chip functional modules. Each bare chip functional module has a Interconnect resource modules (INT) distributed around the bare chip functional modules with the same structure, and the hori...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More