Reliability test system for laser chip

A test system and reliability technology, applied in the field of reliability test systems for laser chips, can solve problems such as troublesome and poor temperature control accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

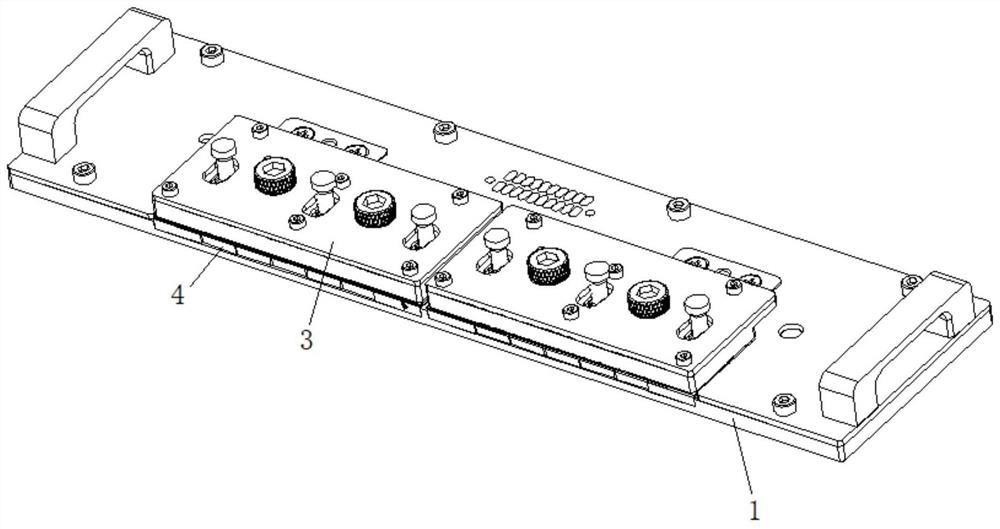

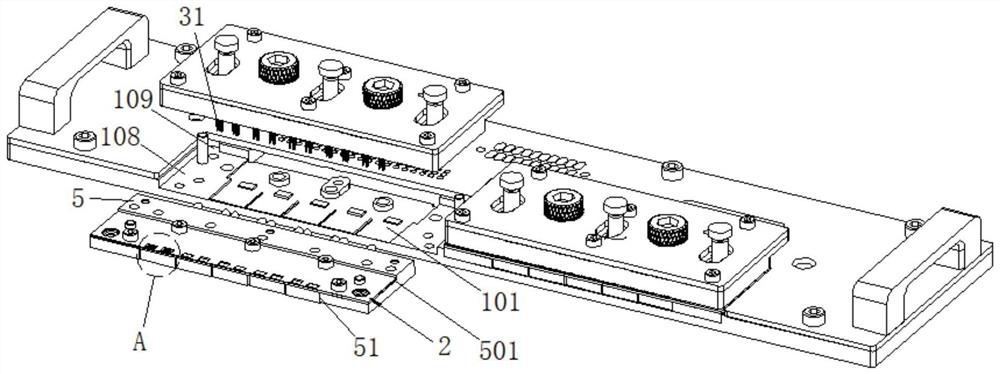

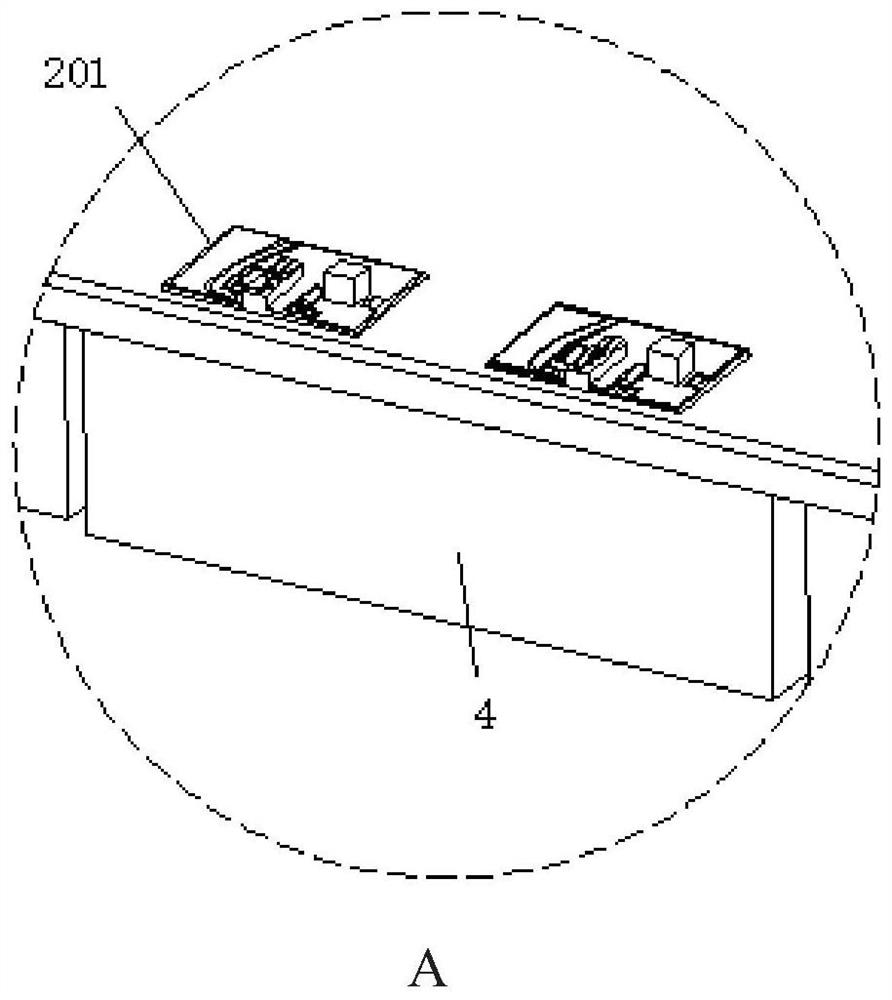

[0030] Embodiment 1: a kind of reliability test system for laser chips, with reference to the attached Figure 1-6 , including a substrate 1, a carrier 2 mounted on the substrate 1, and a first PCB3 mounted on the carrier 2, the carrier 2 has a chip slot 201 for chip embedding, and the first PCB3 has a The chip probe 31 corresponding to the chip slot 201, several TEC4s are installed between the substrate 1 and the carrier board 2, and the TEC4 is located directly below the chip slot 201, and a thermal insulation is installed between the substrate 1 and the first PCB3. A plate 5, which is provided with a heat-insulating groove 51 for TEC4 to be embedded in the heat-shielding plate 5;

[0031] The first PCB3 is installed on the heat shield 5, and a second PCB6 is installed on the substrate 1, and the second PCB6 has a connecting contact 61, a test contact 62 communicated with the connecting contact 61, a soldering contact 63 and the power supply contact 63 communicated with the...

Embodiment 2

[0037] Embodiment 2: a kind of reliability testing system for laser chips, with reference to the attached Figure 1-6 , including a substrate 1, a carrier 2 mounted on the substrate 1, and a first PCB3 mounted on the carrier 2, the carrier 2 has a chip slot 201 for chip embedding, and the first PCB3 has a The chip probe 31 corresponding to the chip slot 201, several TEC4s are installed between the substrate 1 and the carrier board 2, and the TEC4 is located directly below the chip slot 201, and a thermal insulation is installed between the substrate 1 and the first PCB3. A plate 5, which is provided with a heat-insulating groove 51 for TEC4 to be embedded in the heat-shielding plate 5;

[0038] The first PCB3 is installed on the heat shield 5, and a second PCB6 is installed on the substrate 1, and the second PCB6 has a connecting contact 61, a test contact 62 communicated with the connecting contact 61, a soldering contact 63 and the power supply contact 63 communicated with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More