Acceleration processing method for autonomously outputting NVME protocol command

A processing method and protocol command technology, applied in the direction of electrical digital data processing, input/output to record carrier, input/output process of data processing, etc., can solve the problem of increasing processing overhead and design difficulty, long-term occupation of CPU resources, and time delay Problems such as large consumption, to achieve the effect of improving CPU access efficiency, reducing the number of CPU operations, and low latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] The present embodiment discloses a method for speeding up processing of autonomously outputting NVME protocol commands, comprising the following steps:

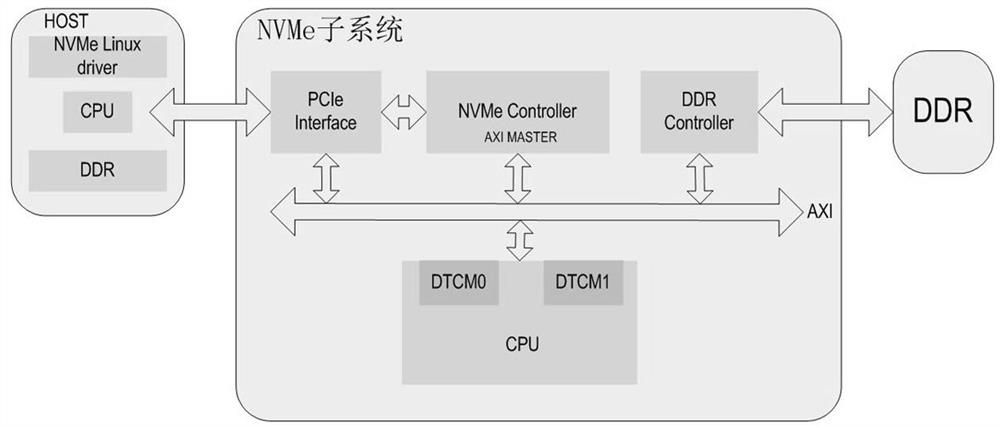

[0030] S01), such as figure 1 As shown, one or more data tightly coupled memory units DTCM (Data Tightly Coupled Memory) are integrated in the CPU of the NVME subsystem, and an AXI MASTER interface is added to the NVME controller. The AXIMASTER interface is connected to the AXI bus, and the address access space It is the DTCM address inside the CPU;

[0031] S02), the NVME controller writes the NVME command into the DTCM through the AXI MASTER interface, and the CPU core in the NVME subsystem directly accesses the DTCM;

[0032] S03), the NVME subsystem writes all the commands with the namespace ID i into the DTCM through the AXI MASTER interface according to the namespace ID i Among them, i=1,2,…,n:

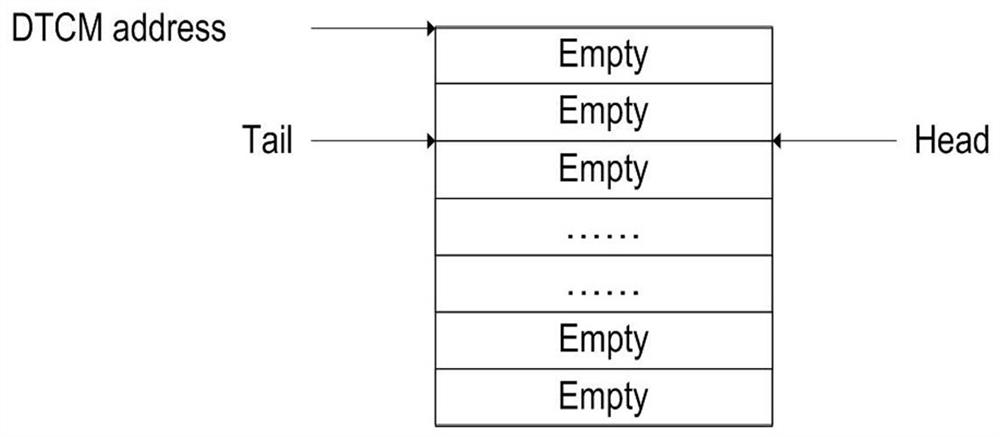

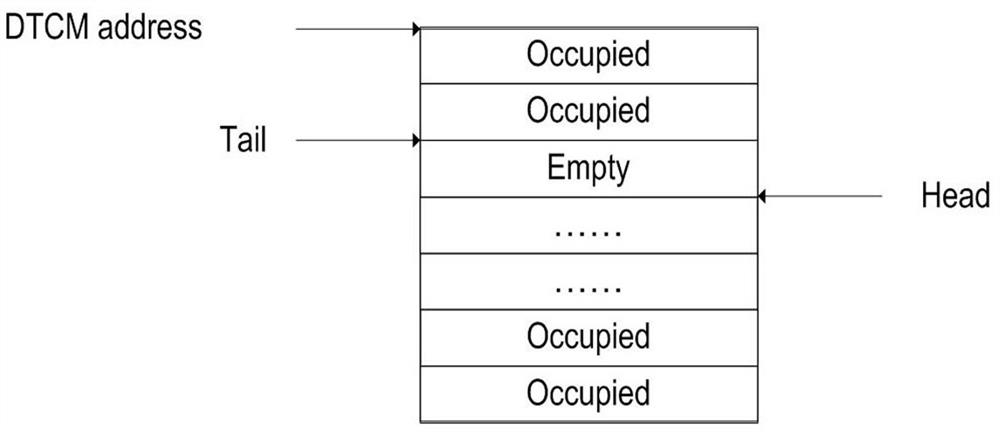

[0033] S04) Each DTCM is implemented in a queue mode, which is jointly maintained by the NVME controller and the CP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com