NVME protocol command acceleration processing system

A technology for processing system and protocol commands. It is applied in the storage field and can solve problems such as long-term occupation of CPU resources, failure to respond to management commands in a timely manner, and frequent operations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

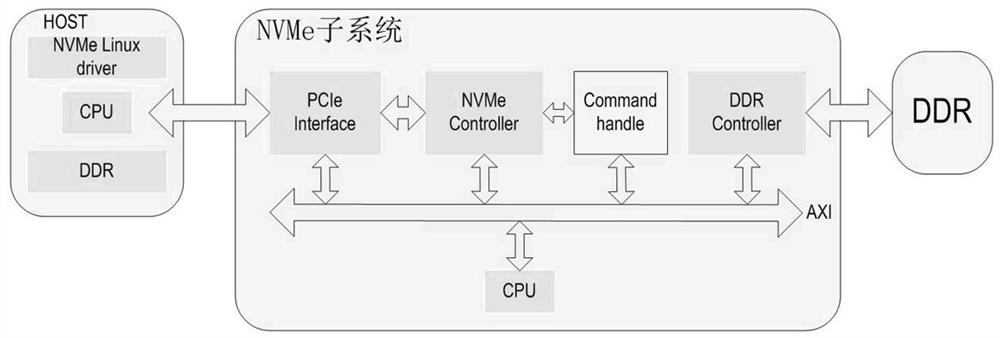

[0026] The present embodiment discloses a kind of NVME protocol command accelerated processing system, such as figure 1 As shown, including the NVME controller (NVME Controller), command processing module (Command handle) and CPU, the NVME controller (NVME Controller), command processing module (Command handle) and CPU are all set in the NVME subsystem. The NVME controller is connected to the host (HOST) through the PCIE interface, the host command is sent to the NVME controller through the PCIE interface, the NVME controller sends the host command to the command processing module through the RAM interface, and the internal CPU of the NVME subsystem accesses the command processing through the AXI bus commands in the module.

[0027] like figure 2 As shown, the command processing module includes a command storage SRAM and a bus protocol conversion module. The command storage SRAM is connected to the NVME controller through the RAM bus to receive host commands from the NVME co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More