Scheduling method and device for out-of-order execution queue in out-of-order processor

An out-of-order processor and execution queue technology, which is applied to machine execution devices, concurrent instruction execution, electrical digital data processing, etc. There are problems such as overflow to achieve the effect of saving area, improving processor performance, and low latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] Embodiments of the present invention will be described in detail below, and examples of the embodiments are illustrated in the drawings, in which the same or similar reference numerals represent the same or similar elements or elements having the same or similar functions. The embodiments described below are illustrative of the invention, and is intended to be construed as limiting the invention.

[0048] Described with reference to the accompanying drawings according to embodiments of the present invention, the processor scrambled embodiment proposed in order execution queue scheduling method and apparatus will be first described with reference to the accompanying drawings scrambled processor embodiment proposed order execution queue according to the embodiment of the present invention. scheduling method.

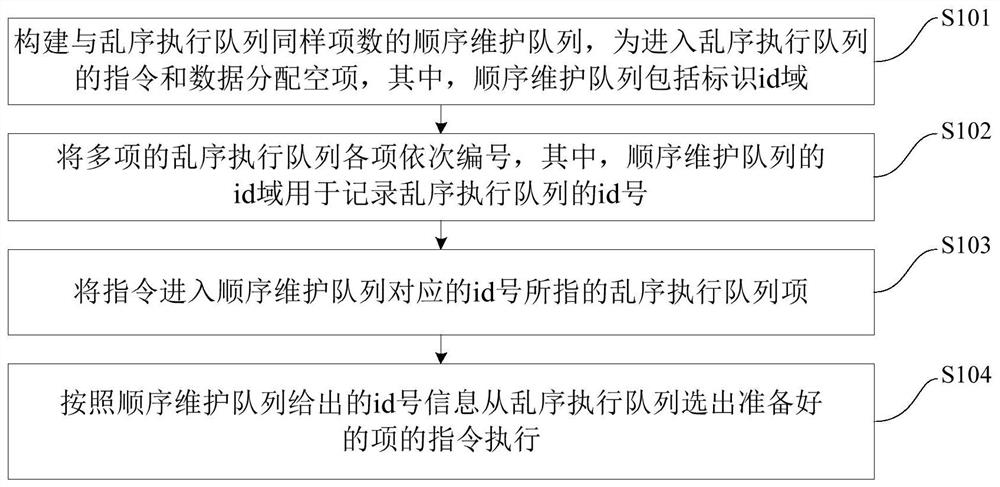

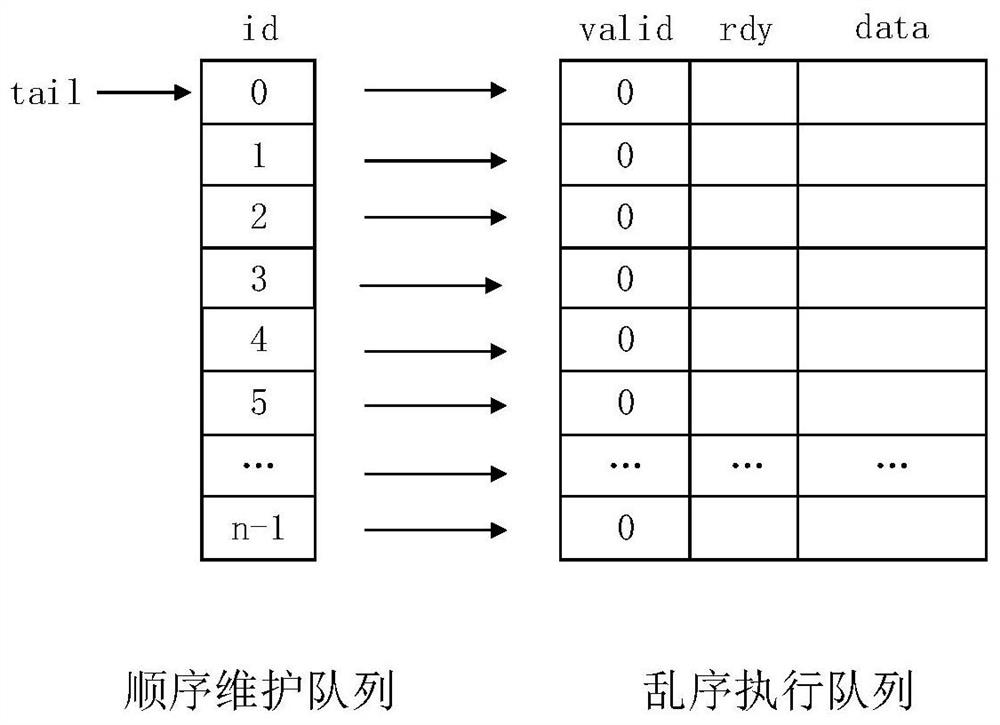

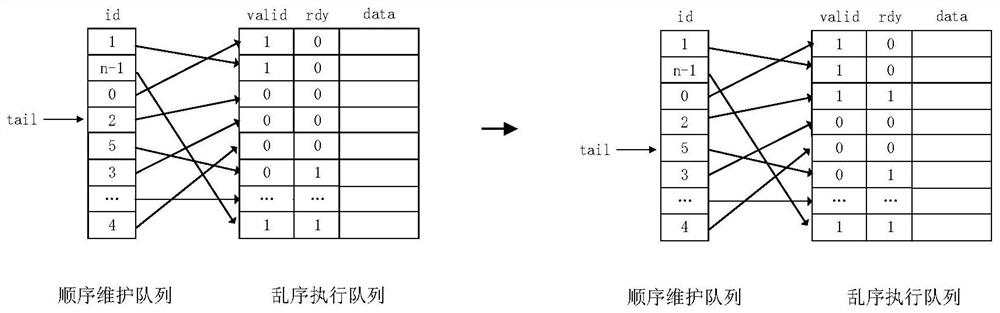

[0049] in particular, figure 1 Flow diagram of an embodiment of a processor scrambled in the provided order execution queue scheduling method of the embodiment of the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More